Изобретение относится к преобразователям аналог-код с промежуточным преобразованием аналоговой величины во временной интервал с помощью устройства интегрирующего типа с импульсной обратной связью.

Известный нреобразователь аналоговой величины в число импульсов имеет интегратор постоянного тока, охваченный двумя цепями обратных связей - через конденсатор С с выхода на вход усилителя постоянного тока и импульсную обратную связь, соединяющую вход интегратора через ключ с выходом эталонного источника постоянного тока. Выход интегратора связан с нуль-органом и через него - с триггером. Другой (установочный) вход триггера через делитель частоты и формирователь импульсов связан с генератором эталонной частоты. Через эту цепь производится тактирование всего устройства. Обычно частотный делитель, применяемый для этих целей, представляет сложное устройство, ибо должен обеспечить значительный коэффициент деления (в известном устройстве он шестикаскадный с коэффициентом деления 200000). Триггер соединен с ключом и схемой совпадения, пропускающей на вход счетчика за период количество импульсов, пропорциональное аналоговой величине.

входом Счетчика, выход старшего разряда которого подключен к установочному входу спускового устройства. Выход нуль-органа подключен через схему несовпадения, ко втором)

входу которой подключен генератор эталон ной частоты, к схемам совпадения, включен ных на выходе разрядов счетчика.

ТакОе выполнение преобразователя позволяет упростить устройство и повысить точность преобразования за счет исключения многокаскадного делителя частоты с формирователем тактового импульса и потенциально-управляемой схемы совпадений - частотного эталонного ключа.

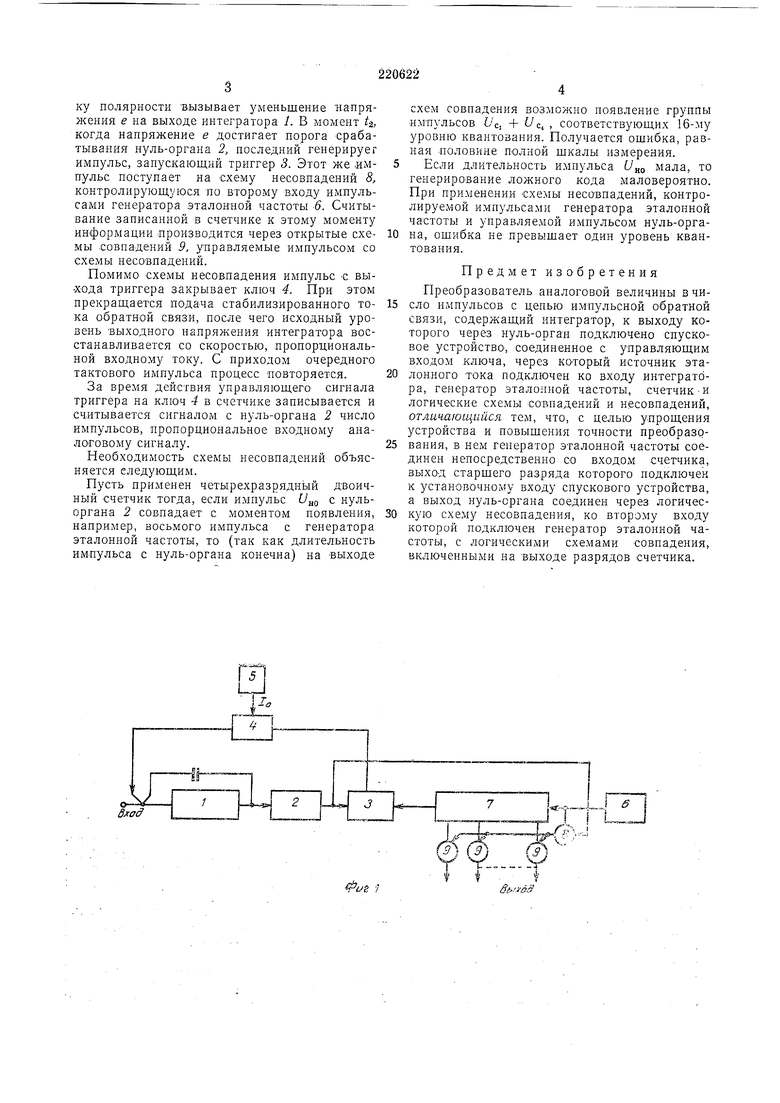

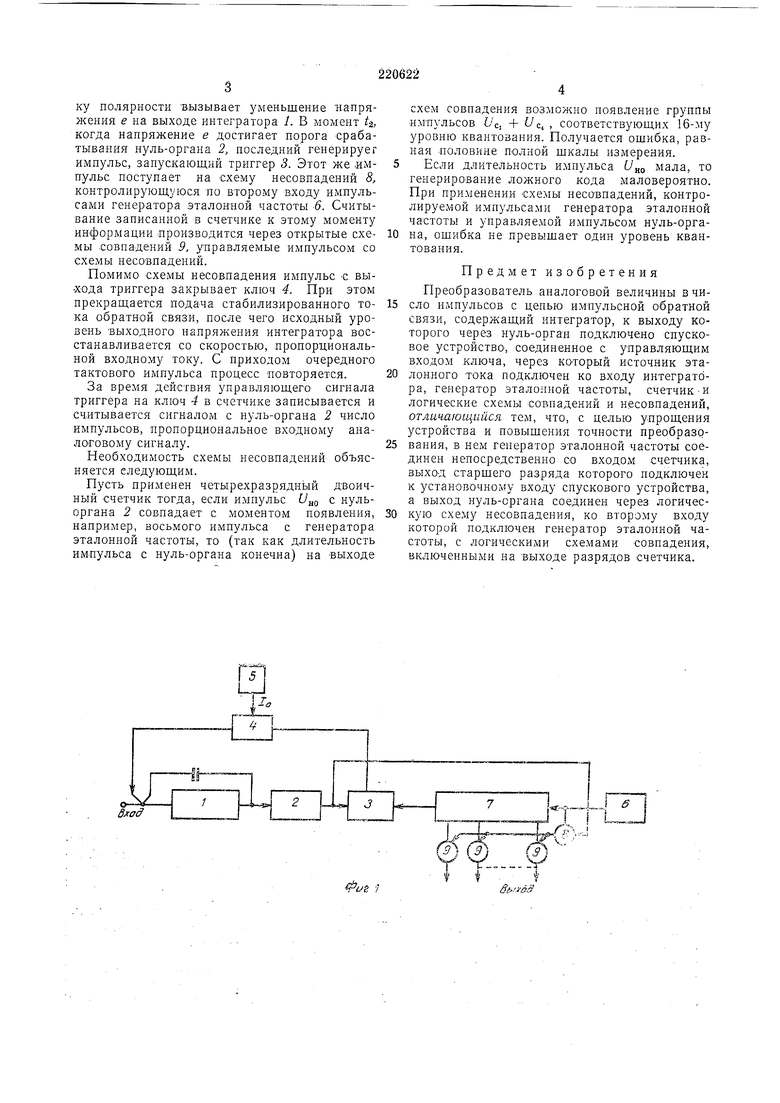

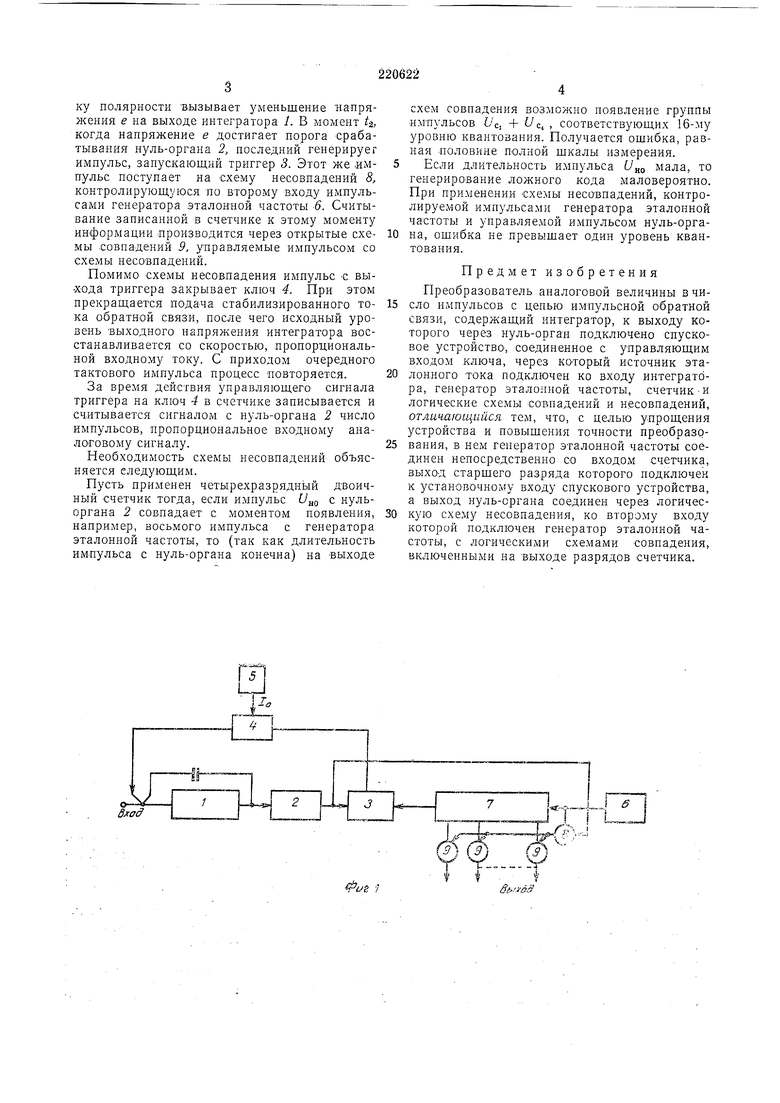

На фиг. 1 показана блок-схема описываемого устройства; на фиг. 2 - временные диаграммы напряжений в различных точках устройства. Устройство содержит интегратор / посто-янного тока, нуль-орган 2, триггер 3, ключ 4, источник 5 эталонного тока, генератор эталонной частоты 6, счетчик 7, схему несовпадений 8 и схемы совпадений 9. Устройство работает следующим образом.

Генератор эталонной частоты 6 непрерывно заполняет счетчик 7. Импульс переполнения счетчика периодически устанавливает триггер 3 в исходное состояние. При этом импульсом с выхода триггера открывается ключ 4. Стаку полярности вызывает уменьшение напряжения е на выходе интегратора I. В момент i-г, когда напряжение е достигает порога срабатывания нуль-органа 2, последний генерирует импульс, запускающий триггер 5. Этот же импульс поступает на схему несовпадений 5, контролирующуюся по второму входу импульсами генератора эталонной частоты 6. Считывание записанной в счетчике к этому моменту информации производится через открытые схемы .совпадений 9, управляемые импульсом со схемы несовпадений.

Помимо схемы несовпадения импульс с выхода триггера закрывает ключ 4. При этом прекращается подача стабилизированного тока обратной связи, после чего исходный уровень выходного напряжения интегратора восстанавливается со скоростью, пропорциональной входному току. С приходом очередного тактового импульса процесс повторяется.

За время действия управляющего сигнала триггера на ключ 4 в счетчике записывается и считывается сигналом с нуль-органа 2 число импульсов, пропорциональное входному аналоговому сигналу.

Необходимость схемы несовпадений объясняется следующим.

Пусть применен четырехразрядный двоичный счетчик тогда, если импульс /7„о с нульоргана 2 совпадает с моментом появления, например, восьмого импульса с генератора эталонной частоты, то (так как длительность импульса с нуль-органа конечна) на выходе

схем совпадения возможно появление группы импульсов LCI + , соответствующих 16-му уровню квантования. Получается ошибка, равная половине полной шкалы измерения. Если длительность импульса 6„о мала, то генерирование ложного кода маловероятно. При применении схемы несовпадений, контролируемой импульсами генератора эталонной частоты и управляемой импульсом нуль-органа, ошибка не превышает один уровень квантования.

Предмет изобретения

Преобразователь аналоговой величины вчиело импульсов с цепью импульсной обратной связи, содержащий интегратор, к выходу которого через нуль-орган подключено спусковое устройство, соединенное с управляющим входом ключа, через который источник эталонного тока подключен ко входу интегратора, генератор эталонной частоты, счетчик-и логические схемы совпадений и несовпадений, отличающийся тем, что, с целью упрощения устройства и повышения точности преобразования, в нем генератор эталонной частоты соединен непосредственно со входом счетчика, выход старшего разряда которого подключен к установочному входу спускового устройства, а выход нуль-органа соединен через логическую схел1у несовпадения, ко второму входу которой подключен генератор эталонной частоты, с логическими схемами совпадения, включенными на выходе разрядов счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель температуры | 1981 |

|

SU974145A1 |

| Пульсотахометр | 1990 |

|

SU1776384A1 |

| Измеритель энергии искры | 1982 |

|

SU1078347A1 |

| Цифровой измеритель параметров катушек индуктивности и конденсаторов | 1975 |

|

SU599232A1 |

| Устройство для измерения постоянной времени | 1987 |

|

SU1504626A1 |

| ЦИФРОВОЙ ИНТЕГРИРУЮЩИЙ ВОЛЬТАМПЕРМЕТР | 1972 |

|

SU347909A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Цифровой измеритель относительной разности скоростей | 1977 |

|

SU717657A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Цифровой измеритель температуры | 1986 |

|

SU1364910A1 |

Ыно

и se /fpamopo

i I I 1 1

U,

щ.ш

и.

U.

W////W/A

y////m/A

Uc,

V//////////.

Даты

1968-01-01—Публикация