Настоящее изобретение относится к области вычислительной техники.

Известны устройства управления цифросинтезирующим индикатором, содержащие входное устройство, устройство управления, запоминающее устройство, дешифратор, устройство Питания цифрового индикатора, панель управления, цифровой индикатор.

Указанное устройство обеспечивает индикацию только одного числа, набранного на панели управления. Чтобы индицировать другое число, необходимо с помощью аппаратуры панели управления снять индикацию первого числа и задать индикацию нового числа. Для передачи .произвольного ряда чисел необходимо вьшолнять последовательные переключения, выдерживая требуемую длительность индикации каждого числа. При повторении индикации переключения необходимо повторять в том же порядке.

Целью изобретения является упрощение управления цифросинтезирующим индикатором пр.и передаче произвольного ряда чисел, заключающееся в обеспечении автоматической последовательной индикации каждого числа в течение заданного времени, при одновременном наборе этих чисел на панели управления.

соединенные двоично-десятичный счетчик, дешифратор кода счетчика, числовой дешифратор, блок формирования длительности индикации. По входу распределитель через схему 5 запрета подключен к генератору импульсов, по первому выходу через панель управления подключен ко входу блока формирования длительности индикации, а по второму выходу через выходной блок, блок формирования длительности индикации подключен к схеме запрета.

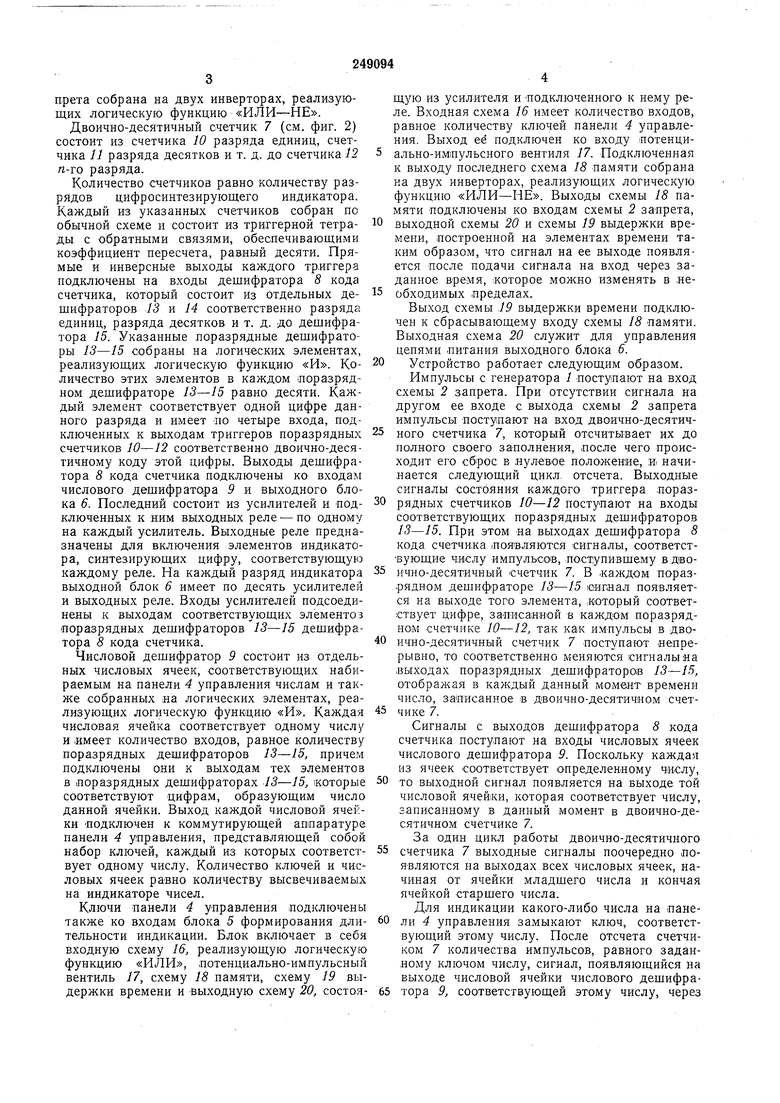

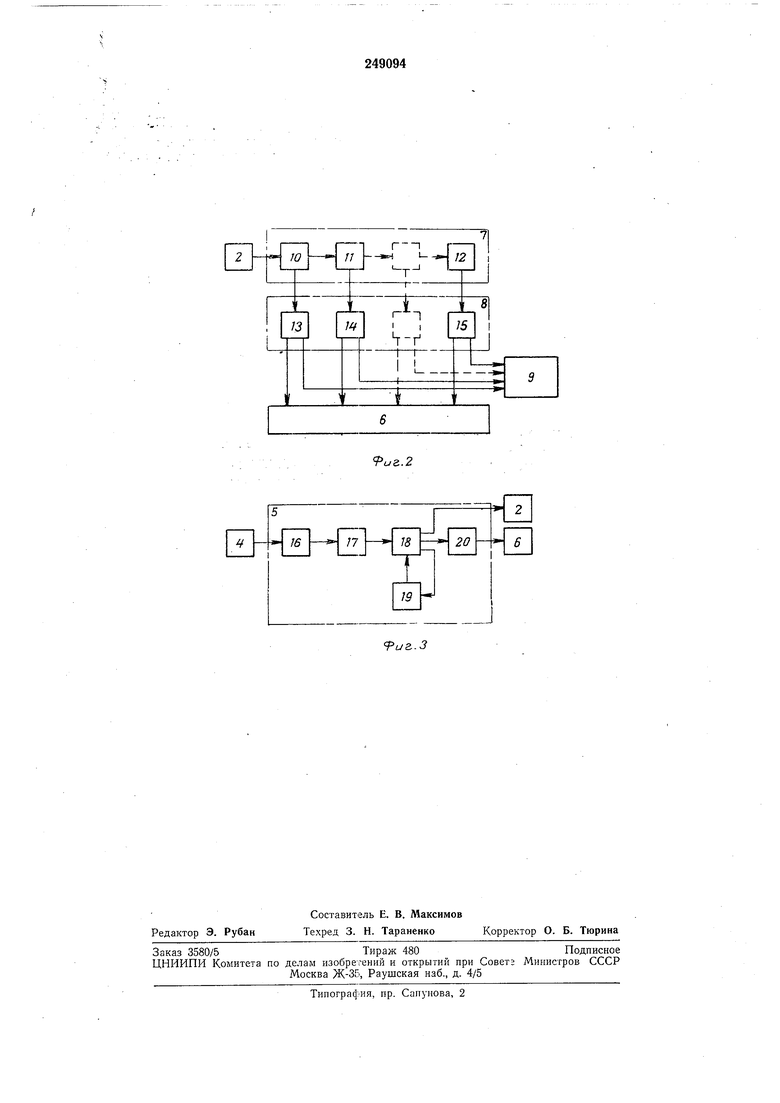

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - структурная схема распредели5 теля; на фиг. 3 - структурная схема блока формирования длительности индикации.

Устройство содержит генератор / импульсов, схему 2 запрета, распределитель 3, панели 4 управления с коммутирующей аппаратурой, блок 5 формирования длительности индикации и выходной блок 6. Распределитель 3 содерлсит двоично-десятичный счетчик 7, дешифратор 8 кода счетчика и числовой дешифратор 9.

5 В качестве генератора / импульсов использован мультивибратор (или блокинг-генератор) с выходной частотой, величина которой (в герцах) несколько выще величины числовой емкости цифросинтезирующего индикатора, прета собрана на двух инверторах, реализующих логическую функцию «ИЛИ-НЕ. Двоично-десятичный счетчик 7 (см. фиг. 2) состоит из счетчика 10 разряда единиц, счетчика // разряда десятков и т. д. до счетчика 12 п-то разряда. Количество счетчиков равно количеству разрядов цифросинтезирующего индикатора. Каждый из указанных счетчиков собран по обычной схевде и состоит из триггерной тетрады с обратными связями, обеспечивающими коэффициент пересчета, равный десяти. Прямые и инверсные выходы каждого тр.иггера подключены на входы дешифратора 8 кода счетчика, который состоит из отдельных дешифраторов 13 и 14 соответственно разряда единиц, разряда десятков и т. д. до дешифратора 15. Указанные поразрядные дешифраторы 13-15 собраны на логических элементах, реализующих логическую функцию «И. Количество этих элементов в каждом поразрядном дешифраторе 13-15 равно десяти. Каждый элемент соответствует одной цифре данного разряда и имеет по четыре входа, подключенных к выходам триггеров поразрядных счетчиков 10-12 соответственно двоично-десятичному коду этой цифры. Выходы дешифратора 8 кода счетчика подключены ко входам числового дешифратора 9 и выходного блока 6. Последний состоит из усилителей и подключенных к ним выходных реле - по одному на каждый усилитель. Выходные реле предназначены для включения элементов индикатора, синтезирующих цифру, соответствующую каждому реле. На каждый разряд индикатора выходной блок 6 имеет по десять усилителей и выходных реле. Входы усилителей подсоединены к выходам соответствующих элементоз поразрядных дешифраторов 13-15 дещифратора 8 кода счетчика. Числовой дешифратор 9 состоит из отдельных числовых ячеек, соответствующих набираемым на панели 4 управления числам и также собранных на логических элементах, реализующих логическую функцию «И. Каждая числовая ячейка соответствует одному числу и .имеет количество входов, равное количеству поразрядных дешифраторов 13-15, причем подключены они к выходам тех элементов в (Поразрядных дешифраторах .13-15, которые соответствуют цифрам, образующим число данной ячейки. Выход каждой числовой ячейки Подключен к коммутирующей аппаратуре нанели 4 управления, представляющей собой набор ключей, каждый из которых соответствует одному числу. Количество ключей и числовых ячеек равно количеству высвечиваемых на индикаторе чисел. Ключи панели 4 управления подключены также ко входам блока 5 формирования длительности индикации. Блок включает в себя входную схему 16, реализующую логическую функцию «ИЛИ, потенциально-импульсный вентиль 17, схему 18 памяти, схему 19 выщую из усилителя и -подключенного к нему реле. Входная схема 16 имеет количество входов, равное количеству ключей панели 4 управления. Выход её подключен ко входу потенциально-импульсного вентиля 17. Подключенная к выходу последнего схема 18 памяти собрана на двух инверторах, реализующих логическую функцию «ИЛИ-НЕ. Выходы схемы 18 памяти подключены ко входам схемы 2 запрета, выходной схемы 20 и схемы 19 выдержки времени, построенной на элементах времени таким образом, что сигнал на ее выходе появляется после подачи сигнала на вход через заданное время, .которое можно изменять в необходимых пределах. Выход схемы ,19 выдержки времени подключен к сбрасывающему входу схемы 18 памяти. Выходная схема 20 служит для управления цепями питания выходного блока 6. Устройство работает следующим образом. Импульсы с генератора 1 поступают на вход схемы 2 запрета. При отсутствии сигнала на другом ее входе с выхода схемы 2 запрета импульсы поступают на вход двоично-десятичного счетчика 7, который отсчитывает их до полного своего заполнения, после чего происходит его сброс в нулевое положение, и начинается следующий цикл, отсчета. Выходные сигналы состояния каждого триггера поразрядных счетчиков 10-12 поступают на входы соответствующих поразрядных дешифраторов 13-15. При этом на выходах дешифратора 8 кода счетчи;ка появляются сигналы, соответствующие числу импульсов, поступившему в двоично-десятичный счетчик 7. В каждом поразрядном дешифраторе 13-15 юигнал появляется на выходе того элемента, .который соответствует цифре, записанной в каждом поразрядном счетчике 10-12, так ка.к импульсы в двоично-десятичный счетчик 7 поступают непрерывно, то соответственно меняются .сигналы на выходах поразрядных дешифраторов 13-15, отображая в каждый данный момент времени число, записанное .в двоично-десятичном счетчике 7. Сигналы с выходов дешифратора 8 кода счетчика поступают на входы числовых ячеек числового дешифратора 9. Поскольку каждая из ячеек соответствует .определеН|Ному числу, то выходной сигнал появляется на выходе той числовой ячейки, которая соответствует числу, записанному в данный момент в двоично-десятичном счетчике 7. За один цикл работы двоично-десятичного счетчика 7 выходные сигналы поочередно появляются на выходах всех числовых ячеек, начиная от ячейки младшего числа и кончая ячейкой старшего числа. Для индикации какого-либо числа на панели 4 управления замыкают ключ, соответствующий этому числу. После отсчета счетчиком 7 количества импульсов, равного заданному ключом числу, сигнал, появляющийся на выходе числовой ячейки числового дешифразамкнутый ключ поступает на входную схему 16 блока формирования длительности индикации 5.

Потенциальный сигнал с выхода входной схемы 16 поступает на вход потенциально-импульсного вентиля 17, который преобразует его В импульс, включающий схему 18 .памяти.

Это преобразование необходимо для исключения Повторного срабатывания блока 5 внутри одного цикла отсчета двоично-десятичного счетчика 7 от одного и того же сигнала, т. е. для обеспечения обегания всех числовых ячеек числового дешифратора 9.

Сигнал с выхода схемы 18 памяти поступает на схему 2 залрета, в результате чего прекращается поступление имлульсов в двоично-десятичный счетчик 7. Кроме того, сигнал поступает на входы схемы 19 выдержки времени и выходной схемы 20. Последняя включает цепи питания выходного блока 6, в котором срабатывают выходные реле, подключенные к выходам элементов поразрядных дешифраторов 13-15, соответствующих цифрам, образующим заданное число.

Выходные реле выходного блока 6 включают на цифросинтезирующем индикаторе необходимые сочетания элементов, синтезирующих цифры заданного числа. С окончанием выдержки времени появляется выходной сигнал на выходе схемы 19 выдержки времени, который отключает схему 18 памяти, что вызывает исчезновение сигнала на входе схемы 2 запрега. После этого импульсы вновь начинают поступать в двоично-десятичный счетчик 7.

Изменение его состояния вызывает исчезновение в поразрядных дешифраторах 13-15 выходных сигналов, соответствующих заданному числу, в результате чего отпадают выходные реле выходного блока 6, прекращая индикацию этого числа. Исчезает также выходной сигнал числовой ячейки числового дешифратора 9, соответствующей заданному числу. Кроме того, отключение выходной схемы 20 блока 5 формирования длительности индикации вызывает отключение выходного блока 6.

Двоично-десятичный счетчик 7 отсчитывает иМПульсы до .полного заполнения, после чего происходит сброс его, и в новом цикле отсчета описанный процесс повторяется. Таким образом, если для индикации выбрано одно число, то в каждом цикле отсчета индикатор высвечивает его изображение на время, определяемое схемой 19 выдержки времени. Если для индикации выбрано несколько чисел, т. е. замкнуты соответствующие им ключи на панели 4 управления, то внутри одного цикла отсчета двоично-десятичного счетчика 7 происходит автоматическая последовательная их индикация, начиная от младшего выбранного числа и кончая старшим, по мере отсчета соответствуюшего количества импульсов. В следующем цикле отсчета индикация выбранных чисел повторяется. Для индикации можно избирать любое количество чисел в пределах, определяемых разрядностью индикатора и количеством ключей, установленных на панели 4 управления, причем в процессе индикации можно подключать или отключать любое число.

Предмет изобретения

Устройство для управления цифросинтезирующим индикатором, содержащее дешифратор, генератор импульсов, выходной блок, панель управления, отличающееся тем, что, с целью упрощения управления индикатором при передаче произвольного ряда чисел, оно содержит схему запрета, распределитель сигналов, состоящий из последовательно соединенных двоично-десятичного счетчика, дешифратора кода счетчика и числового дешифратора, блок формирования длительности индикации, причем по входу распределитель через схему запрета подключен к генератору импульсов, по первому выходу через панель управления подключен ко входу блока формирования длительности индикации, а по второму выходу через выходной блок, блок формирования длительности индикации подключен

к схеме запрета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления цифросинтезирующим индикатором | 1974 |

|

SU531176A2 |

| БЫСТРОДЕЙСТВУЮЩЕЕ ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ РАЗНОСТИ СКОРОСТЕЙ СЕКЦИЙ АГРЕГАТОВ | 1973 |

|

SU370529A1 |

| Устройство для индикации | 1977 |

|

SU822243A1 |

| Электронная игра | 1988 |

|

SU1674888A1 |

| Устройство для индикации | 1979 |

|

SU851453A1 |

| УСТРОЙСТВО для РЕГИСТРАЦИИ ИМПУЛЬСНЫХ СИГНАЛОВ | 1972 |

|

SU334478A1 |

| Устройство для индикации | 1980 |

|

SU877604A1 |

| Устройство управления электронной игрой | 1986 |

|

SU1437051A1 |

| Тренажер оператора систем управления | 1990 |

|

SU1711221A1 |

| ПРОГРАММНОЕ УСТРОЙСТВО | 1973 |

|

SU406185A1 |

иг.З

Авторы

Даты

1969-01-01—Публикация