Изобретение отиосйтся к счетно-решающим устройствам и может найти применение, когда нужно определить весьма малые скорости изменения сигналов, напримф в металлургичеокой, химической иромышлениости (|ОптИ|Мизаторы, экстремальные регуляторы и ор.).

устройство для получения производной в диск,ретных системах, содержащее гереобразователь «амплитуда сигнала - частота, схемы коммутации, .включающ.ие логические элементы с функцией «ИЛИ - НЕ, Д|ва триггера и генератор; счетчи1ки импульсов, работающие на принципе использования эффекта ступенчатого леремагничивания материала с прямоугольной петлей гистерезиса; схему выделения разиости, включающую девять элементов с функцией «ИЛИ - НЕ.

Такое устройство работает лишь в диапазоне частот входных ситналов, в котором обеспечивается неравенство:

k,(k,-k),

где kfnan - количество импульсов, которое может вместить (счетчик;

k - меньшее количество импульсов, заиисанное в каком-либо счетчике; 3 - количество импульсов, поступившее на счетчики в третьем такте. При достаточно малых скоростях входных сигналов это неравенство не соблюдается.

Кроме того, с изменением температуры изменяется емкость счетчиков, работающих на принципе использования эффекта ступенчатого перемагничивания материала с прямоугольной петлей гнстерез.иса, что снижает точность дифференцирования.

Целью предлагаемого изобретения является расширение диапазона |Скорастей изменения входных .сигналов и повышение точности устройства.

Это достигается тем, что устройство содерл ит реверсивный счетчик импульсов, входы которого связаны с выходами схемы коммутации, а выходы подключены к нуль-индикатору.

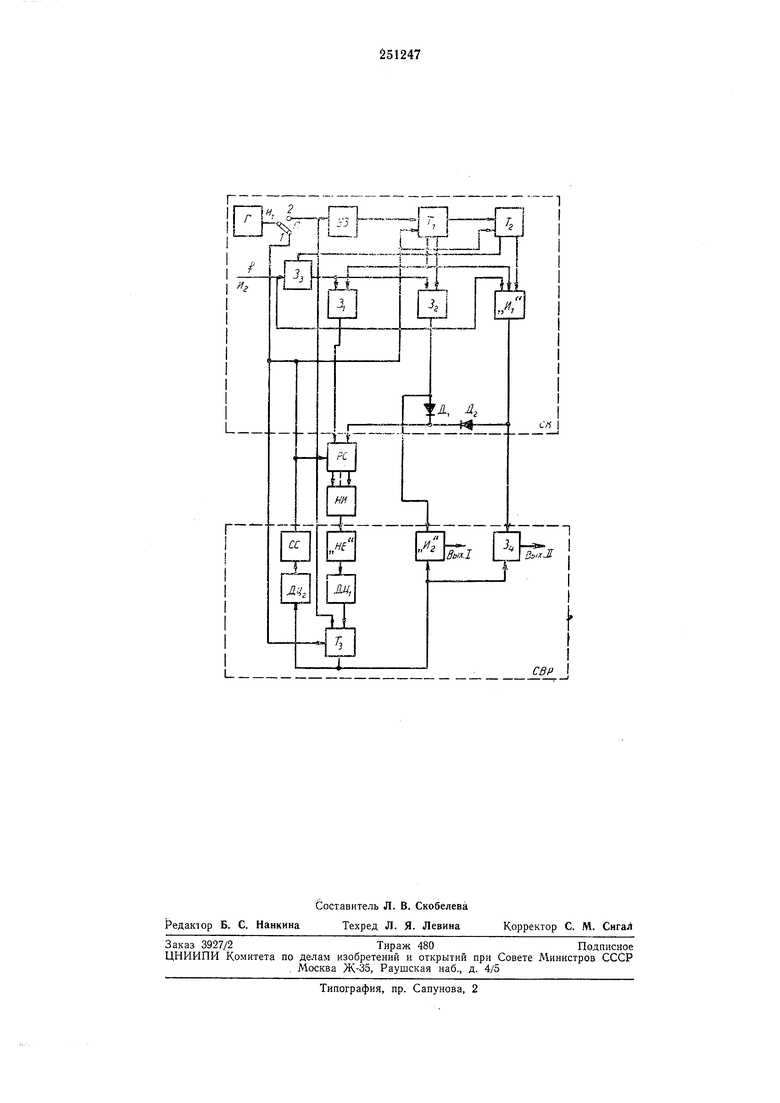

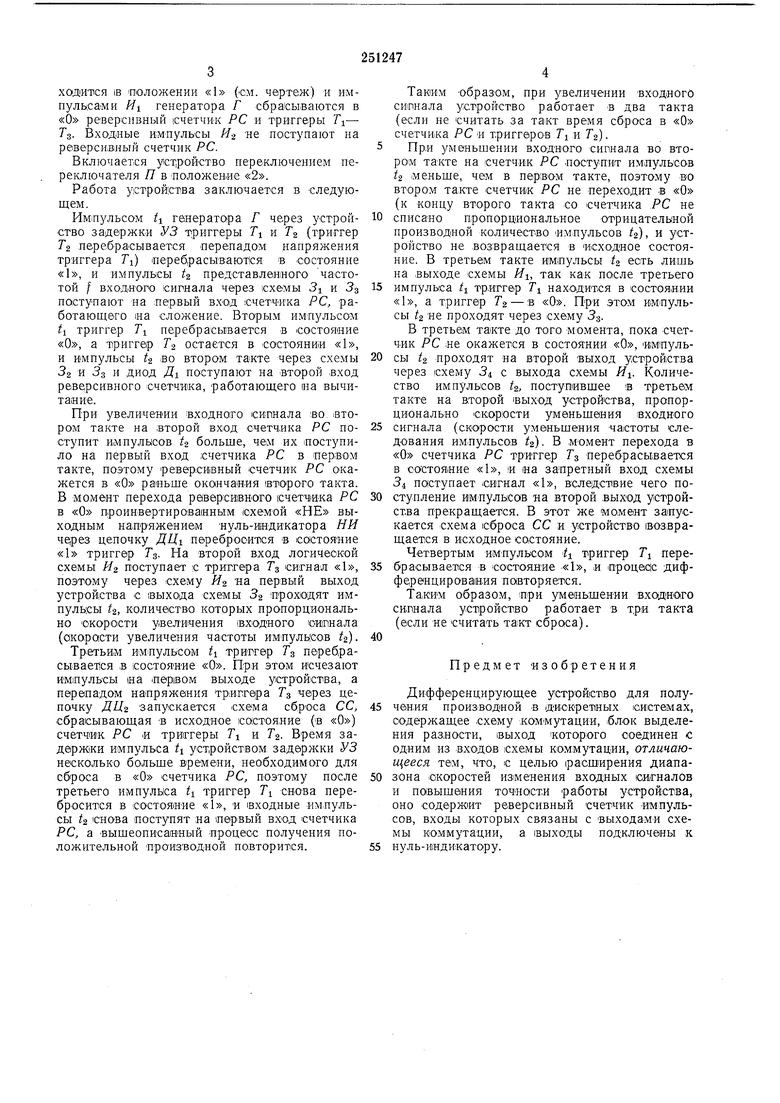

Сущность изобретавия поясняется блок-схемой, изображенной на чертеже.

Устройство состоит из схемы коммутации СК, включающей генератор тактовых импульсов Г, устройство задержки УЗ, два триггера TI и Г.2, логические схемы «Запрет , логическую схему «И И, два диода Mi и Да и переключатель П, реверсивный счетчик PC с нуль-индикатором НИ (логическая схема «И) и схемы выделения разности СВР, включающей логичес1сую схему «И Я, схе.му «Запрет 3, схему сброса СС, две дифференцируюЩИе цепочки ДЦ и ДЦз и триггер 7з. В тгсходном состоянии -переключатель Я находится IB положении «1 (-см. чертеж) и импульсами И генератора Г сбрасываются в «О реверсивный счетчик PC и триггеры Tj- Гд. Входные импульсы Яз не поступают на реверсивный счетчик PC.

Включается устройство переключением переключателя Я в Положение «2.

Работа устройства заключается в следующем.

Им1пульсом /1 генератора Г через устройство задержки УЗ триггеры TI и Т (триггер TZ перебрасывается перепадом напряжения триггера Tj) перебрасываются в состояние «1, и импульсы tz представленного частотой / входного сигнала через схемы 3 и 3 поступают на первый вход счетчика PC, работающего 1на сложение. Вторым и импульсом 1 триггер TI перебрасывается в состояние «О, а триггер Го остается в состоянии «1, и и мпульсы t-2 iBo втором такте через схемы 32 и Зз и диод Дх поступают на второй вход реверсивного счетчи1ка, работающего на вычитание.

При увеличении входного сигнала во, втором такте на второй вход счетчйка PC поступит импульсов tz больше, че.м их поступило на первый вход счетчика PC в первом такте, поэтому реверсивный счетчик PC окажется в «О раиьше окончания второго такта. В момент перехода раверсивного счетчйка PC в «О проинвертированным (Схемой «НЕ выходным напряжением нуль-вндккатора ЯЯ че|рез цепочку ДЯх перебросится в состояние «1 триггер TZ- На второй вход логической схемы HZ поступает с триггера Т сигнал «1, поэтому через схему Яа на первый выход устройства с выхода схемы 3z проходят импульсы tz, количество которых пропорционально скорости увеличения входного сигнала (скорости увеличения частоты импульсов 2)

Тр етьим импульсом t триггер Гз перебрасывает1ся в состояние «О. При этом исчезают импульсы на nepiBOM выходе устройства, а перепадом напряжения тригге)ра Гз через цепочку ДЯ2 запускается схема сброса СС, сбрасывающая В исходное состояние (в «О) счетчик PC и триггеры Tj и Т. Время задврж1ки импульса t устройством задержки УЗ несколько больше времени, необходимого для сброса в «О счетчика PC, поэтому после третьего импульса t триггер TI снова перебросится в состояние «1, и входные импульсы tz снова поступят на первый вход счетчика PC, а вышеописанный процесс получения положительной производной повторится.

Таким образом, при величении входного сипнала устройство работает в два такта (если не считать за таКт время сброса в «О счетчика PC -и триггеров Tj и TZ. При уменьшении входного сипнала во втоPOIM такте на счетчик PC поступит импульсов tz меньше, чем в первом такте, поэтому во втором такте счетчик PC не переходит в «О (к концу второго такта со счетчика PC не

списано пропорциональное отрицательной производной количество импульсов tz), и устройство не возвращается в И1сходное состояние. В третьем такте импульсы 4 есть лишь на выходе схемы И, так как после третьего

импулыса t триггер Т находится в состоянии «1, а триггер Т - в «О. При этом И1М1пульсы tz не проходят через схему Зз.

В третьем такте до того момента, пока счетчик PC не окажется в состоянии «О, И1М1пульсы tz проходят на второй выход устройства через схему 34 с выхода схемы И. Количество импульсов tz, поступивщее в третьем такте на второй выход устройства, пропорционально скорости уменьшения входного

сигнала (скорости уменьшения частоты следования импульсов tz). В момент перехода в «О счетчика PC триггер Гз перебрасывается в состояние «1, и на запретный вход схемы 34 поступает сигнал «1, вследствие чего поотупление импульсов на второй выход устройства прекращается. В этот же момент запускается схема Сброса СС и устройство 1возвращается в исходное состояние. Четвертым импульсом i триггер Т перебрасывается в состояние .«1, и процеас дифференцирования повторяется.

Таким образом, при уменьшении входного сипнала устройство работает в три такта (если не считать такт сброса).

Предмет изобретения

Дифференцирующее устройство для получения производной в дискретных системах, содержащее схему коммутации, блок выделения разности, выход которого соединен с одним из входов Схемы коммутации, отличающееся тем, что, с целью (расширения диапазона скоростей изменения входных сигналов и повышения точности работы устройства, оно содерл 1ит реверсивный счетчик импульсов, входы которых связаны с выходами схемы коммутации, а выходы подключены к нуль-индикатору.

Даты

1969-01-01—Публикация