Изобретение относится к радиотехнике и может быть использовано в электронных установках (счетчиках), предназначенных для преобразования временных интер1вало1в в числа двоичною кода, в частности для преобразования информации о дальности, -получаемой от радиолокационных станций.

Известен .преобразователь временных интервалов в числа двоичного кода, содержащий триггеры, вентили, линию задерж1ки, электронный счетчик грубого отсчета. С выхода такого преобразователя нельзя снять единое двоичное число с уменьшенной вдвое дискретностью отсчета дальности.

С целью получения единых чисел двоичного кода с уменьшенной вдвое дискретностью отсчета лри пониженной частоте следования счетных имлульсав, в предлагаемом преОбразователе в состав младшего разряда включен дополнительный каскад на логических элементах «И и «ИЛП, соединенный по цепям управления с выходами четырех плеч счетных триггеров равного быстродействия. Один из триггеров одновременно выиюлняет функцию пересчета сдвинутых по фазе на 180° счетных имлульсов .и служит iB качестве второго разряда -преобразователя.

Преобразователь содержит счетные триггеры / И 2 (электронный счетчик грубого отсчета), два вентиля 3 и 4, линию задерлски 5, триггер 6 управления и дополнительный каскад на логических схемах «П 7 и S и «ПЛИ 9.

Оба входа схем «И соединены с выходами попарно противоположных плеч триггеров / и 2 равного быстродействия. Выходы схем «PI

через схему «ИЛИ соединены с шиной 10 младшего разряда преобразователя. Выход правого плеча триггера 2 соединен с шиной 11 его -второго разряда. Снимаемое с этих шин двоичное число с уменьшенной вдвое дискретностью отсчета дальности в частном случае

может быть передано к фиксатору дальности

арифметического устройства для дальнейшей

математической обработки.

Поступающие на вход, J2 счетные имоульсы

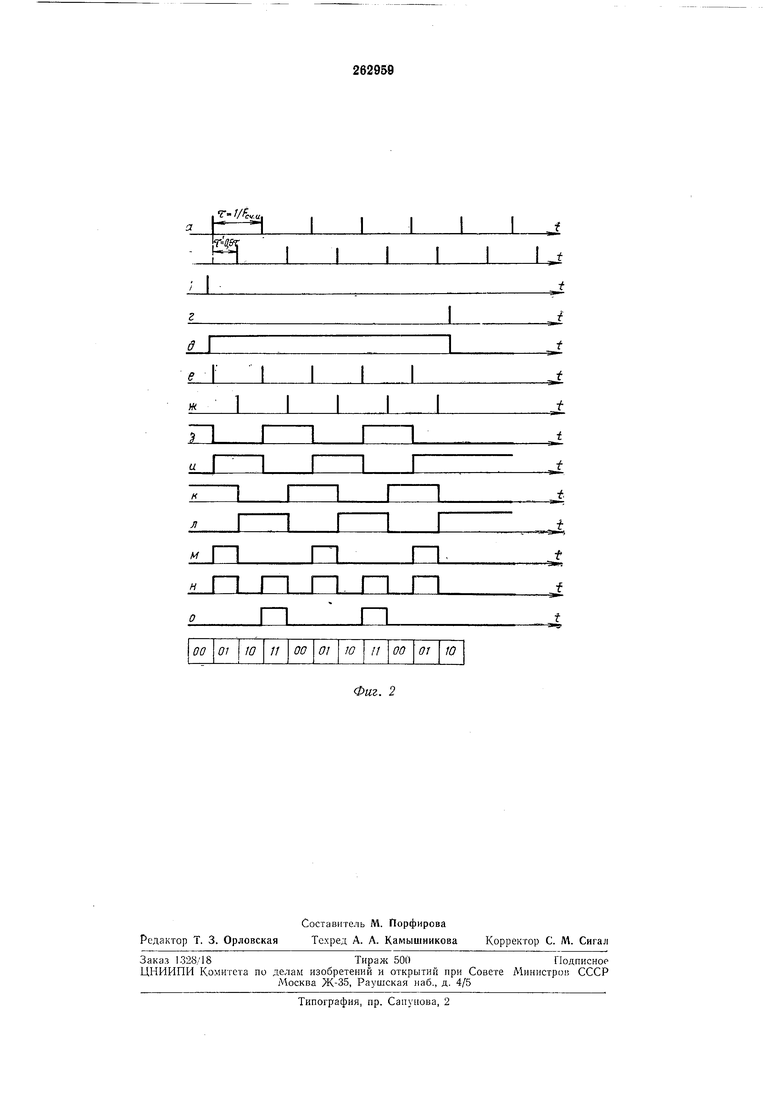

(эпюра а) с периодом следования т 1//сч.и (сч.и -частота следования счетных имлульсов) подводятся ко входу вентиля 3 непосредственно и ко входу вентиля 4 через линию задержки 5. Последняя осуществляет их задержку на т 0,5т (эпюра б).

В течение пропорционального измеряемо: дальности интервала времени, ограниченного стартовым (эпюра в) со входа 13 и стоповым (эпюра г) со входа 14 импульсами, на выходе

(зпюра д}, отпирающий вентили 3 и 4. В схемах преобразователей дальности повышенной точности, как правило, Стартовый имлульс синхронизируется счетными импульсами. Поэтому их взаимное расположение ;во времени не может быть случайным и устанавливается любым при согласовании рассматриваемого устройства с им.пульсным дальномером.

Через открытые вентили 3 н 4 проходят две последовательности сдвинутых ло фазе на 180 ИМпульсов (эпюры е и ж}. Количество импзльсов в Последовательности определяется длительностью управляющего сигнала с выхода триггера 6.

В исходном СОСТОЯНИИ Счетные триггеры 1 и 2 должны иметь на выходах левых (заштрихованных) плеч относительно высокий потенциал. Цепь сброса триггеров мол-сет быть обычной.

Так как на входы схем «И 7 и 8 подаются попарно разнополярные сигналы (эпюры з, и, к и л), то в исходном состоянии на их выходах, а следовательно, и на выходе схемы «ИЛИ 9 сигнала не будет. Не будет также сигнала и на выходе правого плеча счетного триггера 2. Такое состояние преобразователя будет соответствовать запнси в нем двоичпОГО числа «00.

Приходящий первым с выхода вентиля 3 на счетный вход триггера / импульс опрокидывает его. В результате этого иа выходе схемы «И 7, а следовательно, и на выходе схемы «ИЛИ 9, т. е. на ншне JO младшего разряда появляются потенциальные имп льсы (эпюры м, н). Так как счетный триггер 2 остается Пока в исходном состоянни, то в счетчнке преобразо-вателя окажется зафиксированным двОНчное число «01.

Вслед за первым импульсом с выхода вентиля 3 появляется этот же, но задержанный на 0,5т импульс на выходе вентиля 4. Поступая на счетный вход триггера 2, он опрокидывает его. При этом обе схемы «И 7 и 5 окажутся вновь запертыми. В результате в счетчИКе преобразователя окажется зафиксированным двоичное число «10.

Второй незадержанный счетный имиульс опрокинет в исходное состояние триггер /. Теперь окажется открытой схема «И в (лпора о), что будет соответствовать записи в счетчике преобразователя двоичиого числа «11.

Этот же, но задержанный им1пульс, через 0,5 т опрокинет счетный триггер 2. Счетчик

преооразователя ПОвыщенной точности окажется в исходном состоянии, соответствующем записи В нем двоичного числа «00.

В дальнейшем нреобразователь работает аналогично. С .приходом каждого второго задержанного импульса на счетный вход триггера .2 с его выхода будет сниматься единица переноса в старший разряд счетчика.

К моменту прихода щ триггер управления 6 стоп-имлульса в Счетчике преобразователя окажется зафиксированным число jV. Этому числу будет соответствовать временной интервал

,

тде c/4fc4.H, с - скорость распространения электромагнитной энергии. Затем это число передается в фиксатор дальности арифметического устройства.

Из принципа работы предлагаемого устройства следует, что жесткие требования к инерционности схем «И 7 и и «ИЛИ 9 не предъявляются, поскольку съем числа в фиксаторе дальности производится обычно за более

длительный нромежуток времени, чем период следОВаний т счетных им-пульсов. Четкость фиксации младшего разряда в процессе ПОДсчета зДВоенного количества счетных импульсов высокой частоты хотя и может быть достигнута, но в принципе не требуется, так как она не влияет па точность результата, которая автоматически восстановится носле остановки счетчика.

Предмет изобретения

Преобразователь временных интервалов в числа двоичного кода с повышенной точностью измерения дальности, содержащнй счетные

триггеры, вентили, триггер управления, и линию задерж1ки, отличающийся тем, что, с целью получения единых чисел двоичното кода С у.меньшанной вдвое дискретностью отсчета при пониженной частоте следования счетных имп)льсов, в состав младп1его разряда включен дополнительный каскад на логических элементах «И и «ИЛИ, соединенный но цепям унравления с выходами четырех плеч указанных счетных триггеров равного быстродействия,

один из которых одновременно выполняет функцию пересчета сдвинутых но фазе на ISO счетных имиульсов и служит в качестве второго разряда преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь интервала времени в цифровой код | 1975 |

|

SU563714A2 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ДВОИЧНО-п-ИЧНОГО КОДА | 1973 |

|

SU387360A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛА ВРЕМЕНИ В ЦИФРОВОЙ КОД | 1973 |

|

SU391587A1 |

| Измеритель временных интервалов | 1980 |

|

SU930223A1 |

| Преобразователь кода в напряжение | 1974 |

|

SU674213A1 |

| Преобразователь интервала времени в цифровой код | 1976 |

|

SU588630A1 |

| МАСШТАБИРУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU360661A1 |

| ДВОИЧНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК | 1971 |

|

SU311405A1 |

| Преобразователь код-сдвиг фазы | 1972 |

|

SU439917A1 |

| Устройство для считывания графической информации | 1981 |

|

SU1016802A2 |

2 Фиг. 1

,T-//4.«,

Фиг. 2

Даты

1970-01-01—Публикация