1

Изобретение относится к области автоматики и вычислительной техпиии и предна.значено для одновременного преобразования нескольких параллельных двоично-и-ичных кодов (например, двоичло-десятичных) в соответствующие им число-им1пульсные коды.

Из;вестен многсхканальпый преобразователь параллельного двоич.носо кода в число-и-мпульсный код, содержаш.ий счетчик, регистр, динамическую вентильную цепочку, за-поминающее устройство, элементы «ИЛИ н задержки, управляющие триггеры-п вентили, схему сборки. Принци1П преобразования основан- на выработ1ке кодов уставок для двоичного кода так, что сумма уставки {Xi}ycT и вес разряда в t-ом такте преобразования () создают переполнение двоичного счетчика.

Для преобразования двоично-п-.ичных кодов по известной схеме требуется преобразователь двоич1ю-п-ичного кода в двоичный «од.

Предложенное устройство отличается тем, что содержит числовую линейку «а.ферритовых сердечниках, шпны записи кодов уставок которой соедиИены с выходами соотчветствующих шин управления разрядами запоминающего устройства, а вторичные обмот1К1И ферритовых сердечников числовой линейки соединены со входами соответствующих разрядов двоичного счетчажа. Это упрощает устройство за счет

исключения промежуточного преобразователя ДВОИЧНО-п-ИЧНОГО кода в двочиный |Код, умеиьщепия числа триггеров (вместо регистра используется счетчик) и использования только одного формирователя илшульсов управления разрядами запоминающего устройства.

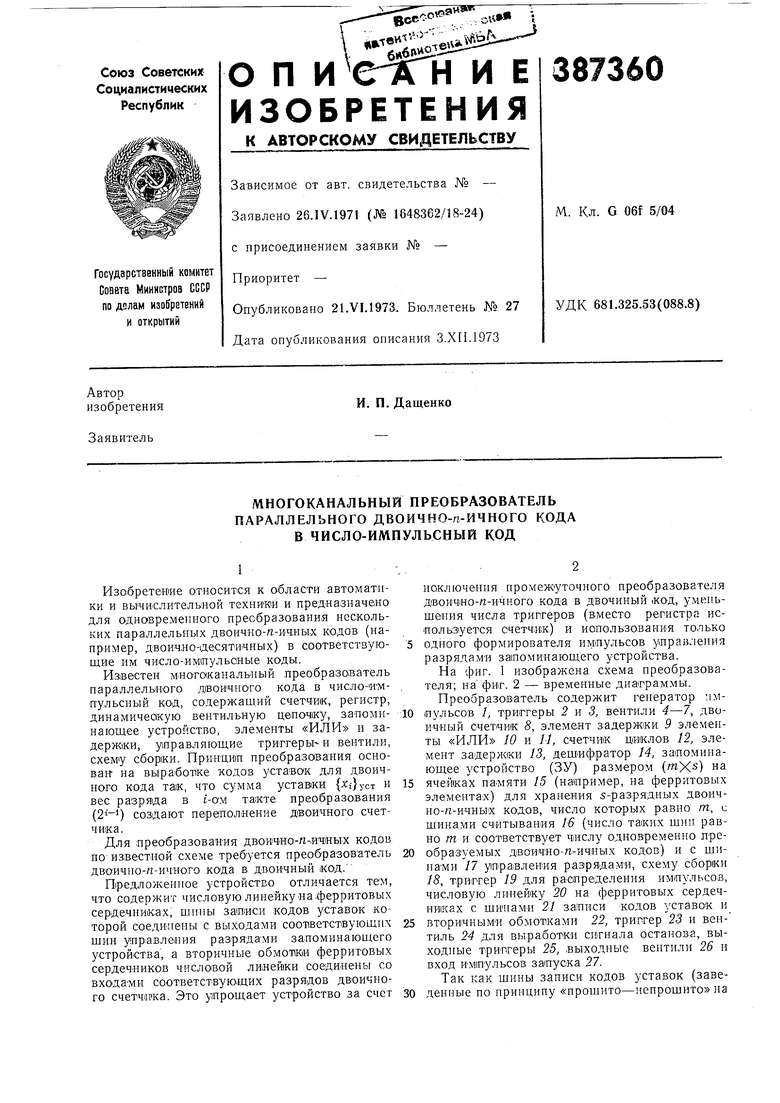

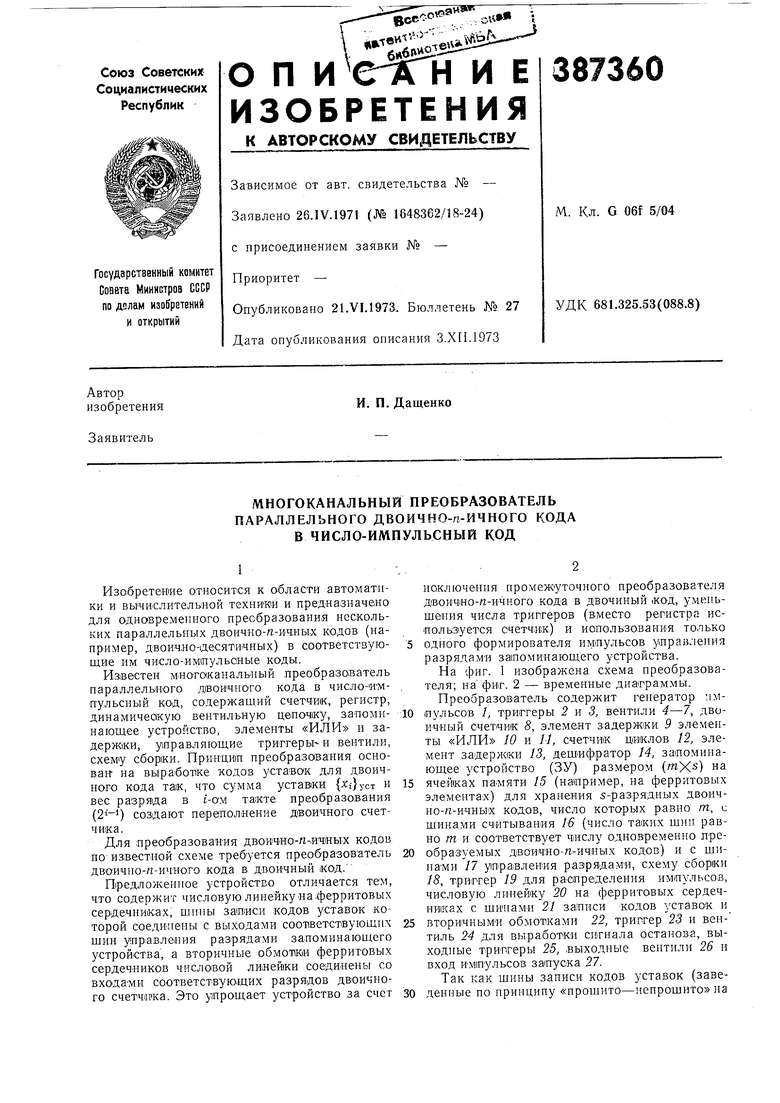

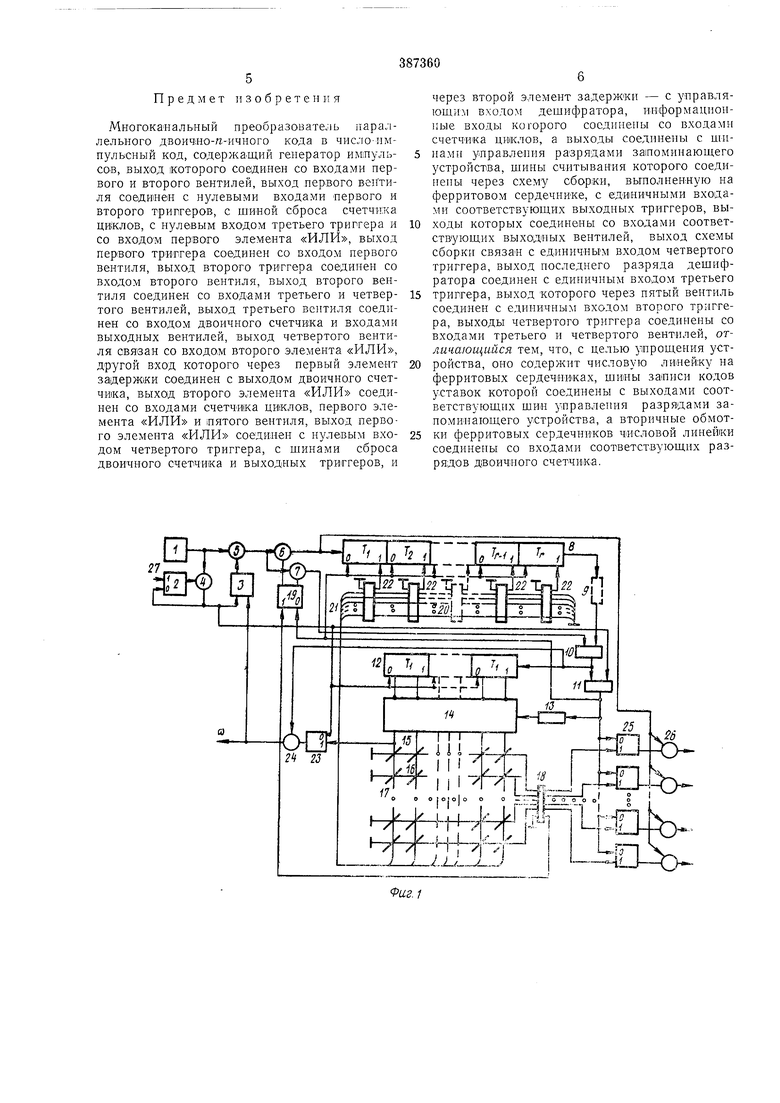

На фиг. 1 изображена схема преобразователя; на фиг. 2 - временные диаграммы. Преобразователь содержит генератор импульсов /, триггеры 2 н 3, вентили 4-7, двоичный счетчик 8, элемент задержки 9 элементы «ИЛИ 10 и 1, счетчик циклов 12, элемент задержки 13, дешифратор 14, запомииающее устройство (ЗУ) размером () на

ячейках 15 (например, на ферритовых элементах) для хранения s-разрядных двоично-ге-ичныХ кодов, число которых равно /п, и щинами считывания 16 (число таких шип равно m и соответствует числу одновременно лреобразуемых двоично-п.-ичных кодов) и с шинами 17 унравления разрядами, схему сборки 18, триггер 19 для раапределения импульсов, числовую лршейку 20 на ферритовых сердечниках с шинами 21 записи кодов уставок и

вторичными обмотками 22, триггер 23 и вентиль 24 для выработки сигнала останова, выходные триггеры 25, выходные вентили 26 и вход и-мпульсов запуска 27. Так как шины записи кодов уставок (заведенные по принципу «прошито-непрощито на

числовую линейку) жестко связаны с шинами управления разрядами ЗУ (т. е. с шинами управления считывания кодов), то появляется возможность записать любой код уставки, соответствую:щий весу данного разряда преообразуемого кода. Таиим образом, реализуется любая зависимость кода уставки от номера такта преобразования.

Преобразователь работает следующим образом.

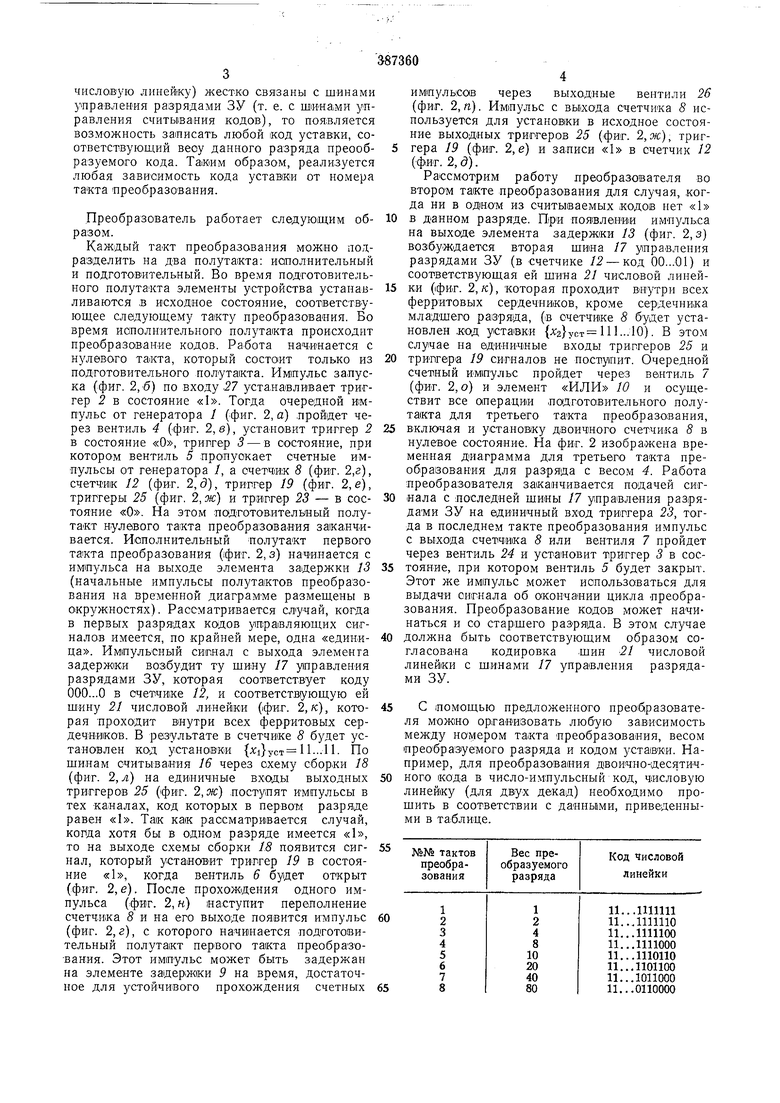

Каждый такт преобразования можно подразделить на два полутакта: исполнительный и подготовительный. Во время подготовительного полутакта элементы устройства устанавливаются в исходное состояние, соответствующее следующему такту преобразования. Бо время исполнительного полутакта происходит преобразование кодов. Работа начинается с нулевого такта, который состоит только из подготовительного полутакта. Имшульс залуска (фит. 2,-б) по входу 27 устанавливает триггер 2 в состояние «1. Тогда очередной И1Мпульс от генератора / (фиг. 2, а) .пройдет через вентиль 4 (фиг. 2,8), установит триггер 2 в состояние «О, триггер 5 - в состояние, при котором вентиль 5 пролуокает счетные импульсы от генератора /, а очетчик S (фиг. 2,г), счетчик 12 (фиг. 2,5), триггер 19 (фиг. 2,е), триггеры 25 (фиг. 2, ж и триггер 23 - в состояние «О. На этом подготовительный полутакт нулевого такта преобразования заканчивается. Исполнительный полутакт первого такта преобразования (фит. 2, з) начинается с импульса на выходе элемента задержки 13 (начальные импульсы полутактов преобразования на временной диаграмме размещены в окружностях). Рассматривается случай, когда в первых разрядах кодов у1П:ра1Вляющих сигналов имеется, по крайней мере, одна «единица. Импульсный си1лнал с выхода элемента задержки воэбудит ту шину /7 управления разрядами ЗУ, которая соответствует коду 000...О в счетчике 12, и соответствующую ей шину 21 числовой линейки (фиг. 2, к), которая Проходит внутри всех ферритовых сердечников. В результате в счетчике 8 будет установлен когД установки {xi}ycT ll-..ll. По шинам считывания 16 через схему сборки У8 (фиг. 2, л) на единичные входы выходных триггеров 25 (фиг. 2, ж) иоступят импульсы в тех каналах, код которых в первом разряде равен «1. Так как рассматривается случай, коща хотя бы в одном разряде имеется «1, то на выходе схемы сборки 18 появится сигнал, который установит триггер 19 в состояние «1, когда вентиль В будет открыт (фиг. 2, е). После прохождения одного импульса (фиг. 2, к) наступит переполнение счетч.ика S и на его выходе появится импульс (фиг. 2,г), с которого начинается подготовительный полутакт первого такта преобразования. Этот импульс может быть задержан на элементе задер;жки 9 на время, достаточное для устойчивого прохождения счетных

импульсов через выходные вентили 26 (фиг. 2, и). Импульс с выйода счетчика 5 используется для установки в исходное состояние выходных триггеров 25 (фиг. 2,ж), триггера 19 (фиг. 2, е) и записи «1 в счетчик 12 (фиг. 2,(3).

Рассмотрим работу преобразователя во втором такте преобразования для случая, когда ни в одном из считываемых кодов нет «1

в данном разряде. При появлении импульса на выхоя-е элемента задерж1ки 13 (фиг. 2, з) воз буждается вторая шина /7 управления разрядами ЗУ (в счетчике 12 - код 00...01) и соответствующая ей шина 21 числовой линейки (фиг. 2,/с), которая проходит внутри всех ферритовых сердечников, кроме сердечника младшего разряда, (в счетчике 8 будет установлен .код уставки {А;2}уст 111...10). В этом случае на единичные входы триггеров 25 и

трипгер1а 19 сигналов не поступит. Очередной счетный импульс пройдет через вентиль 7 (фиг. 2, о) и элемент «ИЛИ 10 и осуществит все с«пераци1И падготовительного полутакта для третьего такта преобразования,

включая и установку двоич ного счетчика 8 в нулевое состояние. На фиг. 2 изображена временная диаграмма для третьего такта преобравования для разряда с весом 4. Работа преобразователя закапчивается подачей сигнала с последней щины П управления разрядами ЗУ на единичный вход триггера 23, тогда в последнем такте преобразования импульс с выхода счетчика 8 или вентиля 7 пройдет через вентиль 24 и установит триггер 3 в состояние, при котором вентиль 5 будет закрыт. Этот же импульс может использоваться для выдачи сигнала об окончании цикла преобразования. Преобразование кодов может начинаться и со старшего разряда. В этом случае

должна быть соответствующим образом согласована кодировка шин 21 числовой линейки с шинами П управления разрядами ЗУ.

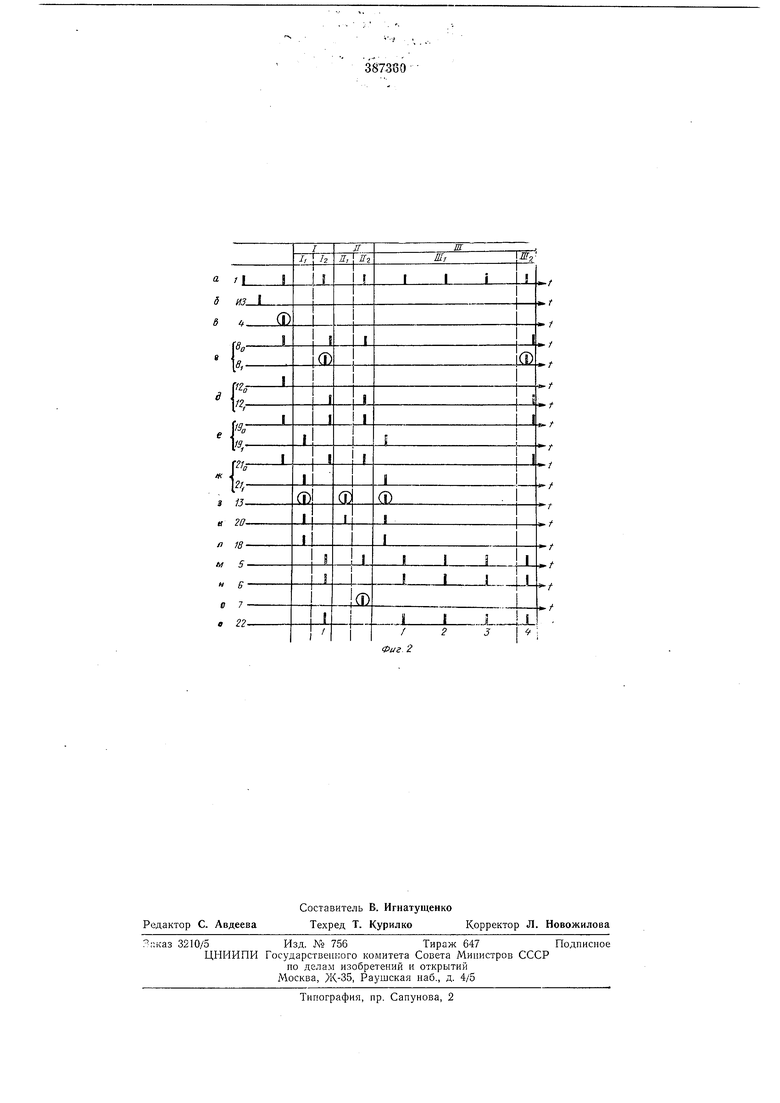

С помощью предложенного преобразователя МОЖ1НО организовать любую зависимость между номером такта преобразования, весом преобразуемого разряда и кодом уставки. Например, для преобразования двоично-десятичного кода в число-импульсный код, числовую линейку (для двух декад) необходимо прошить в соответствии с данными, приведенными в таблице.

Предмет изобретения

Многокаиальный преобразователь napa;iлельного двоичио-га-ичного кода в число-импульсный код, содержащий генератор илшульсов, выход которого соединен со входами первого и второго вентилей, выход первого вентиля соедииен с нулевыми входами первого и второго триггеров, с шиной сброса счетчика циклов, с нулевым входом третьего триггера и со входом первого элемента «ИЛИ, выход первого триггера соединен со входом первого вентиля, выход второго триггера соединен со входом второго вентиля, выход второго вентиля соединен со входами третьего и четвертого вентилей, выход третьего вентиля соединен со входом двоичного счетчика и входами выходных вентилей, выход четвертого вентиля связан со входом второго элемента «ИЛИ, другой вход которого через первый элемент задержки соединен с выходом двоичного счетчика, выход второго элемента «ИЛИ соединен со входами счетчика циклов, первого элемента «ИЛИ и иятого вентиля, выход первого элемента «ИЛИ соединен с нулевым входом четвертого триггера, с шинами сброса двоичного счетчика и выходных триггеров, и

через второй элемент задержки - с управляюшим входом дешифратора, ииформациоииые входы которого соединены со входами счетчика циклов, а выходы соединены с шинами управления разрядами затомииаюшего устройства, шины считывания которого соедипеиы через схему сборки, выполненную на ферритовом сердечнике, с единичными входами соответствующих выходных триггеров, выходы которых соединены со входами соответствующих выходных вентилей, выход схемы сборки связан с единичньгм входом четвертого триггера, выход последнего разряда дешифратора соединен с единичным входом третьего

триггера, выход которого через пятый вентиль соединен с единичным входом второго триггера, выходы четвертого триггера соединены со входами третьего и четвертого вентилей, огличающийся тем, что, с целью упрощения устройства, оно содержит числовую линейку на ферритовых сердечни1ках, ши1ны заииси кодов уставок которой соединены с выходами соответствующих шин управления разрядами запоминающего устройства, а вторичные обмотки фер:ритовых сердечников Ч1исловой линейки соединены со входами соответствующих разрядов двоичного счетчи1ка.

| название | год | авторы | номер документа |

|---|---|---|---|

| АССОЦИАТИВНО-АДРЕСНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU336697A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1720160A1 |

| ЗВУКОВОЙ ДЕКОДЕР | 1993 |

|

RU2099905C1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1035794A1 |

| Система автоматического контроля качества псевдоожижения в печи кипящего слоя | 1982 |

|

SU1076475A1 |

| Счетчик импульсов | 1980 |

|

SU875640A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Запоминающее устройство | 1973 |

|

SU446107A1 |

| МНОГОКАНАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1967 |

|

SU224589A1 |

g Ть Г о -ч - п П П г л П I . , 1 t-f-7f-lT Н S I 1,.- 1 I iO 1 / J b

Авторы

Даты

1973-01-01—Публикация