Изобретение относится к импульсной технике и предназначено для осуществления операции логического умножения.

Известен ряд схем совпадения, реализованных на базе двух ферротранзисторных элементов. Эти феррит-транзисторные схемы совпадения, содержап1,ие ферритовые сердечники (запоминающие и компенсационные) с обмотками записи, считывания и управления и транзистор, включенный по схеме с общим эмиттером, требуют большого количества активных элементов.

С целью упрощения в предложенной схеме совпадения обмотки записи запоминающих сердечников соединены последовательно и встречио с обмоткой записи компенсационного сердечника, которая, в свою очередь, соединена с сопротивлением в цепи базы транзистора.

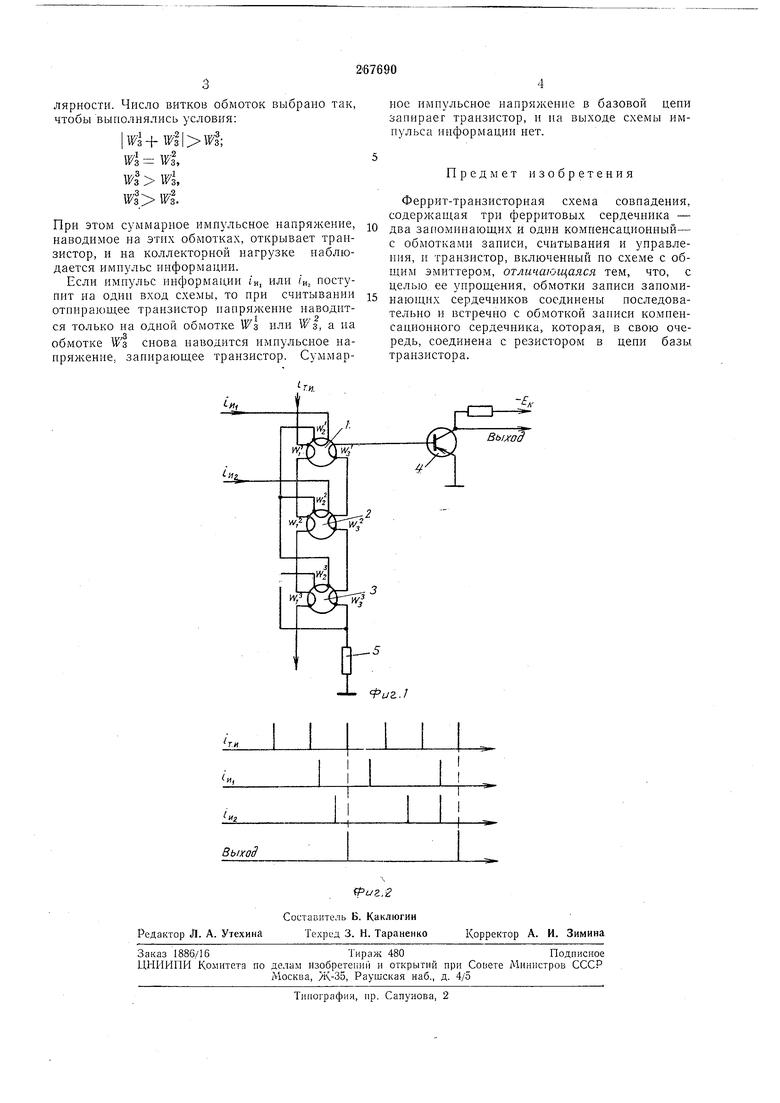

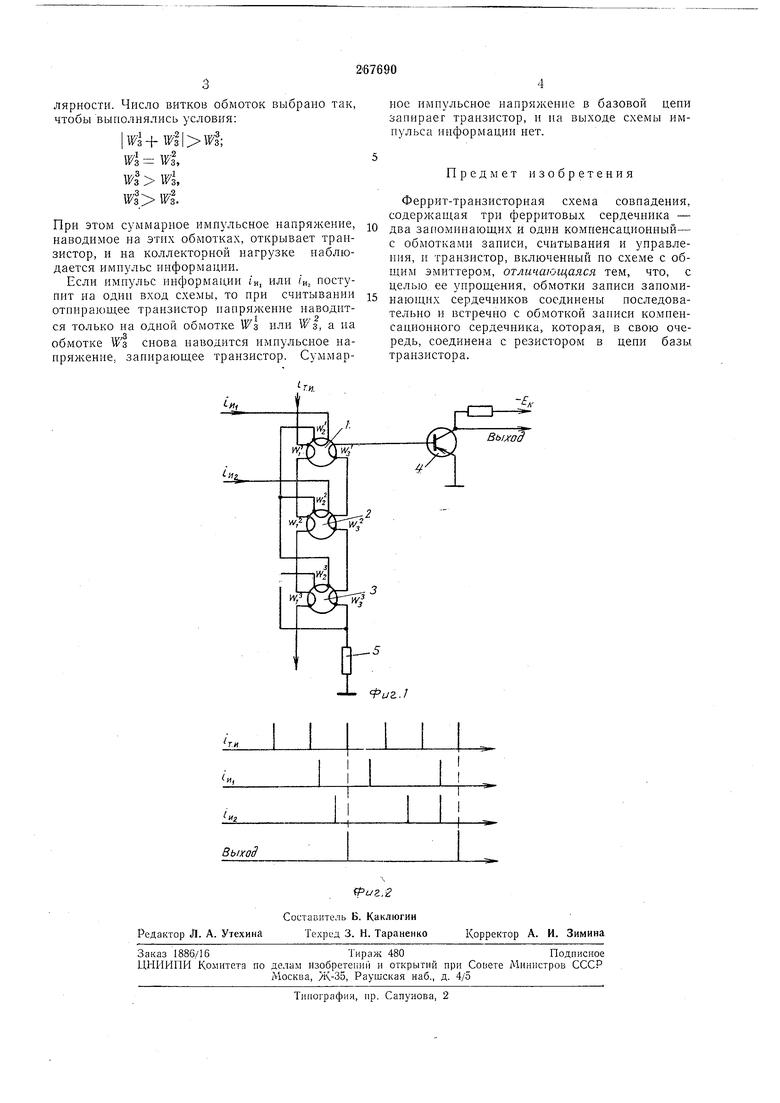

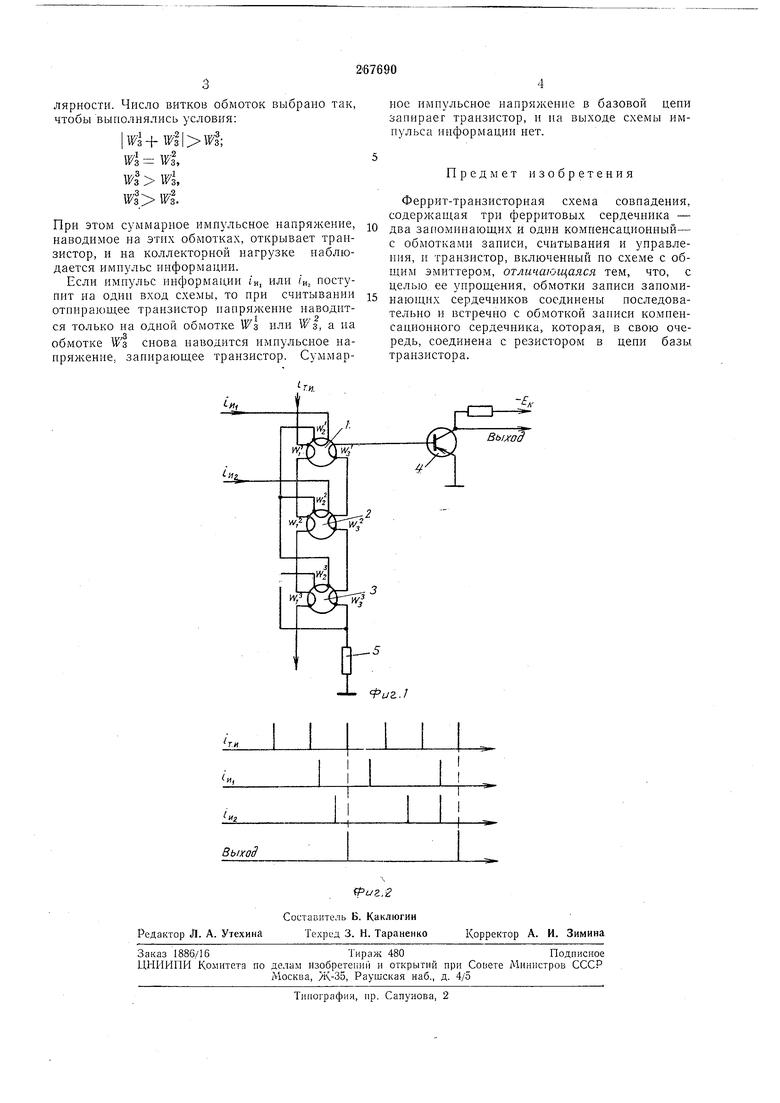

На фиг. 1 показана принципиальная схема устройства; на фиг. 2 - времеиная диаграмма ее работы.

Схема совпадения содержит два запоминаю. щих сердечника 1, 2 и один компенсационный 3. Каждый сердечник содержит обмотки управления W - Wi , обмотки записи Wy и обмотки считывания Ws - зстора 4 включена цепочка, составленная из последовательно соединенных обмоток считывания 11з, IFs, Ws и сопротивления 5.

Обмотки заииси W2 и W сердечииков } и 2 соедпг1еиы иоследовательно и встречно с обмоткой записи W сердечника 5, которая, в свою очередь, соедииеиа с пезаземленной точкой сопротивления-5.

Устройство работает следующим образом.

Импульсы тока информации /и, и tm могут поступать на ячейку одновременно или разновремеиио в промежутке между тактовыми импульса мп /т.и .

Поступающие на входы схемы имиульсы тока ииформации /и, записывают в сердечник /, а импульсы ги, - в сердечник 2 магнитное состояние одного иаправления, и одновременно оба импульса записывают в сердечник 3 магнитное состояние обратного направления. При записи за счет подключения обмоток заииси к сопротивлеиию 5, включенному в цепь базы транзистора 4, осуществляется запирание транзистора.

Если импульсы информации ini и ги, иоступили на оба входа одновременно или разновременно, то ири считывании тактовым импульсом /т.и на обмотках Wl и W наводятся импульсные напряжения отрицательной полярности, а на обмотке Wl-положительной полярности. Число витков обмоток выбрано так, чтобы выполнялись условия:

wl wl, wl wl, wl wl.

При этом суммарное импульсное напряжение, наводимое иа этих обмотках, открывает транзистор, и на коллекторной нагрузке наблюдается импульс информации.

Если импульс информации ги, или (и, поступит на один вход схемы, то при считывании отпирающее транзистор напряжение наводится только на одной обмотке Wz или W з, а иа обмотке W снова наводится импульсное напряжение, запирающее транзистор. Суммарi y

ное импульсное напряжение в базовой цепи запирает транзистор, и иа выходе схемы импульса информации нет.

Предмет изобретения

Феррит-транзисторная схема совпадения, содержащая три ферритовых сердечника -

два запоминающих и один комиенсационный- с обмотками записи, считывания и управлеиия, и транзистор, включенный по схеме с общ,им эмиттером, отличающаяся тем, что, с целью ее упрощения, обмотки записи заноминающих сердечников соединены последовательно и встречно с обмоткой записи компенсационного сердечника, которая, в свою очередь, соединена с резистором в цепи базы транзистора.

-..J

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРОИЧНАЯ ЯЧЕЙКА С НЕРАЗРУШАЕМЫМ СЧИТЫВАНИЕМ | 1965 |

|

SU173025A1 |

| Распределительное устройство | 1982 |

|

SU1083233A1 |

| Несимметричный феррит-транзисторный двухтактный триггер | 1960 |

|

SU150131A1 |

| Устройство для формирования тактовых импульсов | 1990 |

|

SU1746518A1 |

| РАСПРЕДЕЛИТЕЛЬ НА ТИРИСТОРАХ | 1970 |

|

SU275122A1 |

| ФЕРРИТ-ТРАНЗИСТОРНАЯ ЯЧЕЙКА | 1969 |

|

SU242967A1 |

| УСТРОЙСТВО ПЕРЕЗАПИСИ ИНФОРМАЦИИ ДЛЯ ФЕРРИТОВОГО СЕРДЕЧНИКА | 1972 |

|

SU360692A1 |

| МАГНИТНЫЙ АДАПТИВНЫЙ ЭЛЕМЕНТ | 1972 |

|

SU358784A1 |

| СОХРАНЯЮЩИЙ ИНФОРМАЦИЮ ПРИ ПЕРЕРЫВАХПИТАНИЯ | 1969 |

|

SU238237A1 |

| АДАПТИВНЫЙ ЭЛЕМЕНТ | 1969 |

|

SU239382A1 |

Даты

1970-01-01—Публикация