Изобретение относится к области преобразования и кодирования информации.

Известны преобразователи числа импульсов в фазу, содержащие счетный триггер, источник опориого сигнала, выход которого подключен ко входу счетчика опорного канала и первому входу счетчика рабочего каиала, второй вход которого подсоединен к выходу источника управляющего сигнала. Недостатком этих преобразователей является низкая надежность преобразования.

Предлагаемый преобразователь отличается тем, что содержит инвертор, реверсивный счетчик, формирователь, две схемы совпадения и собирательную схему, причем вход реверсивного счетчика объединен с выходом источника управляющего сигнала, а выход подсоединен ко входу триггера и через формирователь - к иервым входам схем совнадения, вторые входы которых соединены с выходом .счетчика рабочего ка.-пла, третьи входы первой схемы совпадения непосредственно, а второй схемы через инвертор - к выходу счетчика опорного канала, четвертые входы - к двум плечам триггера, а выходы схем совпадения соединены со входами собирательной схемы.

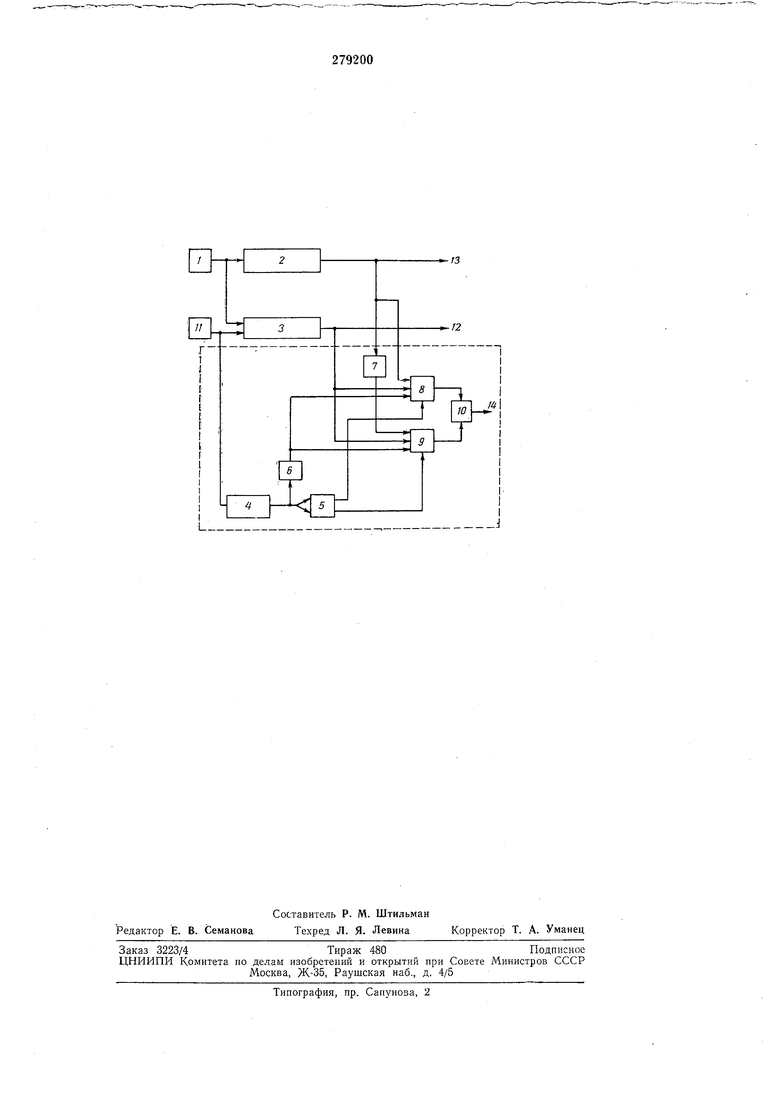

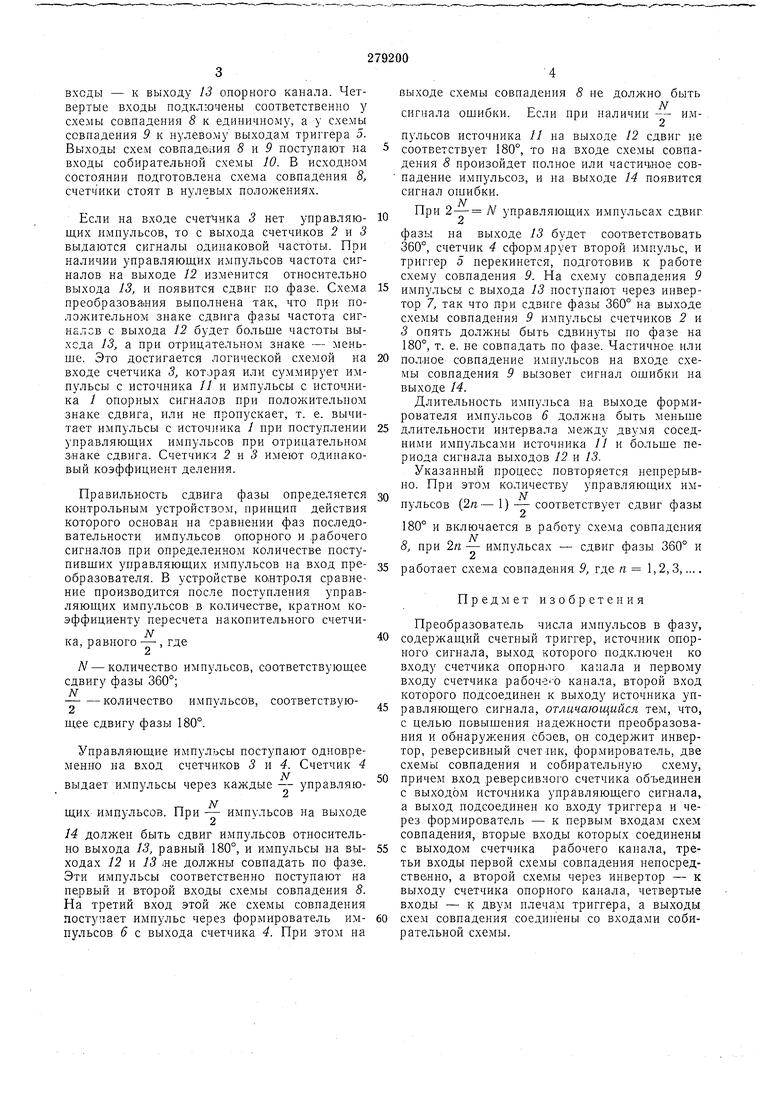

На чертеже приведена схема оиисываемого преобразователя.

Преобразователь состоит из источника / опорных сигналов счетчика 2 опорного канала

для формирования выходного опорного сигнала, счетчика 3 рабочего канала с синхронизатором и логическим входом для формирования выходного рабочего сигнала, сдвинутого по фазе, контроль1ого устройства, состоящего из реверсивного накопительного счетчика 4 с коэффициентом пересчета, равным половине коэффициента пересчета рабочего канала, счетного триггера 5, формирователя импульсов 6, инвертора 7, схем совпадения 8 и

9, собирательной схемы 10 и источиика 11 управляющего сигнала.

Выход источника 1 опорного сигнала подключен ко входам опорного и рабочего каналов счетчиков .2 и . К логическому входу рабочего канала подсоединен выход источника управляющих импульсов. Один вход устройства контроля (счетный вход счетчика 4) иодключен к логическому входу рабочего канала, а два вторых входа соответственно - к рабочего и опорного каналов. Выход счетчика 4 подсоединен к счетному входу триггера 5 и ко входу формирователя импульсов 6, выход которого подключен к первым входам схем совпадения 8 и 9. Вторые их входы иодвходы - к выходу 13 опорного канала. Четвертые входы подключены соответственно у схемы совпадения 8 к единичному, а у схемы совпадения 9 к нулевому выходам триггера 5. Выходы схем совпадения S и 5 поступают на входы собирательной схемы 10. В исходном состоянии подготовлена схема совпадения 8, счетчики стоят в нулевых положениях.

Если на входе счетчика 3 нет управляющих импульсов, то с выхода счетчиков 2 и 3 выдаются сигналы одинаковой частоты. При наличии управляюш,их импульсов частота сигналов на выходе 12 изменится относительно выхода 13, и появится сдвиг по фазе. Схема преобразования выполнена так, что при положительном знаке сдвига фазы частота сигналов с выхода 12 будет больше частоты выхода 13, а при отрицательном знаке - меньше. Это достигается логической схемой на входе счетчика 3, которая или суммирует импульсы с источника 11 и импульсы с источника / опорных сигналов при полончительном знаке сдвига, или не пропускает, т. е. вычитает импульсы с источ ика / при поступлении управляющих импульсов при отрицательном 3|Наке сдвига. Счетчики 2 и 3 имеют одинаковый коэффициент деления.

Правильность сдвига фазы определяется контрольным устройством, принцип действия которого основан на сравнении фаз последовательности импульсов опорного и рабочего сигналов при определенном количестве поступивших управляющих импульсов на вход преобразователя. В устройстве контроля сравнение производится после поступления управляющих импульсов в количестве, кратном коэффициенту пересчета накопительного счетчиNка, равного -, где

Л - количество импульсов, соответствующее сдвигу фазы 360°;

;v

- -количество импульсов, соответствующее сдвигу фазы 180°.

Управляющие импульсы поступают одновременно на вход счетчиков 3 и 4. Счетчик 4

N выдает и.мпульсы через каждые - управляюгтN

щих импульсов. При - импульсов на выходе

14 должен быть сдвиг импульсов относительно выхода 13, равный 180°, и импульсы на выходах 12 и 13 яе должны совпадать по фазе. Эти импульсы соответственно поступают на первый и второй входы схемы совпадения 5. На третий вход этой же схемы совпадения поступает импульс через формирователь импульсов 6 с выхода счетчика 4. При этом на

выходе схемы совпадения 8 не должно быть

сигнала ошибки. Если при наличии - импульсов источника 11 на выходе 12 сдвиг не 5 соответствует 180°, то на входе схемы совпадения 5 произойдет полное или частичное совпадение импульсов, и на выходе 14 появится сигнал ошибки.

N При 2- Л управляющих импульсах сдвиг

фазы на выходе 13 будет соответствовать 360°, счетчик 4 сформирует второй импульс, и триггер 5 перекинется, подготовив к работе схему совпадения 9. На схему совпадения 9

5 импульсы с выхода 13 поступают через инвертор 7, так что при сдвиге фазы 360° на выходе схе.мы совпадения 9 импульсы счетчиков 2 и 3 опять должны быть сдвинуты по фазе на 180°, т. е. не совпадать по фазе. Частичное или полное совпадение импульсов на входе схемы совпадения 9 вызовет сигнал ошибки на выходе 14.

Длительность импульса на выходе формирователя импульсов 6 должна быть меньше

5 длительности интервала между двумя соседними импульсами источника /У и больше периода сигнала выходов 12 и 13.

Указанный процесс повторяется непрерывно. При этом количеству управляющих импульсов (2п-1) -соответствует сдвиг фазы

Zi

180° и включается в работу схема совпадения

дг

8, при 2« - импульсах - сдвнг фазы 360° и 5 работает схема совпадения 9, где и 1,2,3,....

Предмет изобретения

Преобразователь числа импульсов в фазу,

0 содержащий счетный триггер, источник опорного сигнала, выход которого подключен ко входу счетчика опорного капала и первому входу счетчика рабоче-о канала, второй вход которого подсоединен к выходу источника управляющего сигнала, отличающийся тем, что, с целью повышения надежности преобразования и обнаружения сбоев, он содержит инвертор, реверсивный счет IHK, формирователь, две схемы совпадения и собирательную схему,

0 причем вход .реверсивного счетчика объединен с выходом источника управляющего сигнала, а выход подсоединен ко входу триггера и через формирователь - к первым входам схем совпадения, вторые входы которых соединены

5 с выходом счетчика рабочего канала, третьи входы первой схемы совпадения непосредственно, а второй схемы через инвертор - к выходу счетчика опорного канала, четвертые входы - к двум плечам триггера, а выходы

схем совпадения соединены со входами собирательной схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий фазометр | 1980 |

|

SU894595A1 |

| Многоканальное устройство для управ-лЕНия -фАзНыМ иНВЕРТОРОМ | 1979 |

|

SU813669A1 |

| Калибратор фазы звуковых и инфразвуковых частот | 1975 |

|

SU570852A1 |

| Преобразователь фаза-код | 1980 |

|

SU960656A1 |

| Мера фазового сдвига | 1983 |

|

SU1103156A1 |

| Цифровой фазометр | 1977 |

|

SU690407A1 |

| Устройство для передачи и приема дискретной информации | 1980 |

|

SU886295A1 |

| Способ цифрового управления многофазным инвертором | 1989 |

|

SU1683154A1 |

| Следящий фазометр | 1980 |

|

SU1038885A1 |

| Устройство для раздельного управления многофазным реверсивным вентильным преобразователем | 1979 |

|

SU773897A1 |

Даты

1970-01-01—Публикация