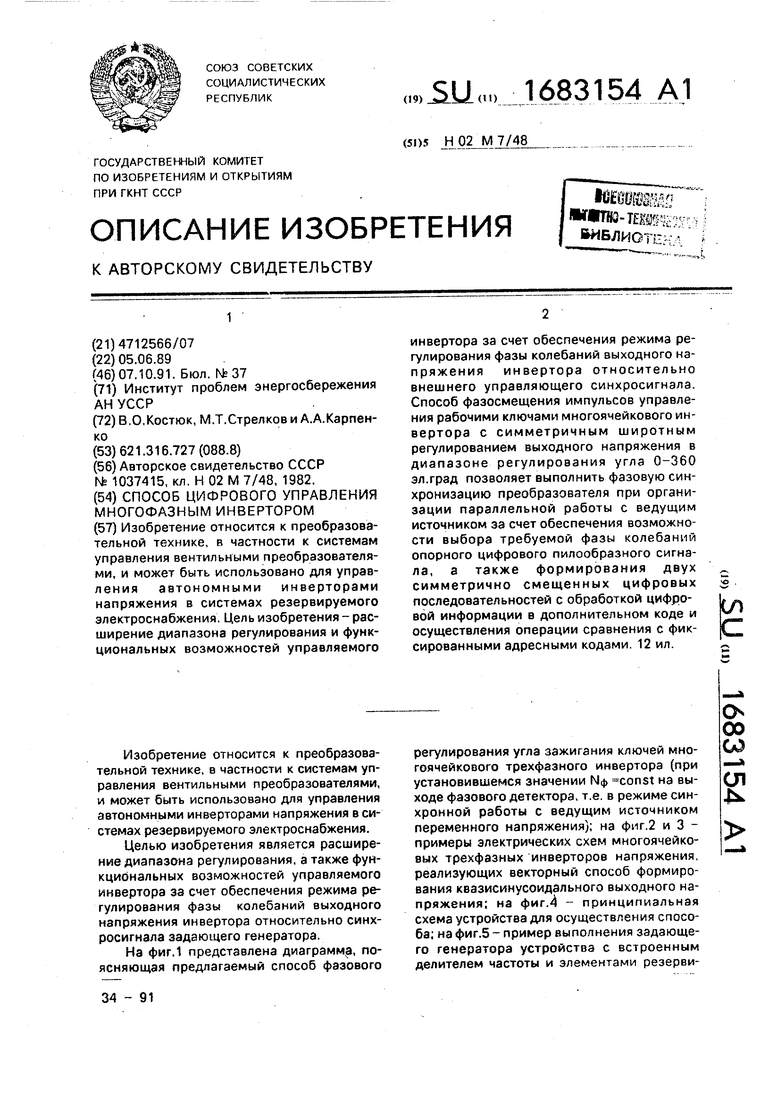

Изобретение относится к преобразовательной технике, в частности к системам управления вентильными преобразователями, и может быть использовано для управления автономными инверторами напряжения в системах резервируемого электроснабжения.

Целью изобретения является расширение диапазона регулирования, а также функциональных возможностей управляемого инвертора за счет обеспечения режима регулирования фазы колебаний выходного напряжения инвертора относительно синхросигнала задающего генератора.

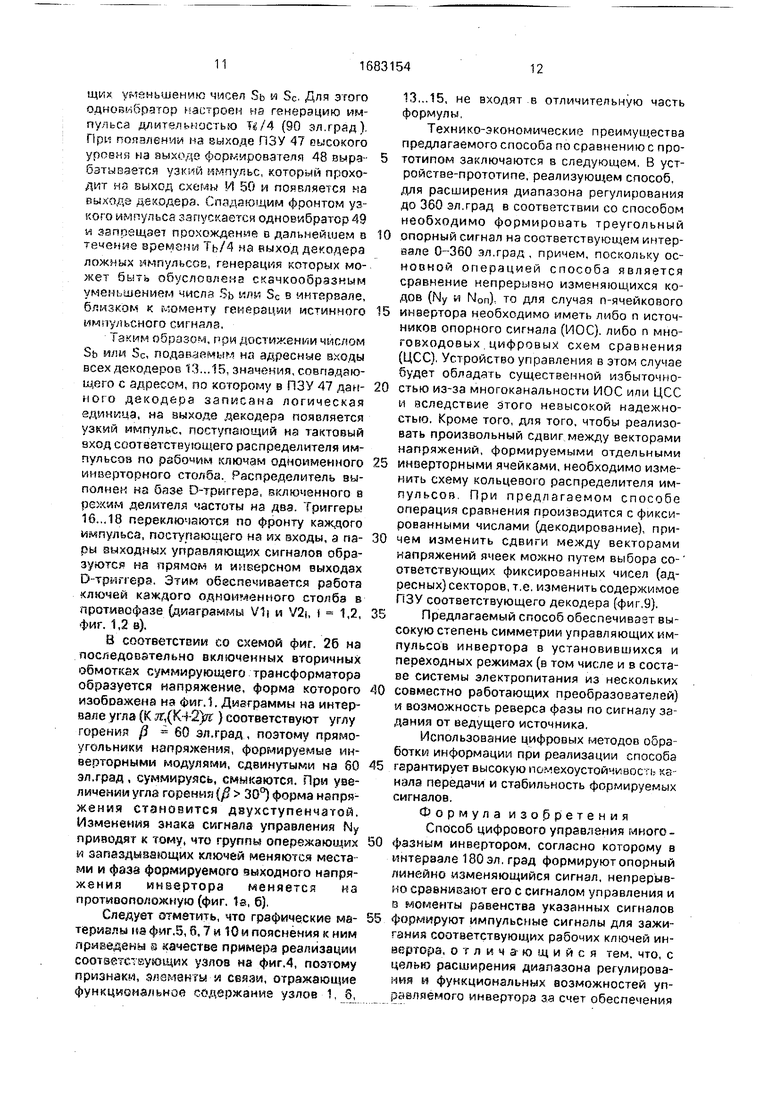

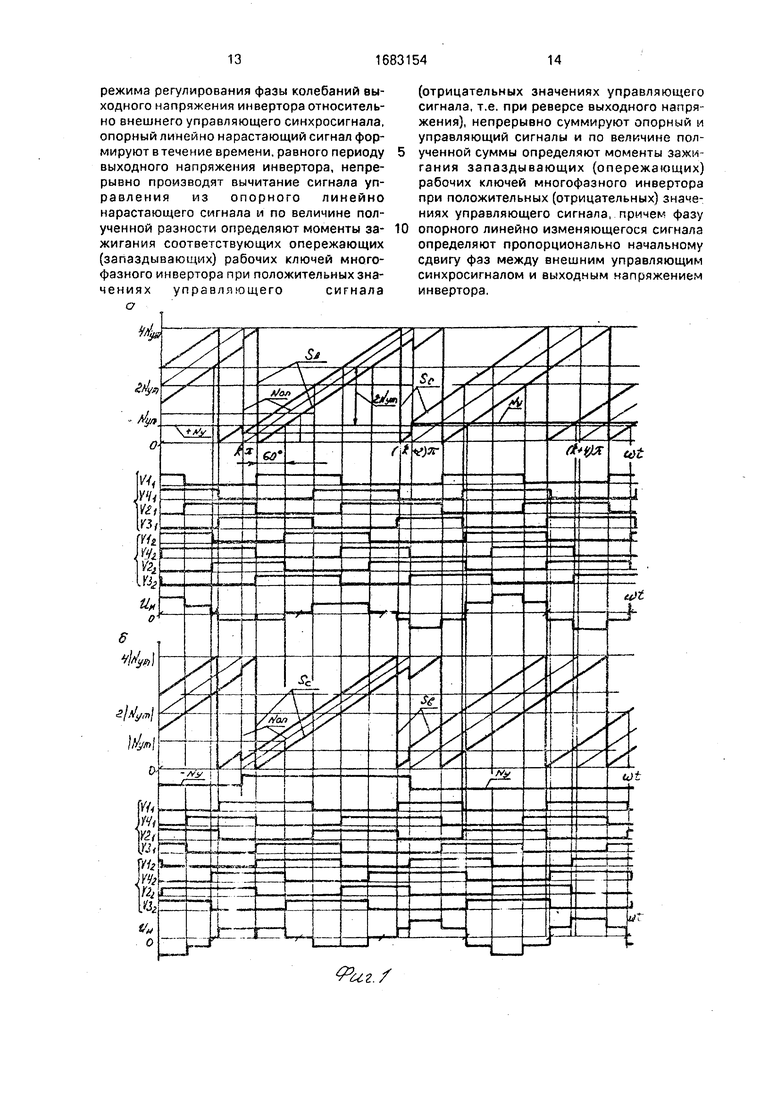

На фиг.1 представлена диаграмма, поясняющая предлагаемый способ фазового

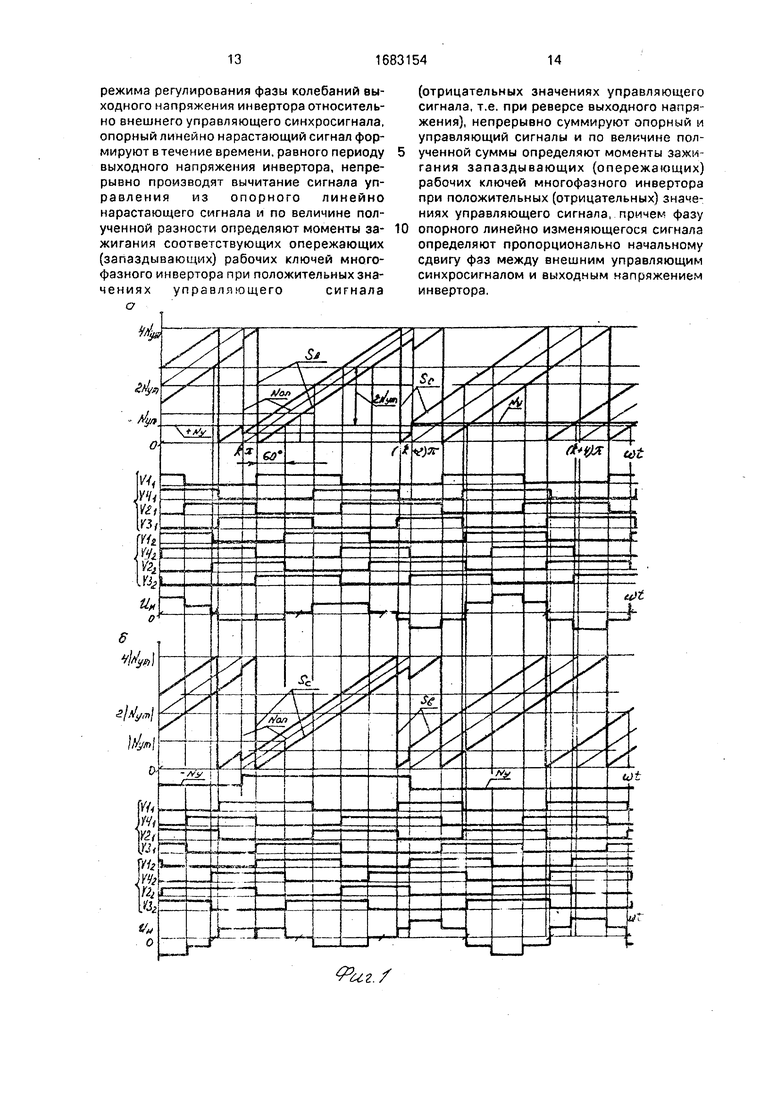

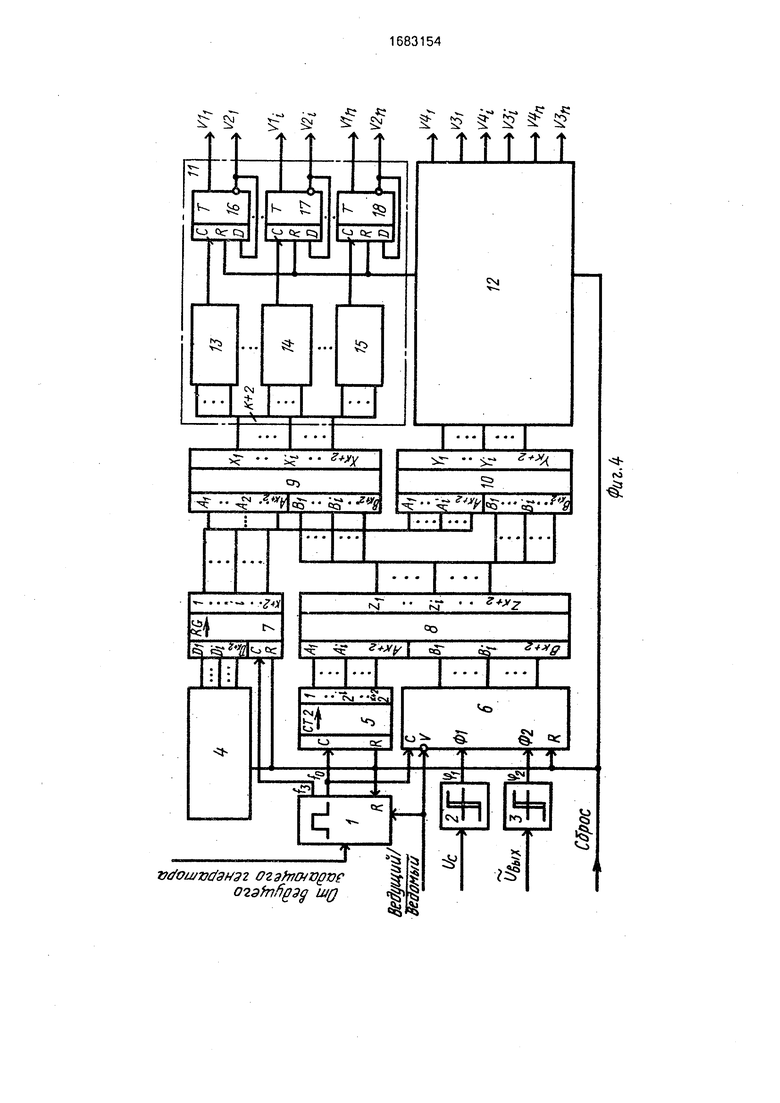

регулирования угла зажигания ключей многоячейкового трехфазного инвертора (при установившемся значении Мф const на выходе фазового детектора, т.е. в режиме синхронной работы с ведущим источником переменного напряжения); на фиг.2 и 3 - примеры электрических схем многоячейковых трехфазных инверторов напряжения, реализующих векторный способ формирования квазисинусоидального выходного напряжения; на фиг.4 - принципиальная схема устройства для осуществления способа; на фиг.5 - пример выполнения задающего генератора устройства с встроенным делителем частоты и элементами резервиО 00

ы

СП

-N

Изобретение относится к преобразовательной технике, в частности к системам управления вентильными преобразователями, и может быть использовано для управления автономными инверторами напряжения в системах резервируемого электроснабжения. Цель изобретения - расширение диапазона регулирования и функциональных возможностей управляемого инвертора за счет обеспечения режима регулирования фазы колебаний выходного напряжения инвертора относительно внешнего управляющего синхросигнала. Способ фазосмещения импульсов управления рабочими ключами многоячейкового инвертора с симметричным широтным регулированием выходного напряжения в диапазоне регулирования угла 0-360 эл.град позволяет выполнить фазовую синхронизацию преобразователя при организации параллельной работы с ведущим источником за счет обеспечения возможности выбора требуемой фазы колебаний опорного цифрового пилообразного сигнала, а также формирования двух симметрично смещенных цифровых последовательностей с обработкой цифровой информации в дополнительном коде и осуществления операции сравнения с фиксированными адресными кодами 12 ил. ел С

34 - 91

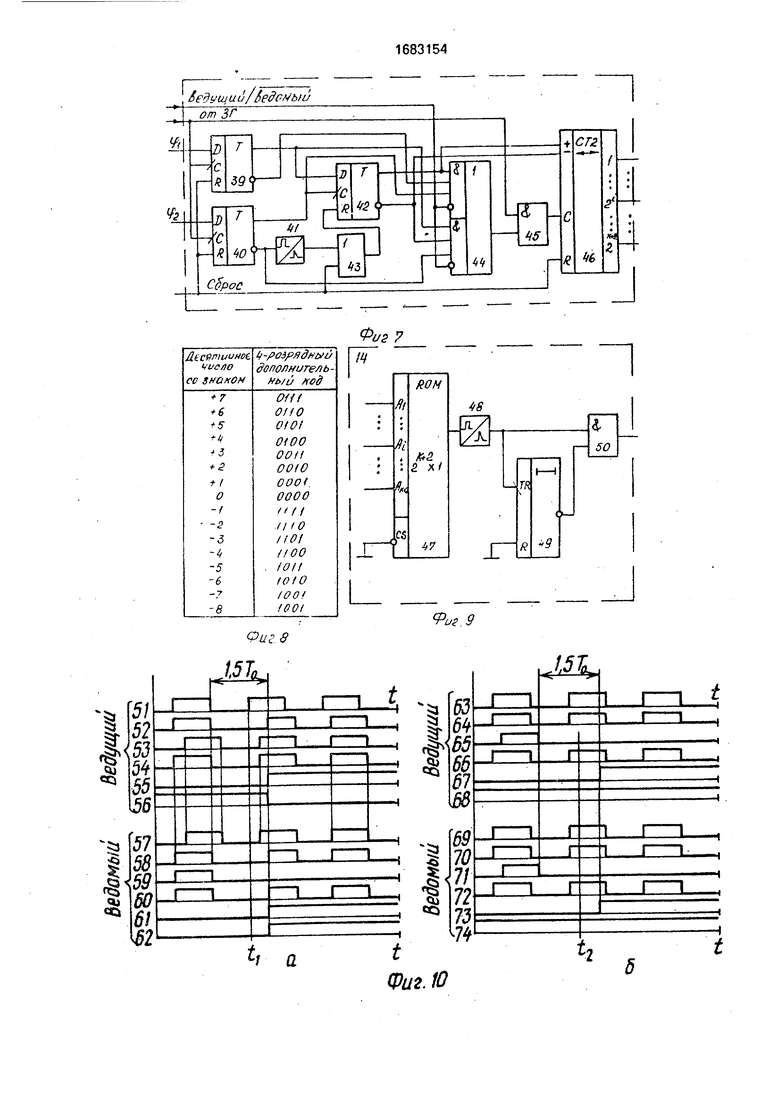

резания при параплельчой работе однотип- мшх мчо( инверторов; на фиг.6 - гЮ лп о ь:попнон. опорного задающего rtfHtjmeD. з отлэге задающего генерзтор.5 У СО С/ фЯ301 0 ЯВТОПОДСТрОЙКИ

(ФДП) rips opi параллельной рабо- гн viHL-jpTjp с ceiыо; м фчг. / - принцыпи- гпьчая схема цифрового фазового (SieKrop j; м фчг.8 - -аблица представления четырехрачочдммч двоичных чисел а до- пог(:н тельцом ходе. на фиг.9 - по нципиаяочзя эле;ср ческая схемэ деко- .цвоя; мз фиг 10 - / граммы, поясняющие иоинцчп ppfjoin ркзор зуфуеиого задающе- ю генроагопс ; на Фмг -диаграммы, пояг.- jiTivft ..ип цифрового фазог1.т-одртег.7орй, нафиг.12 -диаграммы 1 чист и для .зекоцеров, определяющих г. оменть1 oa, рабочих ключей ннчер- тора.

На фиг 5 приведены импульсные после- гппатйл ноети управления ключами двух- М Х -льпого инчертоЕО по фиг, 26. Просгрансгвскно-ср менной сдвиг иежду векторами эоцульных напряжений составляет 60 элл рад ; чз зз наличия указанного сдг/игз ме;кду векторами напряжений модулей чз них в дальнейшем будем называть первь -я, а другом, вектор напряжения которого отстает от пераого на 60 эл.грзд, - sTopt i-fl, в обозначение ключевых элементе s модулей в соответсгоии с фиг.2 введены соотаатсше чо инцзксы i -- 1 и i 2. Фыг.1а гтргжзет фоомкровэние упоавляющих сиг- «глоа ключами V11. ,V3j с помощью предла- гаемо о способа при положительных значениях управляющего сигнала Ny; при- чйм из декению цифрового сигнала Ny от О до Nym соогветствует диапазон регулирования угла инвертора 0-180 эг, град.

Способ управления заключается в том, что, с и,°,лью синхронизации инвертора с едущим wcro i iwKOM перемзннсно напоч- жения при оргзьи ащ м параллельной работы пилообразный опорный сигнал М0п формируют в течение времени, разного периоду выходного напряжения инвертора в виде цифровой последовательности N0n -N0n(i), представлчющбй собой алгебраическую сумму:

Non(0 ) t Мф(1).

где Мсч{) линейно изменяющееся число чэ выходе счетчика;

МФ(1) - смещение, т.е. число, пропорциональное разности фяз колебаний напряжения инвертора и напряжения ведущего источим на 8 режиме синхронизации.

Затем одновременно и непрерывно осуществляют операции сложения и вычитания над текущими значеч эякм опорного сигнала Non(t) и сигнала управления Ny(t). получая две симметрично смещенные относительно кривой Non N0n(t) цифровые последователь) г ости Sh(t) и Sc(t) в виде Sb(t) Non(t) - Ny(t).

Sc(t) Non(t) + Ny(t).

которые в дальнейшем подвергают непрерывному декодированию (сравнивают с фиксированными наборами чисел - адре- сов) с помощью декодеров, число которых равно числу столбов рабочих ключей много- Фазного инвертора. При этом требуемый фиксированный фазовый сдвиг между зонами регулирования соответствующих тири- стороа обеспечивают выбором границ соответствующих секторов Xk и YI значений адресов AI и

i a, b}; k, 1,n;

Yi {Bj; J a cd); {i, j, a, b, c, d} e ( 0, Non max, где п - число модулей в составе многомодульного инвертора;

Аа, Аь, Be, 8,-j - граничные значения адресных секторов;

Nonmax - максимальное значение опор- ного цифрового сигнала;

К - разрядности управляющего слова Ny, если Ny 0 (т.е. Ny(n - 2К- 1)

Управляющие сигналы XR и yi для к-й (i-й) пары рабочих ключей одноименного столба инвертора генерируются в соответствии с выражениями

хк 5ьЛ XR,

yi Sc Л Y|. l 1,n.

При этом получают сигналы управления опережающими (запаздывающими) рабочими ключами инвертора при положительных (отрицательных) значениях управляющего сигнала Ny. Соответствующие диаграммы цифровых последовательностей (N0n, 5ь и Sc) и сигналов управления рабочими ключами представлены на фиг, 1а и б соответственно. Поскольку рабочие ключи одноименного столба инверторной ячейки находятся в противофазе, распределение импульсов управления на каждый из ключей легко достигается путем деления частоты импульсных сигналов xk и ус на два.

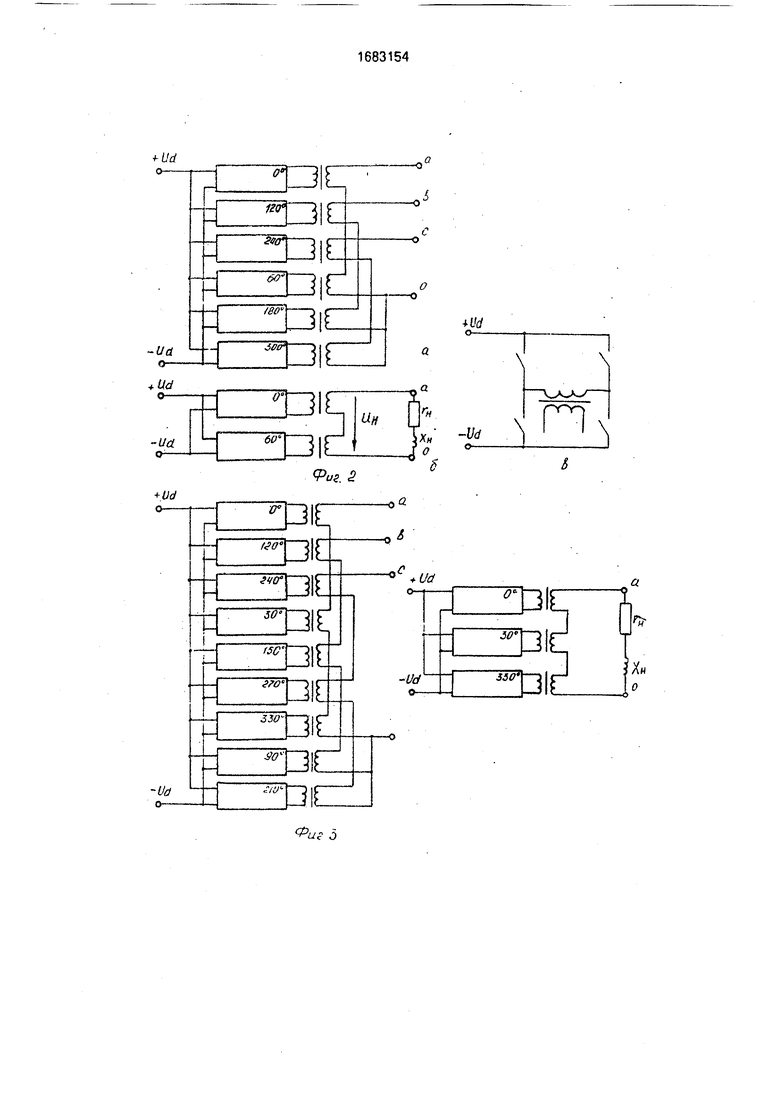

Устройство управления многофазным инвертором (фиг.4) содержит задающий генератор (ЗГ}1 с встроенным делителем частоты, узлом управления и индикации неисправностей (фиг.5), нуль-компараторы 2 и 3, цифровой блок 4 задания, счетчик 5, цифровой фазовый детектор 6, буферный регистр 7, сумматор 8, вычислитель 9, сумматор 10 и два блока 11 и 12 формирования управляющих импульсов. Блоки 11 и 12 устроены одинаково и содержат каждый группу декодеров 13,..15 и триггеров 16...18, число

которых равно количеству п ячеек многоячейкового инвертора.

Высокочастотный выход задающего генератора 1 подключен к счетному входу счетчика 5, а низкочастотный - к тактовому входу регистра 7. Выходы счетчика 5 подключены к первой группе входов сумматора 8, входы второй группы которого связаны с выходами цифрового фазового детектора. Выходы регистра 7 соединены с первыми входами вычитателя 9 и сумматора 10, а выходы первого сумматора 8 - с вторыми входами сумматора 10 и вычитателя 9. Выходы нуль-компараторов 2 и 3 соединены с первым и вторым фазовыми входами фазо- вого детектора 6 соответственно. Выходы вычитателя 9 (сумматора 10) соединены с соответствующими входами декодеров блока 11 (12) формирования управляющих импульсов. Выход каждого декодера 13...15 подключен к счетному входу соответствующего D-триггера 16...18. Инверсный выход каждого триггера связан с собственным информационным входом. При этом информационные входы регистра 7 подключены к выходам цифрового блока 4 задания, а все установочные входы R цифровых схем подключены к общей шине Сброс. Входы управления цифрового фазового детектора 6 и задающего генератора 1 подключены к ши- не назначения приоритета Ведущий/ведомый (для группы работающих параллельно преобразователей).

Для организации параллельной работы двух преобразователей с синхронизацией по схеме От общего задающего генератора с резервным блок задающего генератора содержит опорный задающий генератор (3Q 19, буферные усилители 20...22, мультиплексор 23, триггер 24, схемы ИЛИ 25 и 26, мажоритарный элемент 27, делитель 28 частоты, устройство индикации неисправностей на базе одновибраторов 29 и 30 с перезапуском и светодиодных индикаторов 31...33. Для организации параллельной ра- боты инвертора с сетью ЗГ 19 содержит нуль-компаратор 34, триггер 35 управления, управляемый ключ 36, схему 37 фазовой автоподстройки (ФАП) и делитель 38 частоты.

Цифровой фазовый детектор 6 может быть выполнен в виде D-триггеров 39 и 40, формирователя 41 короткого импульса, D- триггера 42, схемы ИЛИ 43. логической схемы 44,блока 45 совпадения и реверсивного счетчика 46. Декодеры содержат постоян- ное запоминающее устройство (ПЗУ) 47, формирователь 48 короткого импульса, од- новибратор 49 без перезапуска и схему И 50. На фиг. 10... 12 представлены диаграммы 51...88.

Устройство работает следующим образом.

Задающий генератор 1 формирует высокочастотный сигнал частотой

f0 (2VM-iyrb. где VM К+2 - разрядность счетчика 5;

Ть 1/fb период выходного напряжения инвертора,

который поступает на счетный вход счетчика 5, и сигнал с частотой fa, с помощью которого осуществляется запись цифровой информации с выходов блока 4 задания в буферный регистр 7 в требуемые моменты времени. При этом частота f3 определяется в соответствии с желаемой частотой квантования TKB управляющего сигнала Ny по времени (с учетом требований к качеству - точности и быстродействию - САР преобразователя):

f3 f4e 2fb/K3,

где fb частота выходного напряжения инвертора;

Кз 1,2,3,... - кратность частоты записи fa по отношению к частоте 1ь.

Значению Кз 1 соответствует максимальное значение тэтах 2ft, при котором в процессе регулирования инвертора не нарушается симметрия формируемых полуволн выходного напряжения и, следовательно, фаза формируемой волны не изменяется при регулировании даже в переходных режимах (условие постоянства фазы является необходимым условием включения источников переменного напряжений в режим параллельной работы). Значениям Кз 1 соответствует более низкое быстродействие. Для реализации дискретной САР необходимо осуществлять измерение действующего (для синусоидальных форм - среднего) значения напряжений (токов) в соответствии с выражениями

(t)dt

ТЬ/22

Ub cp 2fb/ Um Sin COb tdt Ј Um .

Q

На фиг. 10 приведены диаграммы работы блока задающего генератора для различных значений сигнала Ведущий/ведомый и видов неисправностей первого (а) и второго (б) опорных задающих генераторов (03Г), входящих в состав соответственно первого и второго преобразователей, включенных параллельно. Надписи Ведущий и Ведомый на фиг, 10 относятся к первому ОЗГ. На фиг. 10 обозначены: 52 (58, 64,70) - сигналы на первом входе мажоритарного элемента 27; 51 (57, 63, 69)- на втором его выходе; 53

(59, 6В, 71) - на третьем; 54 (60, 66, 72) - на выходе миноритарного элемента 27; 55 и 73 - ня инверсном вуходе одновибрэтора 30; 56 (62, 68, 74) - на выходе схемы ИЛИ 26; 61 и 6 / на инверсном выходе одноеибратора 29,

Однооибраторы с перезапуском настроены на генерацию имоульса длительностью (а - b - с d). Ирм выходе, из строя первого ОЗГ, выполняющего функции ведущего (который сопровождается недопустимым снижением частоты следования импульсов на первом входе элемента 27 или их исчеэно- вением,диаграмма 53), через интервал времени на инверсное выходе одновмбратора 30 появляется сигнал 55 высокого уровня, который мйрез схему ИЛИ 25 сбрасывает триггер 24 з ноль, из выходе схемы ИЛИ 26 появляется уровень логического нуля, переключается мультиплексор 23, на первый вхоц опемента в дальнейшем проходят импульсы sTODorc (смежного) СЗГ, загораются саетодиоды 3 i и 33, первый ОЗГ автора (ичьскм переводится Б резерв, первый преобразователь становится ведомым. На выходе элемента 27 сохраняется импульсная последовательность, совпадающая с 53, ropvrr сеетодиод 33, индицирующий о неис- прзвнзсти собственного ЗГ. При этом в блоке ЗГ 1 второго преобразователя происходит следующее,

До момента возникновения неисправности в ОЗГ первого преобразователя второй является ведомым. При, недопустимом снижении частоты следования или после исчезновения ммпульсов от смежного (перво- i о) ОЗГ на трет ьем входе элемента 27 через интервал зажигается саетодиод 32, на инверсном выходе одновибратора 29 появляется сигнал 61 высокого уровня, который через схему ИЛИ 28 переключает мультиплексор 23, гаснет светодиод 31, второй ОЗГ автоматически переводится в режим ведущего.

Для организации параллельной работы инвертора с сетью опорный ЗГ необходимо выполнить с использованием схемы ФАП 37 (фиг.6), содержащей генератор, управляемый напряжением,(ГУН) и фазовый компаратор (ФК) с фильтром низких частот (ФНЧ), куль-компаратора 34 с гистерезисом, управляемого ключа 36 и триггера 35 управления, делителя частоты с коэффициентом деления

Кд fo/fUcHOM

где fucHOM - номинальное значение частот ы напряжения сети Uc ГУН схемы ФАП 37. Таким образом, при одиночной работе

узел по фиг.6 генерирует импульсы со стабильной частотой Тгун fo, а при совместной работе - с частотой тгун Кд- fuc.

Сигнал с частотой f0 поступает на счетный вход счетчика 5 и тактовый вход цифрового фазового детектора 6. На выходах счетчика 5 формируется линейно нарастающая цифровая последовательность NCM (линейно во времени изменяется двоичное 0 разрядное число МСчг ). Цифровой фазовый детектор отрабатывает рассогласование фаз (между напряжениями ведущего источника и данного инвертора) только в режиме, когда рассматриваемый инвертор является

ведомым.

В режиме ведущего при включении питающего напряжения на выходах цифрового фазового детектора устанавливается нулевое значение смещения ЫФ2 0 (индекс 2 означает двоичную систему исчисления)и работа фазового детектора запрещается высоким уровнем сигнала Ведущий/ведо- м,ый на его управляющем входе. При этом на выходах сумматора 8 образуется несме5

щенная последовательность Noni

Won. NC42 + 0 МСч2.

8 режиме ведомого до момента включения в режим параллельной работы на выходах цифрового фазового детектора устанавливается кодовая комбинация, соответствующая числу - начальному смещению

фаз между напряжениями ведущего и рассматриваемого инверторов. Устройство цифрового фазового детектора, реализующее указанную функцию (фиг.7), содержит три триггера 39, 40 и 42, схему ИЛИ 43,

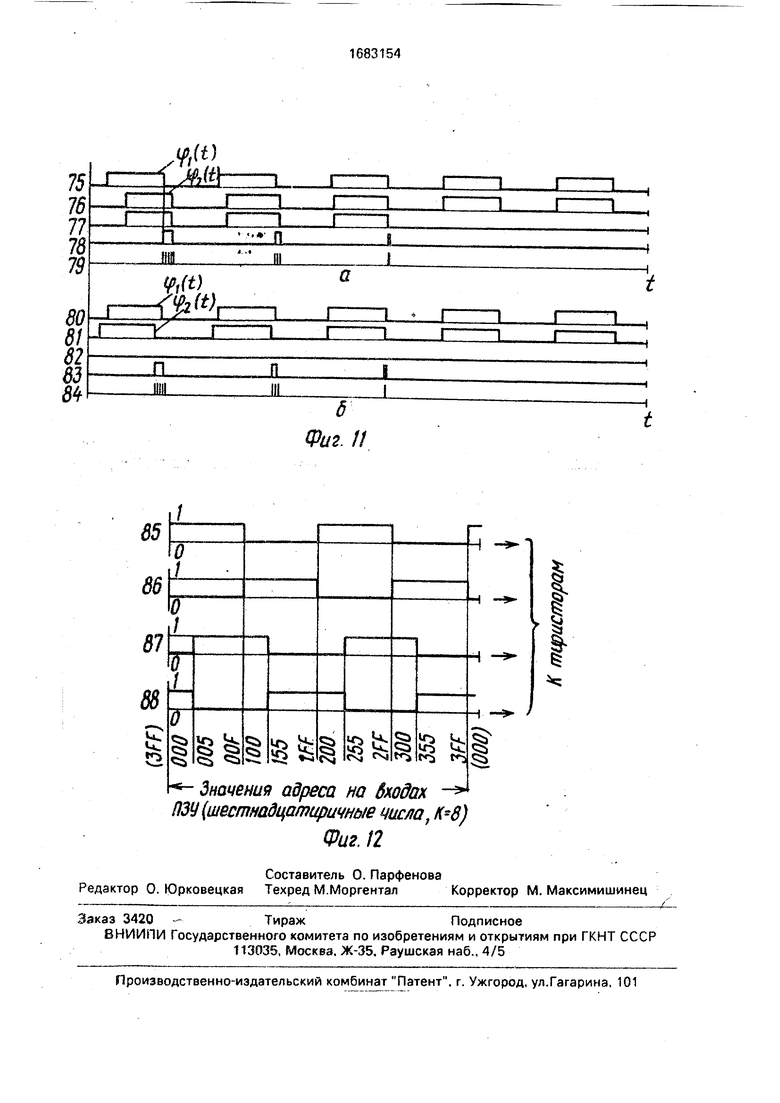

логическую схему 44, блок 45 совпадения и реверсивный счетчик 46. На фиг. 11 изображены диаграммы, поясняющие принцип работы детектора при опережающей фазе ведущего источника (а) и отстающей (б).На

фиг.11 обозначены: 76 (80) - сигнал на прямом выходе триггера 39; 76 (81) - на прямом выходе триггера 40; 77 (82) - на прямом выходе триггера 42; 78 (33) - на выходе логической схемы 44; 79 (84) - на выходе блока

45 совпадения (на счетном входе реверсивного счетчика). Выходные сигналы триггеров 39,40 и 42 управляют логической схемой 44 и входами направления счета реверсивного счетчика таким образом, что в режиме

фазовой подстройки и при опережающей фазе ведущего источника происходит слежение (цикл за циклом) числа импульсов, пропорционального временному сдвигу, с предыдущим содержимым счетчика, а при отстающей фазе ведущего источника - вычитание. Такой режим работы схемы продолжается до тех пор, пока не будет установлена нулевая разность фаз между напряжениями ведущего и ведомого инверторов - при равенстве фаз счетные импульсы на вход счетчика не проходят. Таким образом, в случае включения в режим параллельной работы двух однотипных инверторов при синхронизации от общего задающего генератора условие синхронной работы можно считать выполненным и производить включение. При включении в режим параллельно с сетью девиации частоты устраняются с помощью схемы ФАП в ОЗГ (фиг.6). На выходах счетчика (фазового детектора) устанавливается значение смещения NcD2 0, а на выходах сумматора 8 образуется смещенная последовательность Non:

Non2 N

сч2

Щ2.

Числа последовательности N0n поступают на вторые входы вычитателя 9 и сумматора 10, на первые входы которых подается числовое значение сигнала управления Ny в дополнительном коде, предварительно записанное в буферный регистр 7 с выходов цифрового блока 4 задания. Для осуществления регулирования угла управления инвертором в диапазоне 0...360 зл.град в соответствии с описанным способом для представления чисел кода управления от О до Nym2 достаточно К разрядов. Однако для обработки отрицательных значений управляющего сигнала в режиме реверса направления (фиг. 16) необходимо использовать представление чисел в двоичном дополнительном коде (фиг. 8). Поэтому цифровой блок задания имеет К+2 выходов и использован К+2-разрядный регистр 7.

На выходе вычитателя 9 и сумматора 10 образуются смещенные последовательности дь и 6с. Формирование указанных последовательностей происходит одинаково как для положительных значений сигнала управления (фиг. 1а), так и для отрицательных, соответствующих реверсу (фиг. 16) выходного напряжения благодаря представлению двоичных чисел в дополнительном коде.

Смещенные последовательности дь и (5С поступают на входы декодеров 13...15 блоков 11 и 12 формирования управляющих импульсов групп опережающих и запаздывающих рабочих ключей. Смысл терминов опережающий и запаздывающий рабочий ключ легко пояснить с помощью диаграммы фиг. 1. В частности, диаграммы

V11...V41 представляют последовательности импульсов управления для четырех одноименно обозначенных рабочих вентилей модуля 0° (фиг. 26, в) многоячейкового

инвертора. Из кривой формируемого напряжения UH на фиг,1 а, б видно, что в формировании положительной (отрицательной) полуволны на выходе модуля 0° участвуют рабочие ключи V11 и V4i одной диагонали, а

0 в формировании отрицательной (положительной соответственно) полуволны - рабочие ключи V2i и V3i.

При этом видно, что для 0 Ny Nym сигнал управления рабочим ключом Vh

5 (У21)опережает(с точки зрения происхождения событий в реальном времени) сигнал управления рабочим ключом V4i (V3i) нз угол у 180° -/3 , где/ - угон горения соответствующей пары ключей. Для

0 Nym Ny 0 сигнал управления ключом V11 (V2i) запаздывает по отношению к сигналу управления ключом V4i (V3i) на тот же угол у . Таким образом, опережение и запаздывание определяется между тиристо5 рами одноименной диагонали инверторного модуля относительно формируемого ею прямоугольника напряжения на выходе модуля. Поскольку коммутационные процессы в диагоналях и столбах инвертор0 ных ячеек происходят аналогично (с учетом сдвигов во времени), то все рабочие ключи инвертора можно разделить на группу опережающих и запаздывающих.

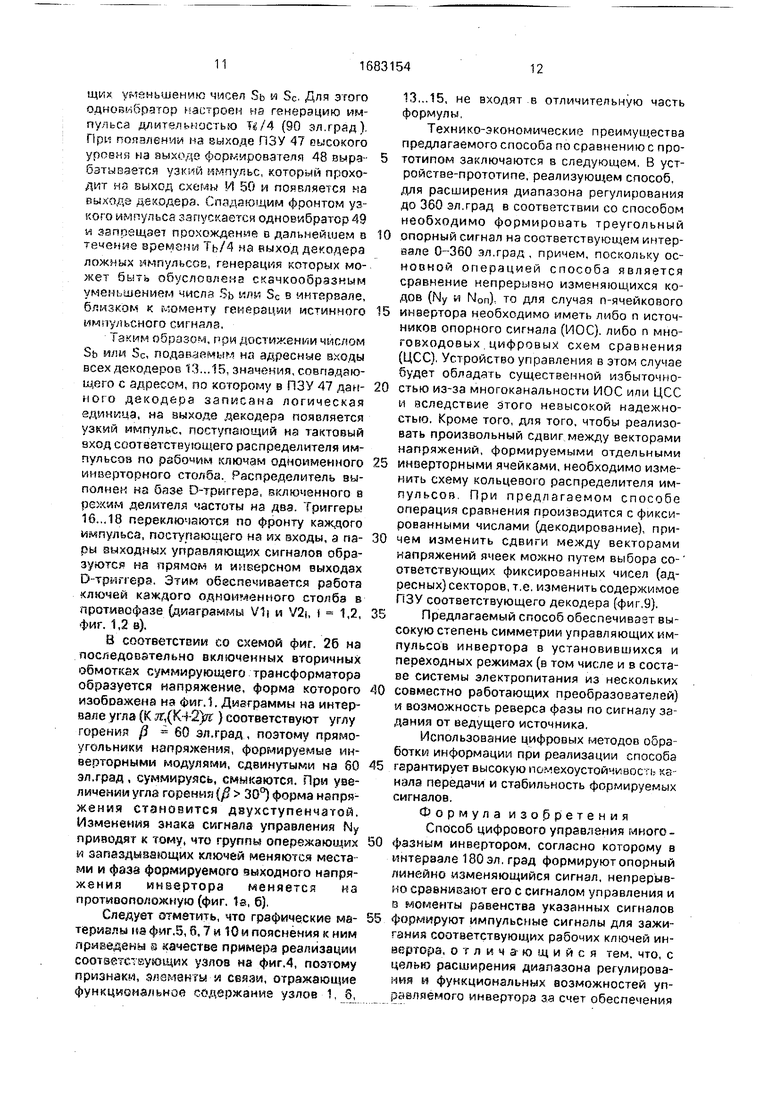

Основным составным элементом каж5 дого декодера (фиг.9) является неполный дешифратор, который легко выполняется на интегральном постоянном запоминающем устройстве объемом 2 + х1 бит. Во избежание ложного несрабатывания декодера при

0 скачкообразном изменении значения Ny, соответствующем увеличению числа Зь или Sc (моменты Кл(К+2)7Г на фиг.содержимое ПЗУ в зависимости от значения

КЧ-9

2 -разрядного адреса на его входе и но- 5 меров инверторного столба (для инвертора по фиг.2 б) должно иметь вид, изображенный диаграммами фиг. 12, Длина сектора, в ячейках которого записана логическая единица, соответствует максимально возмож- 0 ному изменению угла зажигания какого-либо ключа - на 90 эл.град. Помимо ПЗУ 47 декодер (фиг.9) содержит формирователь 48 короткого импульса, одновибра- тор 49 без перезапуска и схему И 50. 5 Формирователь 48. выделяет передний фронт импульса на выходе дешифратора. Узел из элементов 49 и 50 предохраняет от ложных срабатываний устройства при скачкообразных изменениях Ny, соответствующкх уменьшению чисел 5ь и Sc. Для этого одновибрэтор настроен на генерацию импульса длительностью (90 зл.град). При появлении на выходе ПЗУ 47 высокого уровня на формирователя 48 выра- бзтывается узкий м пупьс, который проходит на выход схемы И 50 и появляется на еыяоде декодера. Опадающим фронтом узкого импульса запускается одновибратор49 и запрещает прохождение о дальнейшем в течение времени Ть/4 на выход декодера ложных импульсов, генерация которых может быть обусловлена скачкообразным уменьшением числа 5ь MW Sc в интервале, близком к моменту генерации истинного импульсного сигнала.

Таким образом, г рм достижении числом Зь или Sc, подаваемым на адресные входы всех декодеров 13.,.15, значения, совпадающего с адресом, по которому в ПЗУ 47 дан- иого декодера записана логическая единица, на выходе декодера появляется узкий импульс, поступающий на тактовый зход соответствующего распределителя импульсов по рабочим ключам одноименного инверторного столба. Распределитель выполнен на базе D-триггера, включенного в режим делителя частоты на два. Триггеры 16.., 18 переключаются по фронту каждого импульса, поступающего на их входы, а пары выходных управляющих сигналов образуются на прямом и инверсном выходах D-триггера, Этим обеспечивается работа ключей каждого одноименного столба в протмаофазе (диаграммы V1i и V2i, f 1,2, Фиг. 1,2 в).

В соответствии со схемой фиг. 26 на последовательно включенных вторичных обмотках суммирующего трансформатора образуется напряжение, форма которого изобоажена на фиг. 1. Диаграммы на интервале угла (К зг,(К4-2)тг ) соответствуют углу горения / 60 зл.град, поэтому прямоугольники напряжения, формируемые ин- верторными модулями, сдвинутыми на 60 эл.град, суммируясь, смыкаются. При увеличении угла горения {// 30°) форма напря- жения становится двухступенчатой. Изменения знака сигнала управления Ny приводят к тому, что группы опережающих и запаздывающих ключей меняются местами и фаза формируемого выходного напря- жения инвертора меняется на противоположную (фиг. Is, б),

Следует отметить, что графические материалы на фиг.5, б, 7 и 10 и пояснения к ним приведены s качестве примера реализации соответствующих узлов на фиг.4, поэтому признаки, элементы и связи, отражающие функциональное содержание узлов 1, 6,

Технико-экономические преимущества предлагаемого способа по сравнению с прототипом заключаются в следующем, В устройстве-прототипе, реализующем способ, для расширения диапазона регулирования до 360 зл.град в соответствии со способом необходимо формировать треугольный

0 опорный сигнал на соответствующем интервале 0-360 эл.град , причем, поскольку основной операцией способа является сравнение непрерывно изменяющихся кодов (Ny и Мол), то для случая п-ячейкового

5 инвертора необходимо иметь либо п источников опорного сигнала (ИОС). либо п мно- говходовых цифровых схем сравнения (ЦСС), Устройство управления в этом случае будет обладать существенной избыточно0 стью из-за многоканальное™ HOC ипи ЦСС и вследствие этого невысокой надежностью. Кроме того, для того, чтобы реализовать произвольный сдвиг между векторами напряжений, формируемыми отдельными

5 инверторными ячейками, необходимо изменить схему кольцевого распределителя импульсов При предлагаемом способе операция сравнения производится с фиксированными числами (декодирование), при0 чем изменить сдвиги между векторами напряжений ячеек можно путем выбора со- ответствующих фиксированных чисел (адресных) секторов, т.е. изменить содержимое ПЗУ соответствующего декодера (фиг,9).

5 Предлагаемый способ обеспечивает высокую степень симметрии управляющих импульсов инвертора в установившихся и переходных режимах (в том числе и в составе системы электропитания из нескольких

0 совместно работающих преобразователей) и возможность реверса фазы по сигналу задания от ведущего источника.

Использование цифровых методов оора ботки информации при реализации способа

5 гарантирует высокую помехоустойчивость ка - нала передачи и стабильность формируемых сигналов.

Формула изобретения Способ цифрового управления много0 фазным инвертором, согласно которому в интервале 180эл,грэд формируют опорный линейно изменяющийся сигнал, непрерывно сравнивают его с сигналом управления и D моменты равенства указанных сигналов

5 формируют импульсные сигналы для зажигания соответствующих рабочих ключей инвертора, отличающийся тем. что, с целью расширения диапазона регулирования и функциональных возможностей управляемого инвертора за счет обеспечения

режима регулирования фазы колебаний выходного напряжения инвертора относительно внешнего управляющего синхросигнала, опорный линейно нарастающий сигнал формируют втечение времени, равного периоду выходного напряжения инвертора, непрерывно производят вычитание сигнала управления из опорного линейно нарастающего сигнала и по величине полученной разности определяют моменты зажигания соответствующих опережающих (запаздывающих) рабочих ключей многофазного инвертора при положительных значениях управляющегосигнала а

Фиг/

0

(отрицательных значениях управляющего сигнала, т.е. при реверсе выходного напряжения), непрерывно суммируют опорный и управляющий сигналы и по величине полученной суммы определяют моменты зажигания запаздывающих (опережающих) рабочих ключей многофазного инвертора при положительных (отрицательных) значениях управляющего сигнала, причем фазу опорного линейно изменяющегося сигнала определяют пропорционально начальному сдвигу фаз между внешним управляющим синхросигналом и выходным напряжением инвертора.

Ф1

иг о

R Q

4

Риг.6

т

ID

со

оо

О

nnfafigag пюыодад

| Цифровое многоканальное устройство для управления инвертором | 1982 |

|

SU1037415A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-10-07—Публикация

1989-06-05—Подача