Изобретение относится к области вычислительной техники и предназначено для использования в системах преобразования перемещения в цифровой код.

Известны преобразователи перемещения - код, они содержат кодирующий элемент с нанесенным на него двоичным кодом и контрольными разрядами, головки считывания прямого и обратного кода и сумматоры по модулю «2, выходы которых соединены со входом декодирующего устройства. Однако эти преобразователи не обеспечивают достаточной надежности работы из-за большого количества контрольных разрядов и объема декодирующей аппаратуры.

Отличием описываемого устройства является то, что оно содержит дополнительные головки считывания обратного кода контрольных разрядов, сдвинутые относительно основных на нечетное число длин элементарных участков, занимаемых старшим информационным разрядом. Выходы этих головок соединены со входами сумматоров по модулю «2 непосредственно и через инверторы соответственно при нечетном и четном числах информационных разрядов, используемых для образования контрольных разрядов. Это обеспечивает повыщение надежности работы преобразователя.

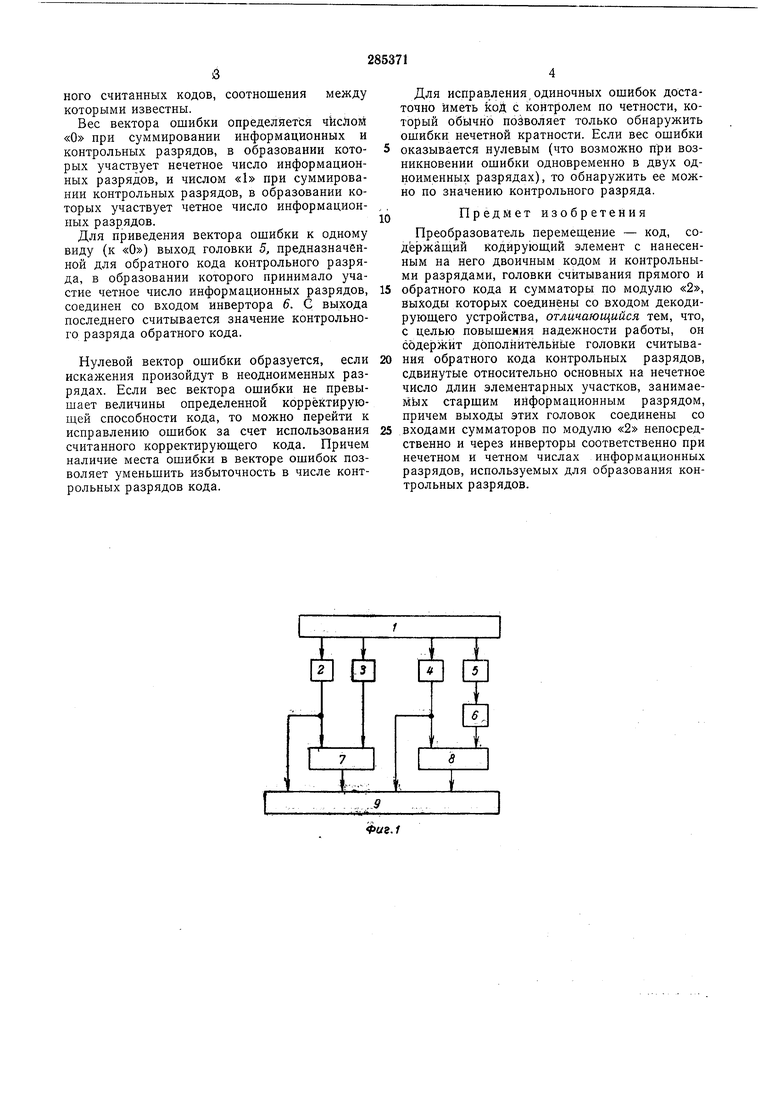

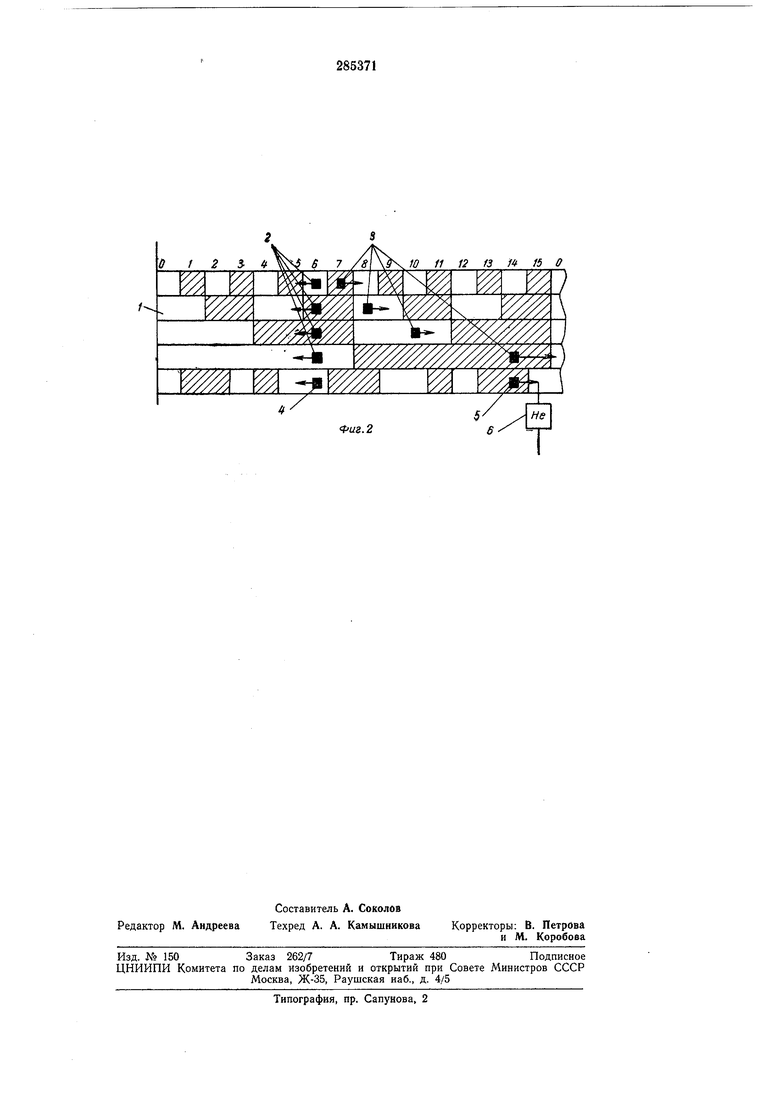

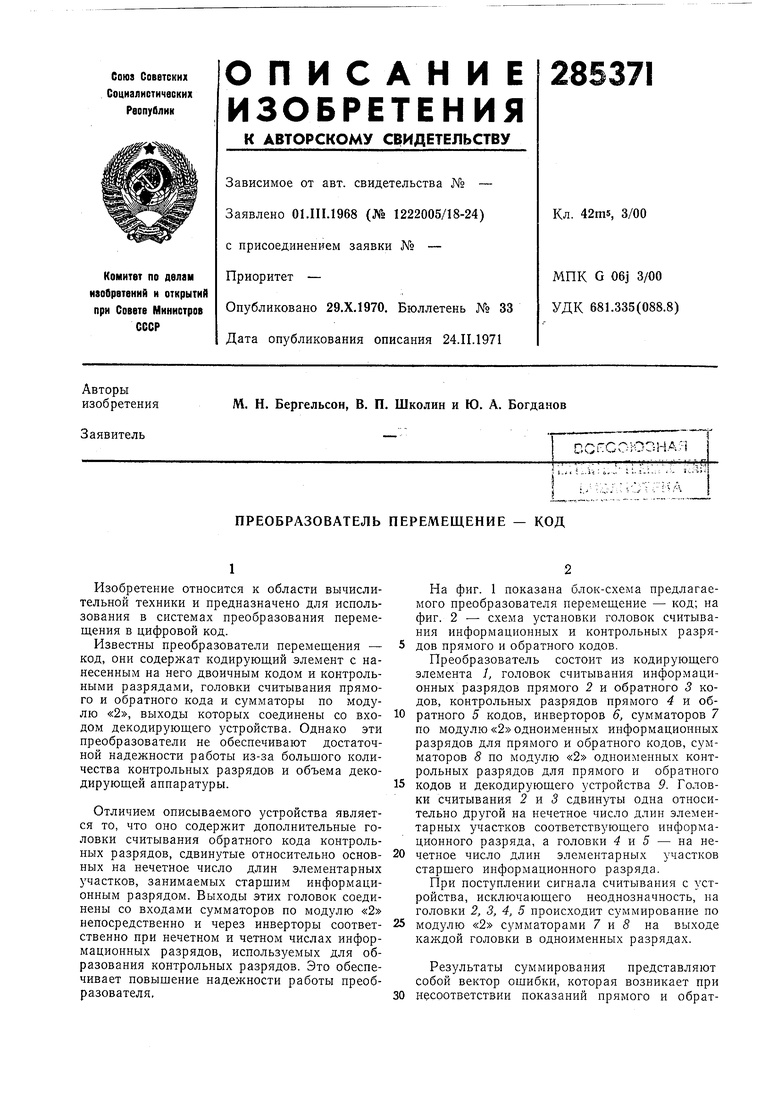

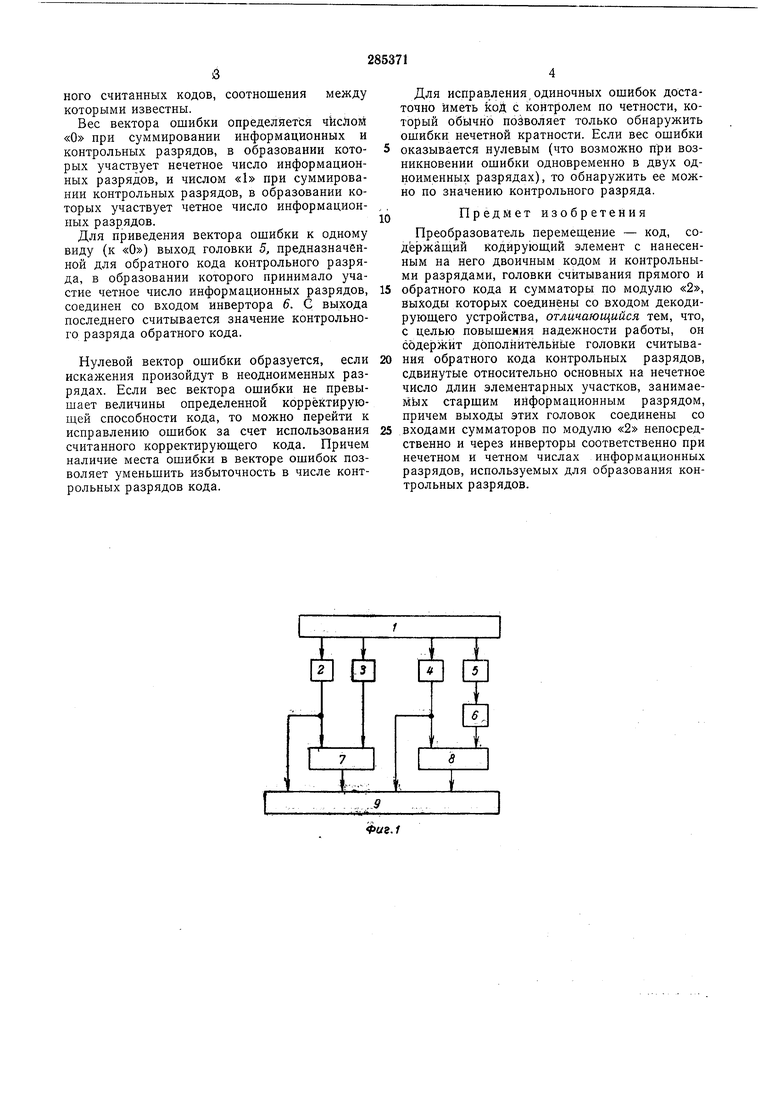

На фиг. 1 показана блок-схема предлагаемого преобразователя перемещение - код; на фиг. 2 -- схема установки головок считывания информационных и контрольных разрядов прямого и обратного кодов.

Преобразователь состоит из кодирующего элемента 1, головок считывания информационных разрядов прямого 2 и обратного 3 кодов, контрольных разрядов прямого 4 и обратного 5 кодов, инверторов 6, сумматоров 7 по модулю «2 одноименных информационных разрядов для прямого и обратного кодов, сумматоров 8 по модулю «2 одноименных контрольных разрядов для прямого и обратного кодов и декодирующего устройства 9. Головки считывания 2 и 5 сдвинуты одна относительно другой на нечетное число длин элементарных участков соответствующего информационного разряда, а головки 4 и 5 - на нечетное число длин элементарных участков старшего информационного разряда.

При поступлении сигнала считывания с устройства, исключающего неоднозначность, на головки 2, 3, 4, 5 происходит суммирование по модулю «2 сумматорами 7 и 5 на выходе каждой головки в одноименных разрядах.

ного считанных кодов, соотношения между которыми известны.

Вес вектора ошибки определяется чйсЛой «О при суммировании информационных и контрольных разрядов, в образовании которых участвует нечетное число информационных разрядов, и числом «1 при суммировании контрольных разрядов, в образовании которых участвует четное число информационных разрядов.

Для приведения вектора ошибки к одному виду (к «О) выход головки 5, предназначенной для обратного кода контрольного разряда, в образовании которого принимало участие четное число информационных разрядов, соединен со входом инвертора 6. G выхода последнего считывается значение контрольного разряда обратного кода.

Нулевой вектор ошибки образуется, если искажения произойдут в неодноименных разрядах. Если вес вектора ошибки не превышает величины определенной корректирующей способности кода, то можно перейти к исправлению ошибок за счет использования считанного корректируюшего кода. Причем наличие места ошибки в векторе ошибок позволяет уменьшить избыточность в числе контрольных разрядов кода.

Для исправления, одиночных ошибок достаточно иметь йоД с контролем по четности, который обычно позволяет только обнаружить ошибки нечетной кратности. Если вес ошибки оказывается нулевым (что возможно при возникновении ошибки одновременно в двух одноименных разрядах), то обнаружить ее можно по значению контрольного разряда.

Предмет изобретения

Преобразователь перемещение - код, содержащий кодирующий элемент с нанесенным на него двоичным кодом и контрольными разрядами, головки считывания прямого и

обратного кода и сумматоры по модулю «2, выходы которых соединены со входом декодирующего устройства, отличающийся тем, что, с целью повышения надежности работы, он содержит дополнительные головки считывания обратного кода контрольных разрядов, сдвинутые относительно основных на нечетное число длин элементарных участков, занимаемых старшим информационным разрядом, причем выходы этих головок соединены со входами сумматоров по модулю «2 непосредственно и через инверторы соответственно при нечетном и четном числах информационных разрядов, используемых для образования контрольных разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО | 2004 |

|

RU2297036C2 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2014 |

|

RU2542665C1 |

| САМОКОНТРОЛИРУЮЩЕЕСЯ УСТРОЙСТВО | 2004 |

|

RU2297028C2 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297034C2 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 2004 |

|

RU2297029C2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2297035C2 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297030C2 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2297032C2 |

| Устройство для обнаружения и коррекции ошибок памяти | 1986 |

|

SU1377918A1 |

и ш

f 2 З t

Ю 11 12 13 /« /5 О

ZZ

w/m/////m.

V77/

Л

Даты

1970-01-01—Публикация