Изобретение относится к вычислительной технике. Известно устройство хранения и передачи данных с исправлением ошибок в байте информации и обнаружением ошибок в байтах информации (Патент на изобретение №2534499 «Устройство хранения и передачи данных с исправлением ошибок в двух байтах информации» авторы: Борисов К.Ю., Павлов А.А., Царьков А,Н., Хоруженко О.В., Гусев А.В. от 25.04.2013 г.), содержащие узел памяти, входной блок кодирования, выходной блок кодирования, блок вычисления синдрома ошибки, дешифратор, корректор, блок элементов И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы отличающееся тем, что дополнительно содержит блок хранения векторов ошибок, вход установки в нулевое состояние, вход записи, вход считывания, адресные входы, подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, вход синхронизации подключен к пятому входу узла памяти и к первому входу блока элементов И, информационные входы подключены к шестым входам узла памяти и к входам входного блока кодирования который, формирует значения контрольных разрядов  ,

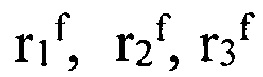

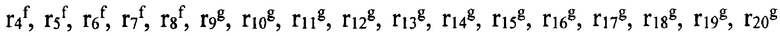

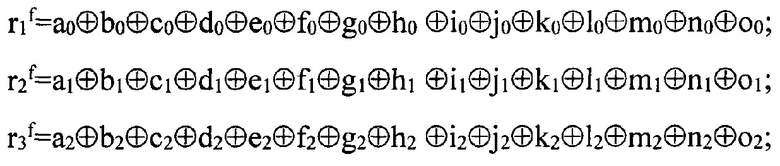

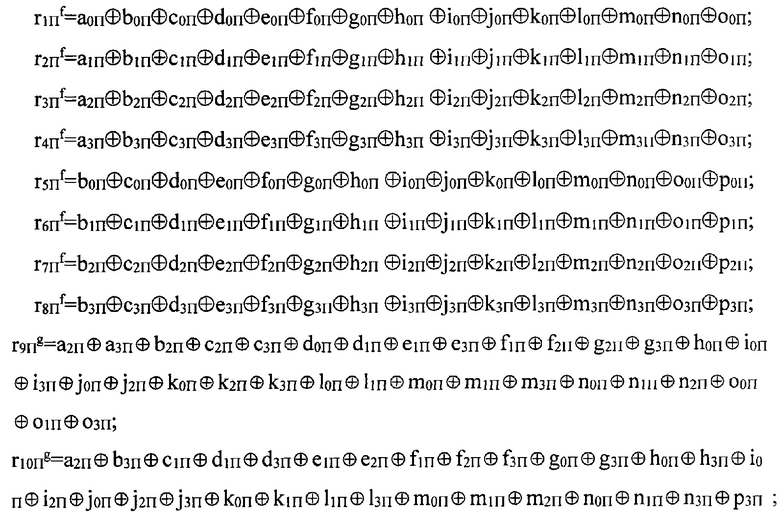

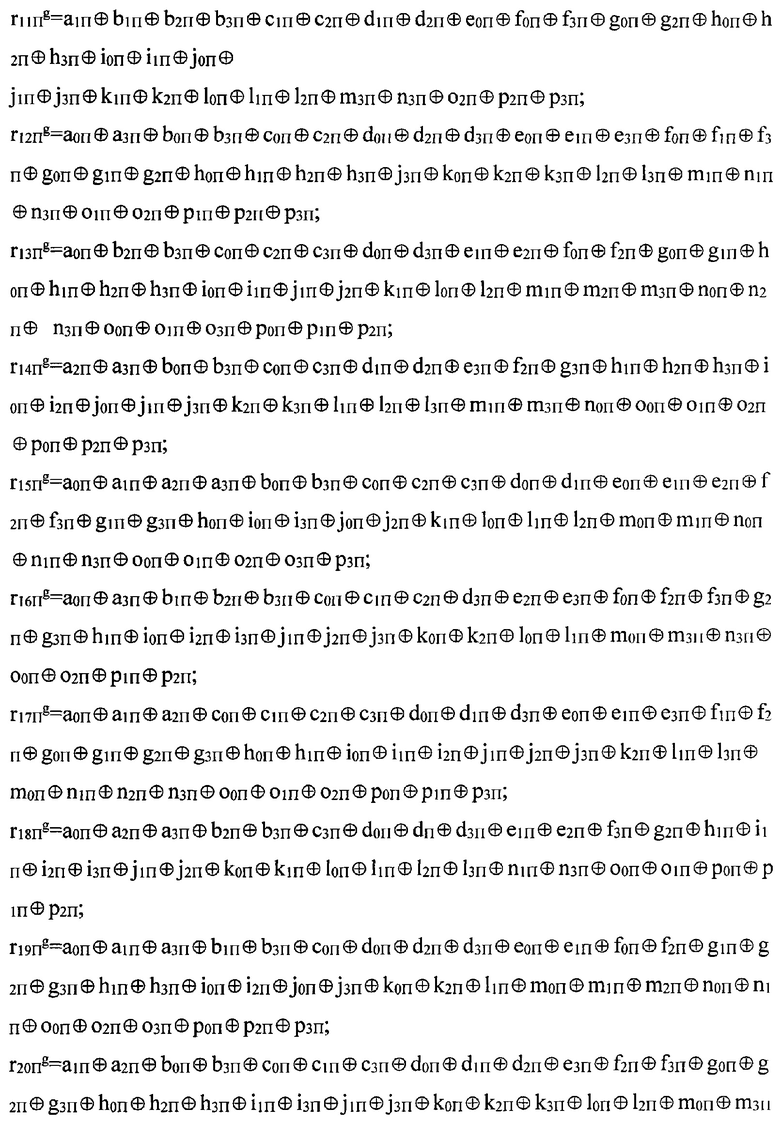

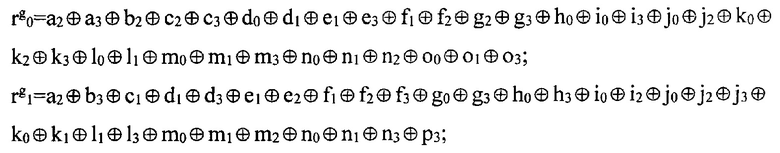

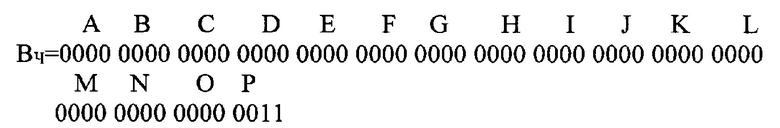

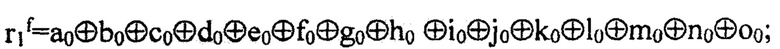

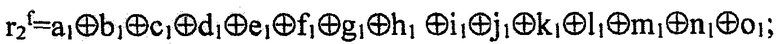

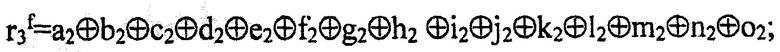

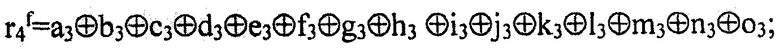

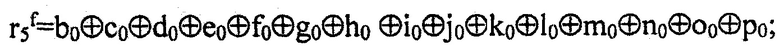

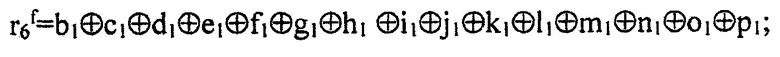

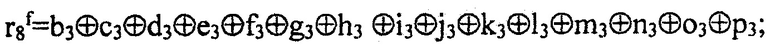

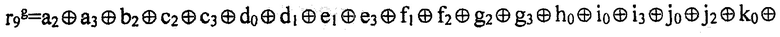

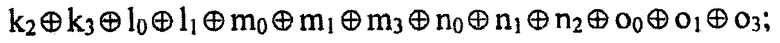

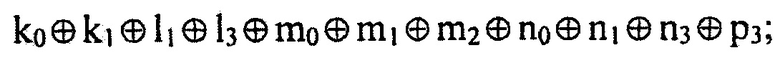

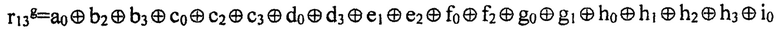

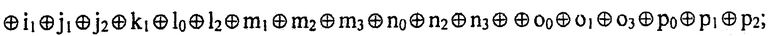

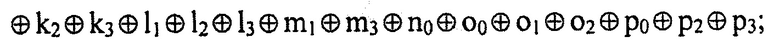

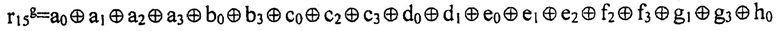

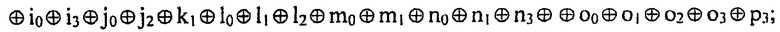

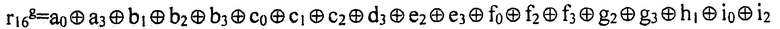

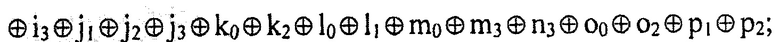

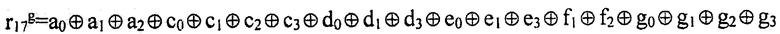

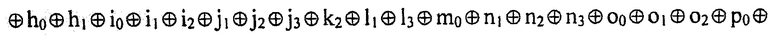

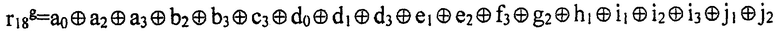

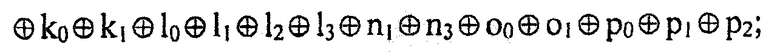

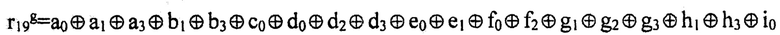

,  , путем сложения по модулю 2 информационных символов а0 a1 а2 а3, b0 b1 b32b3, с0 c1c2c3, d0 d1 d2 d3, e0 e1 e2 е3, f0 f1 f2 f3, g0 g1 g2 g3, h0 h1 h2 h3, i0 i1 i2 i3, j0 j1 j2 j3, k0 k1 k2 k3, l0 l1 l2 l3, m0 m1 m2 m3, n0 n1 n2 n3, o0 o1 o2 o3, p0 p1 p2 р3, поступающих на входы входного блока кодирования, в соответствии с правилом:

, путем сложения по модулю 2 информационных символов а0 a1 а2 а3, b0 b1 b32b3, с0 c1c2c3, d0 d1 d2 d3, e0 e1 e2 е3, f0 f1 f2 f3, g0 g1 g2 g3, h0 h1 h2 h3, i0 i1 i2 i3, j0 j1 j2 j3, k0 k1 k2 k3, l0 l1 l2 l3, m0 m1 m2 m3, n0 n1 n2 n3, o0 o1 o2 o3, p0 p1 p2 р3, поступающих на входы входного блока кодирования, в соответствии с правилом:

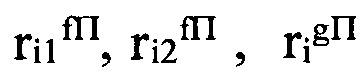

выходы входного блока кодирования подключены к седьмым входам узла памяти, информационные выходы узла памяти подключены соответственно к первым входам корректора и к входам выходного блока кодирования, который формирует значения проверочных контрольных разрядов

выходы входного блока кодирования подключены к седьмым входам узла памяти, информационные выходы узла памяти подключены соответственно к первым входам корректора и к входам выходного блока кодирования, который формирует значения проверочных контрольных разрядов

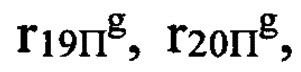

путем сложения по модулю 2 информационных символов а0П а1П а2П а3П, b0П b1П b2П b3П, с0П с1Пс2Пс3П, d0П d1П d2П d3П, е0П е1П е2 Пе3П, f0П f1П f2П f3П, g0П g1П g2П g3П, h0П h1П h2П h3П, i0П i1П i2П i3П, j0П j1П j2П j3П, k0П k1П k2П k3П, l0П l1П l2П l3П, m0П m1П m2П m3П, n0П n1П n2П n3П, о0П о1П о2П о3П, р0П p1П р2П р3П, поступающих на входы входного блока кодирования с информационных выходов узла памяти, в соответствии с правилом:

путем сложения по модулю 2 информационных символов а0П а1П а2П а3П, b0П b1П b2П b3П, с0П с1Пс2Пс3П, d0П d1П d2П d3П, е0П е1П е2 Пе3П, f0П f1П f2П f3П, g0П g1П g2П g3П, h0П h1П h2П h3П, i0П i1П i2П i3П, j0П j1П j2П j3П, k0П k1П k2П k3П, l0П l1П l2П l3П, m0П m1П m2П m3П, n0П n1П n2П n3П, о0П о1П о2П о3П, р0П p1П р2П р3П, поступающих на входы входного блока кодирования с информационных выходов узла памяти, в соответствии с правилом:

выходы выходного блока кодирования подключены к первым входам блока вычисления синдрома ошибки, к вторым входам которого, подключены выходы контрольных разрядов узла памяти, выходы блока вычисления синдрома ошибки подключены к входам дешифратора выходы которого, подключены к входам блока хранения векторов ошибок, выходы блока хранения векторов ошибок подключены к вторым входам корректора выходы которого, подключены к вторым входам блока элементов И, выходы блока элементов И являются выходами устройства.

выходы выходного блока кодирования подключены к первым входам блока вычисления синдрома ошибки, к вторым входам которого, подключены выходы контрольных разрядов узла памяти, выходы блока вычисления синдрома ошибки подключены к входам дешифратора выходы которого, подключены к входам блока хранения векторов ошибок, выходы блока хранения векторов ошибок подключены к вторым входам корректора выходы которого, подключены к вторым входам блока элементов И, выходы блока элементов И являются выходами устройства.

Недостатком устройства является ограниченная область его применения, так как оно не позволяет корректировать ошибки в устройствах обработки информации.

Наиболее близким по техническому решению является процессор повышенной достоверности функционирования (Патент на изобретение №2439667 «Процессор повышенной достоверности функционирования» / / Бобков С.Г., Осипенко П.Н., Павлов А.А., Павлов П.А., Павлов А.А., Хоруженко О.В., Царьков А.Н., от 08.07.2010 г.), содержащий управляющий узел, операционный узел, первые входы управляющего узла является входами процессора, вторая группа входов управляющего узла подключена к первым выходам операционного узла, выходы управляющего узла подключены к первым входам операционного узла, вторые входы которого являются входами данных, а вторые выходы являются выходами данных, отличающееся тем, что он дополнительно содержит дешифратор кода операции, генератор тактовых импульсов, блок управления, первый коммутатор, второй коммутатор, третий коммутатор, счетчик команд, счетчик сдвигов, регистр адреса, регистр числа, регистр сумматора, регистр дополнительный, регистр дополнительного кода, сумматор, блок контроля, управляющую память, блок логических операций и контроля, включающий блок логического сложения по mod2, блок инвертирования, блок логического сложения, блок логического умножения, функциональную схему формирования поправки при выполнении арифметических операций, функциональную схему формирования поправки при выполнении операции ИЛИ, функциональную схему формирования поправки при выполнении операции И, функциональную схему формирования поправки при выполнении операции сдвига, элемент задержки, первый блок элементов неравнозначности, второй блок элементов неравнозначности, третий блок элементов неравнозначности, первый блок элементов ИЛИ, второй блок элементов ИЛИ, блок кодирования, первый блок элементов И, второй блок элементов И, элемент И, выходы устройства обмена подключены к первому входу блока управления и к первому входу второго коммутатора, вторые входы которого подключены к выходам запоминающего устройства, первые выходы второго коммутатора поступают на вход устройства обмена, вторые выходы поступают на вход запоминающего устройства, а третьи выходы подключены соответственно к первым входам счетчика команд, счетчика сдвигов, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к входам дешифратора кода операции, к вторым входам блока управления, к первому входу первого коммутатора, первый выход которого подключ6ен к первому входу регистра адреса, третий вход блока управления подключен к выходам дешифратора кода операции а четвертый вход подключен к выходам генератора тактовых импульсов, а пятый вход подключен к первому выходу управляющей памяти, первый выход блока управления подключен к входу управляющей памяти, первые выходы которой подключены к первым входам блока контроля, второй выход блока управления подключен к второму входу первого коммутатора, третьи и четвертые входы которого подключены соответственно к выходам регистра адреса и счетчика команд, а с второго выхода снимается адрес ячейки памяти запоминающего устройства, третий выход блока управления подключен соответственно к вторым входам блока контроля, к вторым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к первой группе входов блока логических операций и контроля и является выходом синхроимпульсов, второй, третий, четвертый пятый выходы управляющей памяти подключены к третьим и четвертым пятым и шестым входам блока контроля при этом второй выход подключен к четвертому входу второго коммутатора, а третьи, четвертые и пятые выходы блока управляющей памяти подключены соответственно к третьим, четвертым пятым и шестым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к первой группе входов блока логических операций и контроля и являются выходам управляющих сигналов, сигналов считывания, сигналов записи, сигналов установки устройств в нулевое состояние, шестой выход блока управляющей памяти подключен к пятому входу блока управления, выходы регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода подключены к вторым входам третьего коммутатора и к пятым входам второго коммутатора, выход счетчика сдвигов подключен к шестым входам второго коммутатора, первые выходы третьего коммутатора подключены соответственно к входам сумматора и к вторым входам блока логических операций и контроля, выходы сумматора подключены к третьим входам блока логических операций и контроля, вторые, третьи, четвертые, пятые, шестые, седьмые и восьмые выходы третьего коммутатора подключены к четвертым, пятым, шестым, седьмым, восьмым, девятым и десятым входам блока логических операций и контроля, выходы которого подключены к седьмым, восьмым и девятым входам второго коммутатора.

Недостатком устройства является недостаточная отказоустойчивость процессора, так как не обеспечивается коррекция возникающих ошибок.

Задачей изобретения является коррекция ошибок в двух байтах информации, возникающих в процессоре ЭВМ при выполнении арифметических и логических операций, например, из-за отсутствия или возникновения лишних переносов.

Сущность изобретения заключается в том, что процессор, содержащий, управляющий узел, операционный узел, дешифратор кода операции, генератор тактовых импульсов, блок управления, первый коммутатор, второй коммутатор, третий коммутатор, счетчик команд, счетчик сдвигов, регистр адреса, регистр числа, регистр сумматора, регистр дополнительный, регистр дополнительного кода, сумматор, блок логических операций и контроля, включающий блок логического сложения по mod2, блок инвертирования, блок логического сложения, блок логического умножения, функциональную схему формирования поправки при выполнении арифметических операций, функциональную схему формирования поправки при выполнении операции ИЛИ, функциональную схему формирования поправки при выполнении операции И, функциональную схему формирования поправки при выполнении операции сдвига, элемент задержки, первый блок элементов неравнозначности, второй блок элементов неравнозначности, третий блок элементов неравнозначности, первый блок элементов ИЛИ, второй блок элементов ИЛИ, блок кодирования, первый блок элементов И, второй блок элементов И, элемент И, первый, вторые, третьи, четвертые, пятые входы блока логических операций и контроля, первые, вторые, третьи выходы блока логических операций и контроля, управляющую память, входы от устройства обмена, входы данных из запоминающего устройства, выход на устройство обмена, выходы данных на запоминающее устройство, выход адрес запоминающего устройства, выходы синхроимпульсов, выходы для сигналов управления, выходы для команды считывание, выходы для сигналов записи, выходы для сигналов установки в нулевое состояние, выходы устройства обмена подключены к первому входу блока управления и к первому входу второго коммутатора, вторые входы которого подключены к выходам запоминающего устройства, первые выходы второго коммутатора поступают на вход устройства обмена, вторые выходы поступают на вход запоминающего устройства, а третьи выходы подключены соответственно к первым входам счетчика команд, счетчика сдвигов, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к входам дешифратора кода операции, к вторым входам блока управления, к первому входу первого коммутатора, первый выход которого подключен к первому входу регистра адреса, третий вход блока управления подключен к выходам дешифратора кода операции, а четвертый вход подключен к выходам генератора тактовых импульсов, а пятый вход подключен к первому выходу управляющей памяти, первый выход блока управления подключен к входу управляющей памяти, второй выход блока управления подключен к второму входу первого коммутатора, третьи и четвертые входы которого подключены соответственно к выходам регистра адреса и счетчика команд, а с второго выхода снимается адрес ячейки памяти запоминающего устройства, третий выход блока управления подключен к вторым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к первому входу блока логических операций и контроля и является входом синхроимпульсов, вторые, третьи, четвертые и пятые выходы блока управляющей памяти подключены соответственно к третьим, четвертым пятым и шестым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к вторым входам блока логических операций и контроля и являются выходами управляющих сигналов, сигналов считывания, сигналов записи, сигналов установки устройств в нулевое состояние, выходы регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода подключены к вторым входам третьего коммутатора и к четвертым входам второго коммутатора, выход счетчика сдвигов подключен к пятым входам второго коммутатора, первые выходы третьего коммутатора подключены соответственно к входам сумматора и к третьим входам блока логических операций и контроля, выходы сумматора подключены к четвертым входам блока логических операций и контроля, вторые выходы третьего коммутатора подключены к пятым входам блока логических операции и контроля, отличающееся тем, что он дополнительно содержит дешифратор, блок элементов ИЛИ, блок элементов И, корректор, блок памяти, причем первые выходы блока логических операций и контроля подключены к первым входам корректора, вторые выходы подключены к шестым входам второго коммутатора, третьи выходы блока логических операций и контроля подключены к входам дешифратора, первая группа выходов которого подключена к входам блока памяти, выходы блока памяти подключены к первым входам блока элементов И, второй вход которого подключен к третьему выходу блока управления, а выход подключен к второму входу корректора, выходы корректора подключены к седьмым входам второго коммутатора, вторая группа выходов дешифратора подключена к входам блока элементов ИЛИ, выход которого подключен к восьмому входу второго коммутатора.

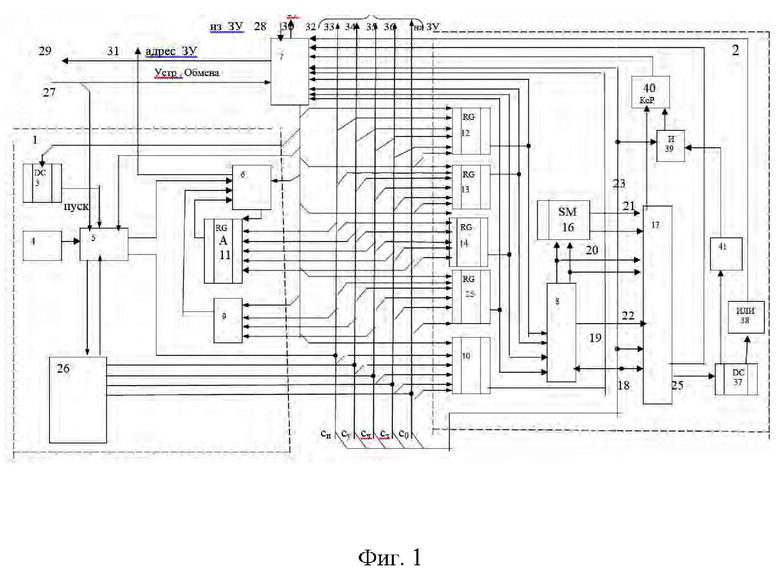

Процессор (фиг. 1) содержит управляющий узел 1, операционный узел 2, дешифратор 3 кода операции, генератор 4 тактовых импульсов, блок 5 управления, первый коммутатор 6, второй коммутатор 7, третий коммутатор 8, счетчик 9 команд, счетчик 10 сдвигов, регистр 11 адреса, регистр 12 числа, регистр 13 сумматора, регистр 14 дополнительный, регистр 15 дополнительного кода, сумматор 16, блок 17 логических операций и контроля, первый 18, второй 19, третий 20, четвертый 21, пятый 22 входы блока 17 логических операций и контроля, первый 23, второй 24, третий 25 выходы блока 17 логических операций и контроля, управляющая память 26, входы 27 устройства обмена, входы 28 данные из запоминающего устройства, выход 29 на устройство обмена, выходы 30 данные на запоминающее устройство, выход 31 адрес запоминающего устройства, выходы 32 синхроимпульсов, выходы 33 для сигналов управления, выходы 34 для команды считывание, выходы 35 для сигналов записи, выходы 36 для сигналов установки в нулевое состояние, дешифратор 37, блок 38 элементов ИЛИ, блок 39 элементов И, корректор 40, блок 41 памяти.

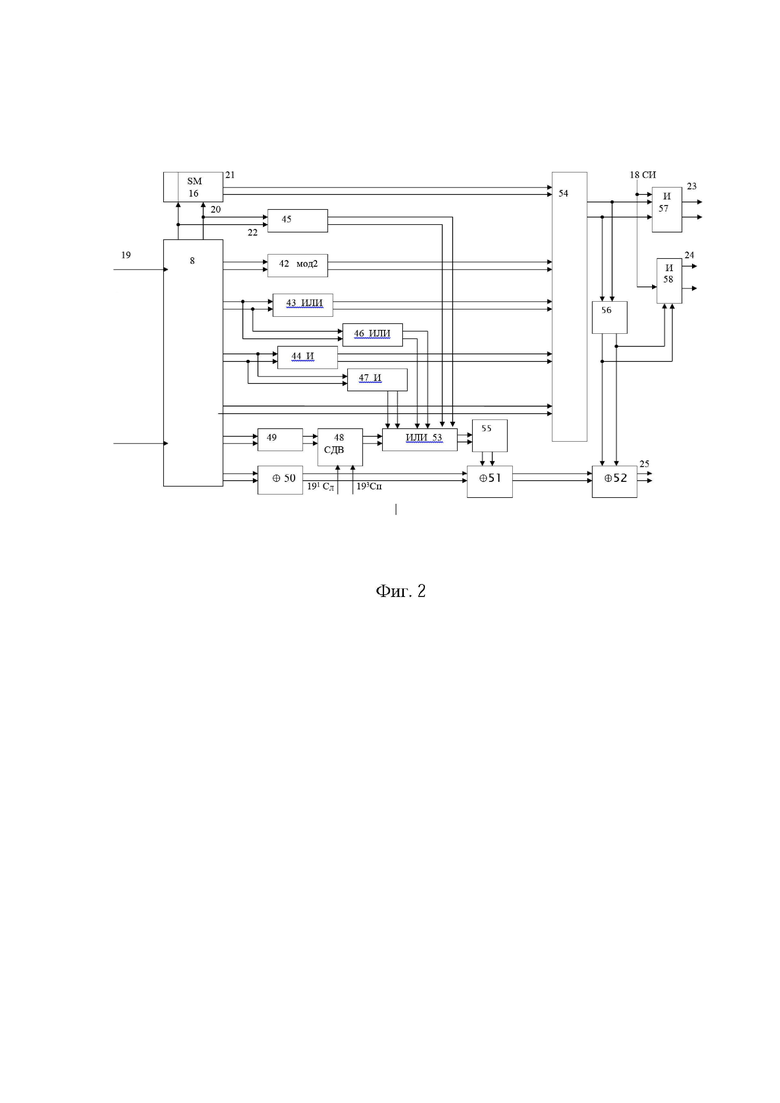

Блок 17 логических операций и контроля (фиг. 2) содержит блок 42 сложения по mod2, блок 43 логического сложения, блок 44 логического умножения, функциональную схему 45 формирования поправки при выполнении арифметических операций, функциональную схему 46 формирования поправки при выполнении операции ИЛИ, функциональную схему 47 формирования поправки при выполнении операции И, функциональную схему 48 формирования поправки при выполнении операции сдвига, элемент 49 задержки, первый блок 50 элементов неравнозначности, второй блок 51 элементов неравнозначности, третий блок 52 элементов неравнозначности, первый блок 53 элементов ИЛИ, второй блок 54 элементов ИЛИ, первый блок 55 кодирования, второй блок 56 кодирования, первый блок 57 элементов И, второй блок 58 элементов И.

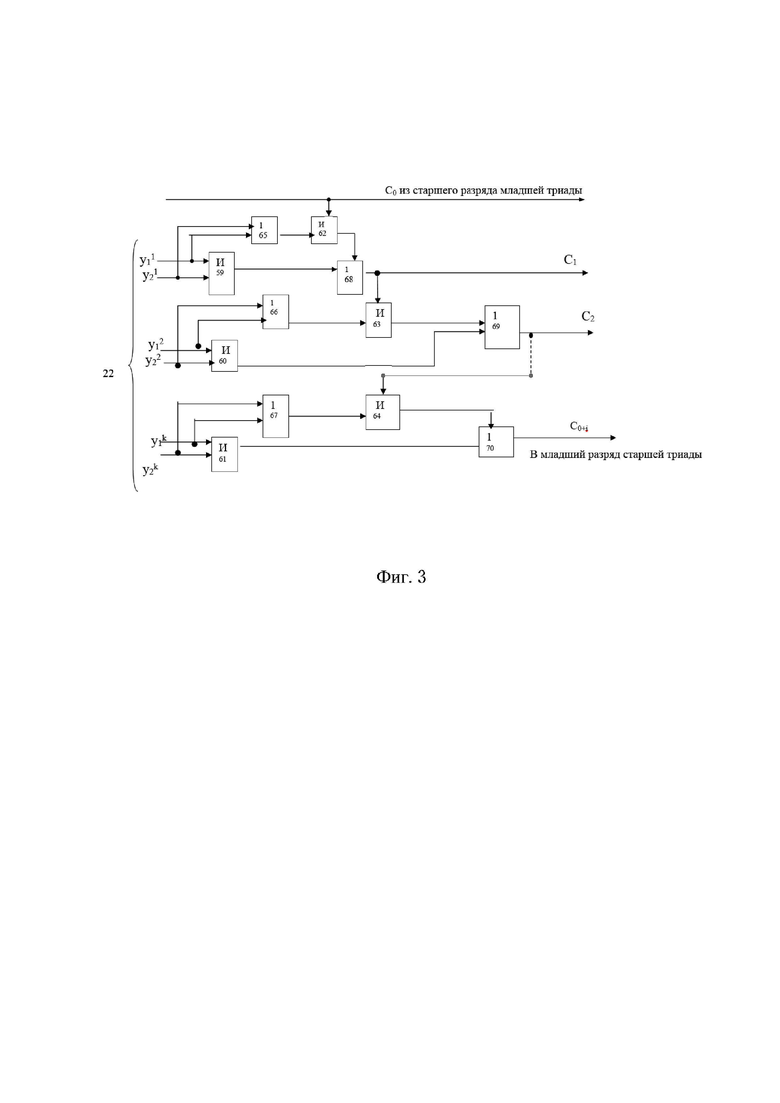

Функциональная схема 45 формирования поправки при выполнении арифметических операций (фиг. 3) содержит первый элемент 59 И, второй элемент 60 И, третий элемент 61 И, четвертый элемент 62 И, пятый элемент 63 И, шестой элемент 64 И, первый элемент 65 ИЛИ, второй элемент 66 ИЛИ, третий элемент 67 ИЛИ, четвертый элемент 68 ИЛИ, пятый элемент 69 ИЛИ, шестой элемент 70 ИЛИ.

Функциональная схема 48 формирования поправки при выполнении операции сдвига.

Выходы 27 устройства обмена подключены к первому входу блока 5 управления и к первому входу второго коммутатора 7, вторые входы 28 которого подключены к выходам запоминающего устройства, первые выходы второго коммутатора 7 поступают на вход 29 устройства обмена, вторые выходы поступают на вход запоминающего устройства, а третьи выходы подключены соответственно к первым входам счетчика 9 команд, счетчика 10 сдвигов, регистра 12 числа, регистра 13 сумматора, регистра 14 дополнительного, регистра 15 дополнительного кода, к входам дешифратора 3 кода операции, к вторым входам блока 5 управления, к первому входу первого коммутатора 6, первый выход которого подключ6ен к первому входу регистра 11 адреса, третий вход блока 5 управления подключен к выходам дешифратора 3 кода операции, а четвертый вход подключен к выходам генератора 4 тактовых импульсов, а пятый вход подключен к первому выходу управляющей памяти 26, первый выход блока 5 управления подключен к входу управляющей памяти 26, второй выход блока 5 управления подключен к второму входу первого коммутатора 6, третьи и четвертые входы которого подключены соответственно к выходам регистра 11 адреса и счетчика 9 команд, а с второго выхода 31 снимается адрес ячейки памяти запоминающего устройства, третий выход блока 5 управления подключен к вторым входам счетчика 9 команд, счетчика 10 сдвигов, регистра 11 адреса, регистра 12 числа, регистра 13 сумматора, регистра 14 дополнительного, регистра 15 дополнительного кода, к первой группе входов третьего коммутатора 8, к третьей группе входов второго коммутатора 7, к первому входу 18 блока 17 логических операций и контроля и является входом синхроимпульсов, вторые, третьи, четвертые и пятые выходы блока управляющей памяти подключены соответственно к третьим, четвертым пятым и шестым входам счетчика 9 команд, счетчика 10 сдвигов, регистра 11 адреса, регистра 12 числа, регистра 13 сумматора, регистра 14 дополнительного, регистра 15 дополнительного кода, к первой группе входов третьего коммутатора 8, к третьей группе входов второго коммутатора 7, к вторым входам 19 блока 17 логических операций и контроля и являются выходами управляющих сигналов, сигналов считывания, сигналов записи, сигналов установки устройств в нулевое состояние, выходы регистра 12 числа, регистра 13 сумматора, регистра 14 дополнительного, регистра 15 дополнительного кода подключены к вторым входам третьего коммутатора 8 и к четвертым входам второго коммутатора 7, выход счетчика 10 сдвигов подключен к пятым входам второго коммутатора 7, первые выходы третьего коммутатора 8 подключены соответственно к входам сумматора 16 и к третьим входам 20 блока 17 логических операций и контроля, выходы сумматора 16 подключены к четвертым входам 21 блока 17 логических операций и контроля, вторые выходы третьего коммутатора 8 подключены к пятым входам 22 блока 17 логических операции и контроля, отличающееся тем, что он дополнительно содержит дешифратор 37, блок 38 элементов ИЛИ, блок 39 элементов И, корректор 40, блок 41 памяти, причем первые выходы блока 17 логических операций и контроля подключены к первым входам корректора 40, вторые выходы подключены к шестым входам второго коммутатора 7, третьи выходы блока 17 логических операций и контроля подключены к входам дешифратора 37, первая группа выходов которого подключена к входам блока 41 памяти, выходы блока 41 памяти подключены к первым входам блока 39 элементов И, второй вход которого подключен к третьему выходу блока 5 управления, а выход подключен к второму входу корректора 40, выходы корректора подключены к седьмым входам второго коммутатора 7, вторая группа выходов дешифратора 37 подключена к входам блока 38 элементов ИЛИ, выход которого подключен к восьмому входу второго коммутатора 7.

Процессор предназначен для обработки информации, поступающей с оперативного запоминающего устройства на вход 28.

Для обнаружения и исправления ошибок используем код, исправляющий ошибки в двух байтах информации, реализующий линейную процедуру построения корректирующего кода с синдромным декодированием. Для этого двоичный набор Y, содержащий k информационных символов, разбивается на w=k/b байтов информации (под байтом информации понимается число информационных разрядов не превышающих значение b и пусть b кратно k).

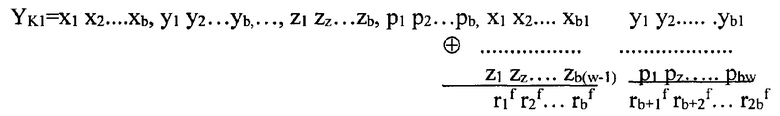

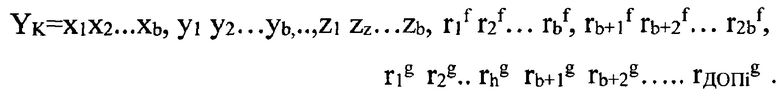

В этом случае двоичный набор может быть представлен в виде:

Результат сложения одноименных разрядов переданных и полученных байтов информации будем называть вектором ошибки.

Для формирования первого вектора ошибки осуществим сложение по mod2 одноименных разрядов байтов информации начиная с первого по (b-1) - блок информации, а для формирования второго вектора ошибки осуществим сложение по mod2 одноименных разрядов байтов информации начиная с второго по b - блок информации (осуществим операцию перемежения) и результат суммирования добавим к двоичному набору Y.

В результате получим кодовый набор YK1:

Для исправления ошибочных разрядов информации, возникает необходимость формирования совокупности проверок (разработки правила кодирования информации), позволяющих определить блок (байт) информации, содержащий ошибку.

С этой целью, осуществим кодирование блоков информации, используя w матриц кодирования.

Каждая матрица кодирования содержит gH=[log2(k+1)] сток при нечетном значении b и gЧ=[log2(k+1)]+1 - при четном значении b.

Каждая строка матрицы кодирования содержит b разрядов.

Примечание: Квадратные скобки означают округление результата в большую сторону.

Представим одноименные строки матриц кодирования двоичным набором, соответствующим одному из значений множества {2b} таким образом, чтобы результат проверки на четность строк матрицы кодирования в двоичном наборе образовывал номер ui, принадлежащий множеству {2 gH} при нечетном значении b и множеству {2 gЧ} - при четном значении b и при этом для полученных значений номеров выполнялось условие uj--ui≥2t.

Значения контрольных проверок (значений контрольных разрядов) матрицы кодирования формируются сложением по mod2 элементов строк матрицы, имеющих единичные значения.

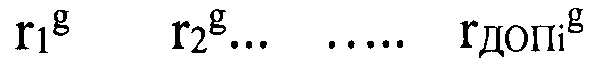

Для исключения совпадения синдромов ошибок (при k=b2b) для второй части синдромов ошибок требуется rgЧ=[log2(2b2b)+1] - контрольных разрядов при четном значении b, и rgH=log2(2b2b) - при нечетном.

В этом случае, число дополнительных контрольных разрядов (строк матрицы кодирования) составит rДОПЧ=[log2(2b2b)+1-b] при четном значении b, и rДОПЧН=[log2(2b2b)-b] - при нечетном.

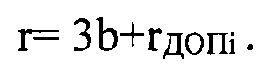

Граница числа контрольных разрядов для кода, корректирующего ошибки в двух байтах информации с формированием аддитивного вектора ошибки, оценивается выражением:

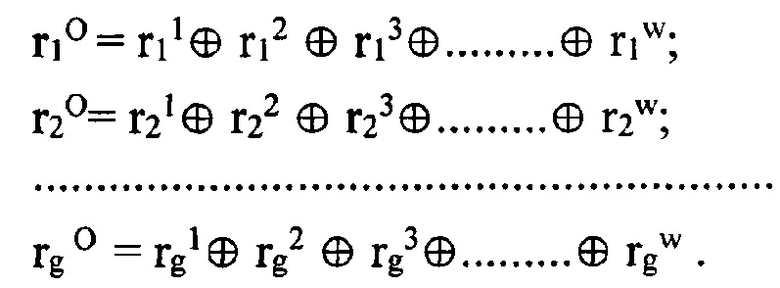

Объединяя по mod2 одноименные контрольные проверки для всех матриц кодирования, получим значения второй части контрольных разрядов

Таким образом, имеем регулярную процедуру построения кодового набора с аддитивным формирование вектора ошибки:

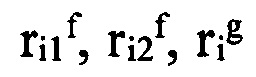

Результат сложения по mod2 переданных значений контрольных разрядов  и контрольных разрядов

и контрольных разрядов  сформированных относительно полученных информационных разрядов даст значение синдрома ошибки, включающего две части:

сформированных относительно полученных информационных разрядов даст значение синдрома ошибки, включающего две части:

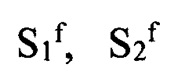

Значение синдрома ошибки  представляют собой векторы ошибки (указывают ошибочные разряды в блоках информации), а значение синдрома ошибки Sg определяет номера ошибочных блоков (байтов) информации.

представляют собой векторы ошибки (указывают ошибочные разряды в блоках информации), а значение синдрома ошибки Sg определяет номера ошибочных блоков (байтов) информации.

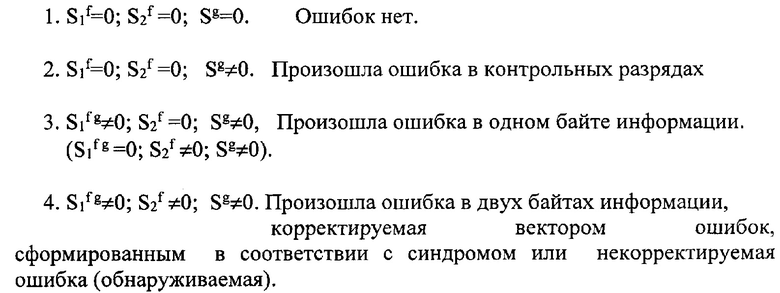

Декодирования включает следующую стратегию:

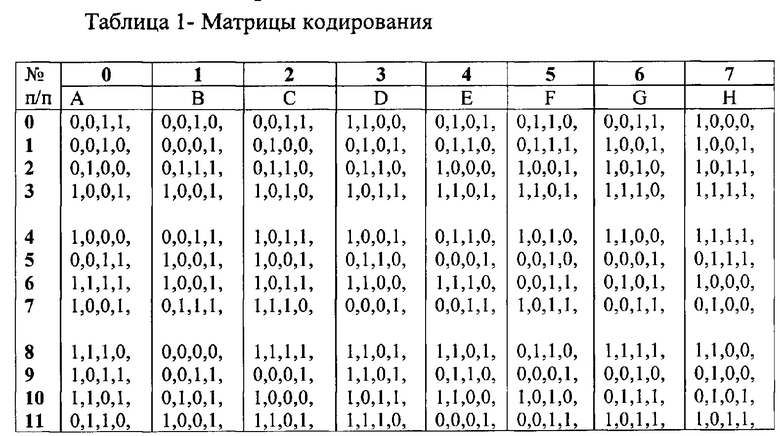

Для коррекции ошибок в двух байтах информации кратности 4, в двоичном наборе, содержащем 64 информационных разряда, используем код (84,20). Матрицы кодирования информации для формирования второй части контрольных разрядов рассматриваемого кода: -  представлены в таблице 1.

представлены в таблице 1.

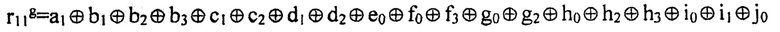

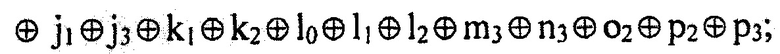

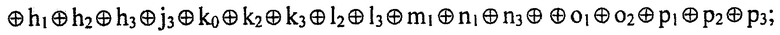

Контрольные проверки (значения второй части контрольных разрядов), полученные относительно полученных матриц кодирования имеют вид:

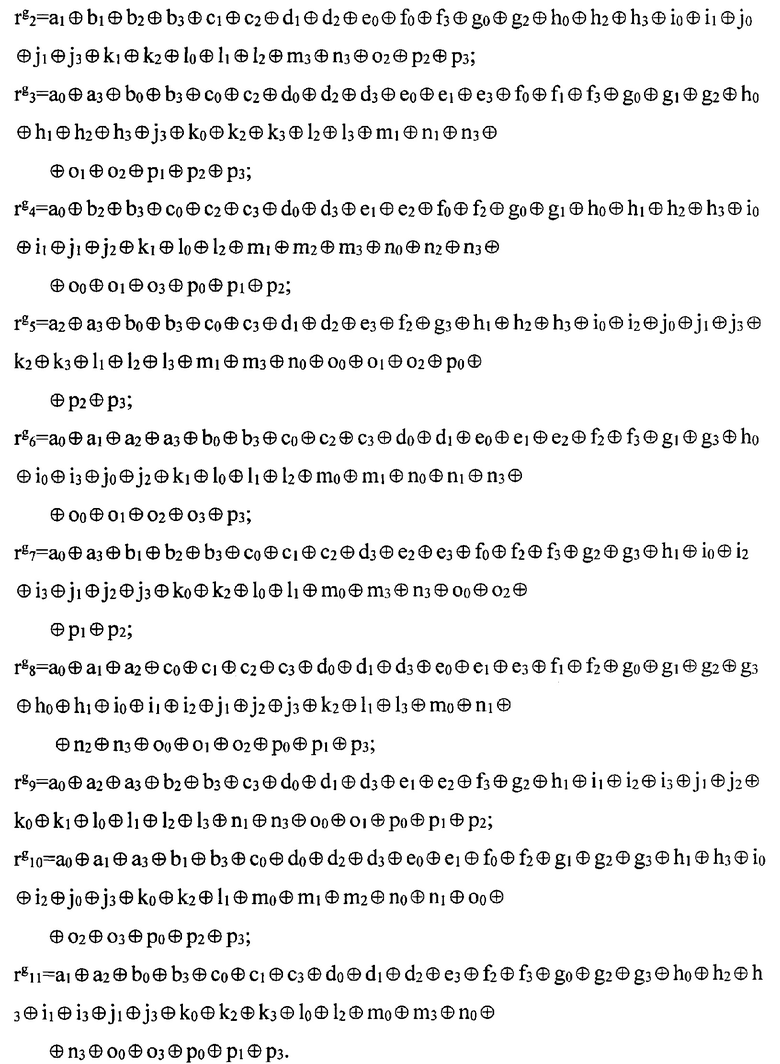

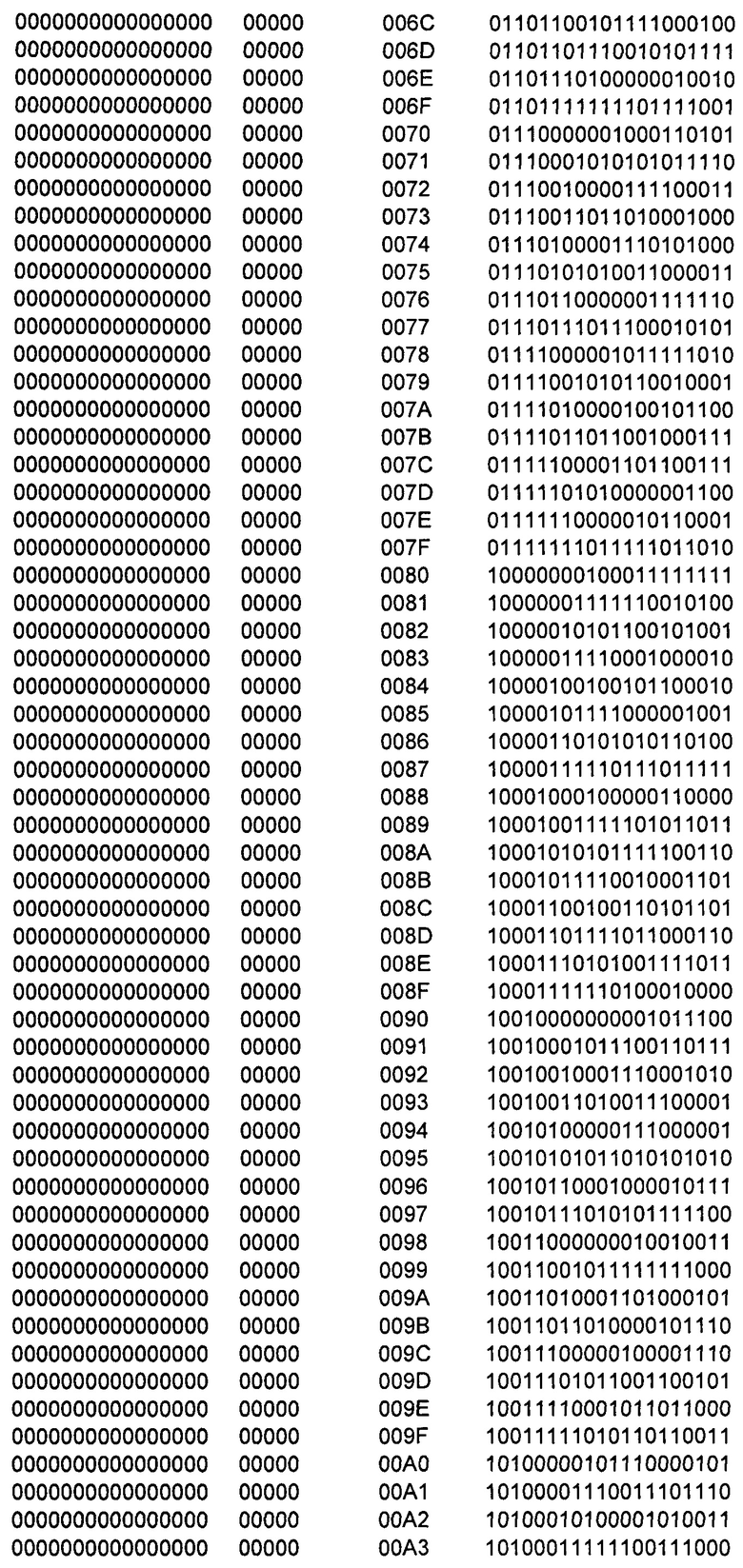

В таблице 2 представлена часть значений синдромов ошибок для кода 84,20.

Предлагаемый код позволяет осуществлять коррекцию ошибок в двух байтах информации, сократить временные затраты на кодирование и декодирование информации и обеспечить работу канала передачи данных в реальном масштабе времени.

Процессор включает в себя два основных устройства: управляющий узел 1 и операционный узел 2.

Управляющий узел 1 координирует действия узлов операционного узла 2 между собой и с другими устройствами ЭВМ, а также выполняет набор операций, включающих команды обращения к памяти. Он вырабатывает в определенной временной последовательности управляющие сигналы, под действием которых в узлах операционного узла 2 выполняются требуемые действия.

Каждое такое элементарное действие, выполняемое в операционном узле 2 в течение одного тактового периода, называется микрооперацией.

В определенные тактовые периоды одновременно могут выполняться несколько микроопераций. Такая совокупность одновременно выполняемых микроопераций называется микрокомандой, а весь набор микрокоманд, предназначенных для решения определенной задачи называется микропрограммой.

Общий временной интервал, в течение которого происходит выборка, хранение и преобразование одной команды в набор управляющих сигналов, называется циклом работы управляющего узла 1.

Таким образом, управляющий узел 1 осуществляет преобразование команды в соответствующий набор управляющих сигналов и обеспечивает:

чтение команды, находящейся в очередной ячейке памяти;

расшифровку кода операции (команды);

отыскание операндов (чисел) по указанному адресу, содержащемуся в команде;

обеспечить выдачу управляющих сигналов в операционный узел для выполнения над ними действий, указанных в коде операции команды.

В данном случае используется микропрограммный управляющий узел 1, в котором микрокоманды хранятся в управляющей памяти 19.

В этом случае, слова, отображающие команды хранятся в памяти в последовательно пронумерованных ячейках, что позволяет формировать адрес очередной команды, добавлением единицы к адресу предыдущей команды, при этом слово состоит из нескольких частей: например, кода операции, указывающего вид операции и адресов чисел, над которыми должна быть произведена соответствующая операция.

Дешифратор 3 кода операций по выбранной из оперативной памяти команде определяет номер требуемой микропрограммы в управляющей памяти 26.

Генератор 4 тактовых импульсов предназначен для формирования тактовых и синхронизирующих импульсов.

Счетчик 9 команд предназначен для формирования адреса ячейки памяти очередной команды, путем естественной выборки, т.е. прибавлением к его содержимому единицы.

Регистр 11 адреса предназначен для формирования адреса ячейки памяти при командах условного или безусловного перехода с возвратом.

Блок 5 управления предназначен для определения адреса очередной микрокоманды в управляющей памяти 20, формирования адреса очередной команды (управления работой первого коммутатора 6), координации работы (выдачи синхроимпульсов) устройств процессора 1.

Управляющая память 26 представляет собой постоянное запоминающее устройство и предназначена для выдачи (в зависимости от кода операции) выдачи управляющих сигналов (сигналов управления, сигналов считывания, сигналов записи, сигналов установки в нулевое состояние) на функциональные узлы процессора. При этом слово памяти содержит информационные разряды (для управляющих сигналов) и контрольные разряды, сформированные на основе предлагаемого метода кодирования.

Операционный узел 2 предназначен для выполнения арифметических и логических операций и включает в свой состав (фиг. 1) счетчик 10 сдвигов, регистр 12 числа, регистр 13 сумматора, регистр 14 дополнительный, регистр 15 дополнительного кода, сумматор 16, блок 17 логических операций и контроля.

Счетчик 10 сдвигов предназначен для подсчета количества сдвигов при выполнении операций умножения и деления, количества сдвигов промежуточных результатов и нормализации.

Регистр 11 адреса представляет собой регистр памяти и предназначен для хранения адресе очередной команды.

Регистр 12 числа представляет собой регистр памяти и предназначен для хранения операндов при выполнении арифметических и логических операций (хранения множимого, при выполнении операции умножения и делителя при выполнении операции деления).

Регистр 13 сумматора (аккумулятора) представляет собой регистр сдвига (вправо - при выполнении операции умножения и влево - при выполнении операции деления), и предназначен для хранения делимого старших разрядов результата умножения.

Заметим, что при выполнении операции деления, блоком 5 управления анализируется значение знакового разряда регистра 12 числа и регистра 13 сумматора.

Регистр 14 дополнительный представляет собой регистр сдвига (вправо - при выполнении операции умножения и влево - при выполнении операции деления), и предназначен для хранения множителя и младших разрядов результата умножения при выполнении операции умножения и результата деления при выполнении операции деления).

Заметим, что при выполнении операции умножения, блоком 5 управления анализируется значение младшего разряда регистра 14 дополнительного.

Регистр 15 дополнительного кода представляет собой регистр памяти и предназначен для хранения отрицательного числа в дополнительном коде (при выполнении операции вычитания и операции деления).

Блок 17 логических операций и контроля (фиг. 2) предназначен для обнаружения и коррекции ошибок, возникающих при выполнении арифметических и логических операций.

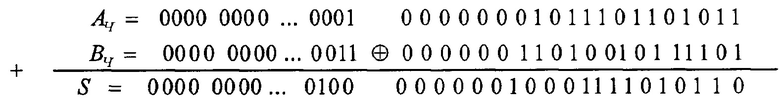

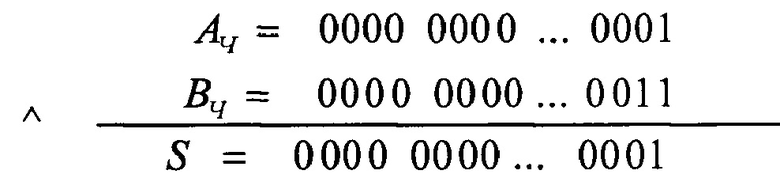

Сумматор 16 представляет собой параллельный n-разрядный сумматор и предназначен для выполнения операции сложения чисел, например, двух двоичных наборов:

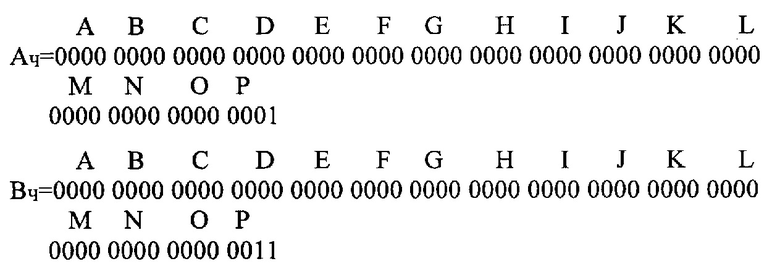

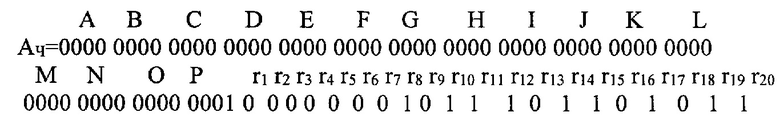

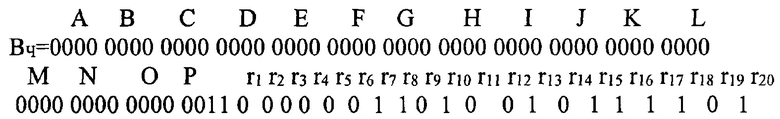

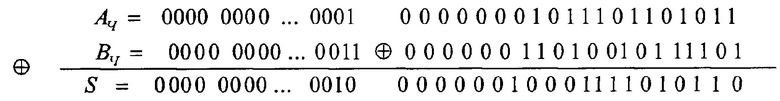

В результате кодирования информации получим значения контрольных разрядов:

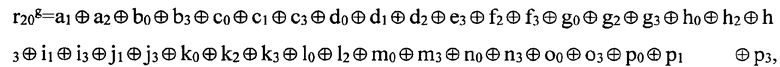

Совокупность значений контрольных разрядов r1 r2 r3 r4 r5 r6 r7 r8 при формировании синдрома ошибки указывают ошибочные разряды в блоках информации, а значение контрольных разрядов r9 r10 r11 r12 r13 r14 r15 r16 r17 r18 r19 r20 указывают номера ошибочных блоков (байтов) информации.

В результате арифметического сложения информационных разрядов и сложения по mod2 значений контрольных получим результат:

Анализ полученного результата, позволяет сделать вывод, что значения контрольных не соответствуют результату суммы информационных разрядов.

Для формирования требуемого значения контрольных разрядов для к полученному значению контрольных разрядов прибавляется поправка, сформированная относительно функции переносов, путем кодирования ее рассматриваемым методом кодирования информации.

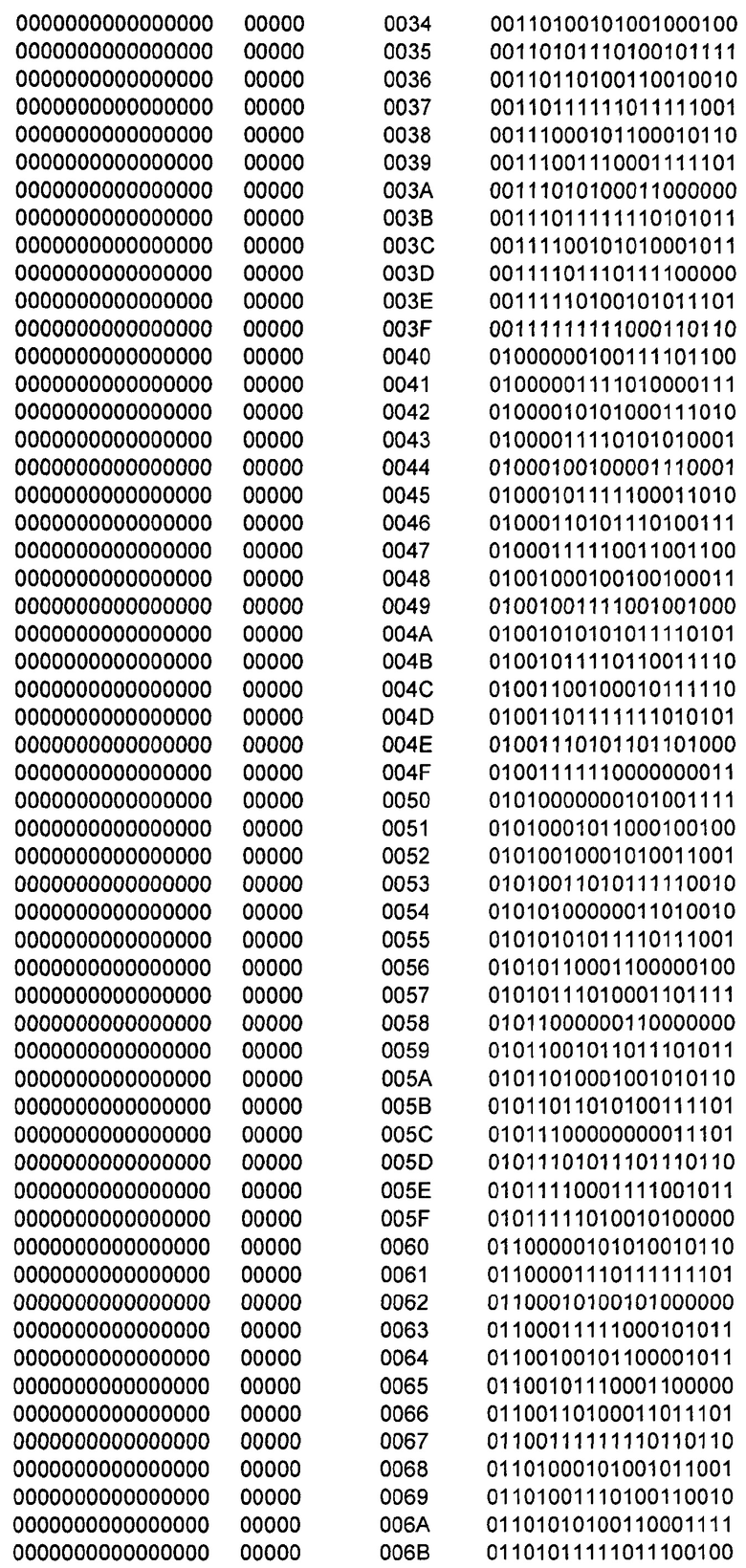

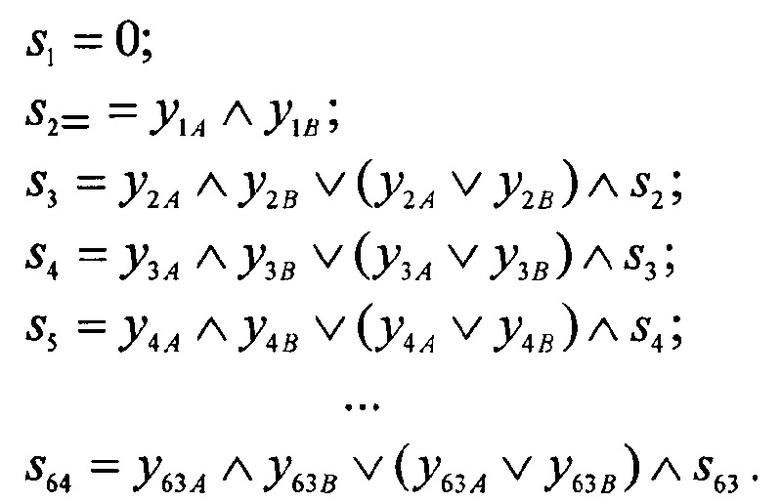

Функциональная схема 45 формирования поправки при выполнении арифметических операций (Фиг. 3) формирует функцию переносов относительно рассматриваемых слагаемых:

Для рассматриваемого примера имеем функцию переносов:

Значения разрядов функции переносов через первый блок 53 элементов ИЛИ поступают на вход первого блока 55 кодирования, с выходов которого снимается значения поправки к значениям контрольных разрядов при выполнении арифметических операций.

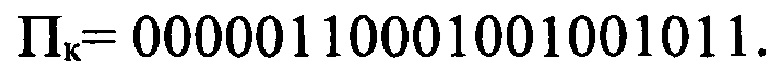

Для полученной функции переносов значение поправки равно:

В первом блоке 50 элементов неравнозначности осуществляется поразрядное сложение по mod2 значений контрольных разрядов слагаемых. Во втором блоке 51 элементов неравнозначности осуществляется поразрядное сложение результата суммы значений контрольных разрядов с значениями разрядов поправки. В результате имеем правильное значение контрольных разрядов для арифметической операции сложения. Для нашего примера получим значение контрольных разрядов:

Вторым блоком 56 кодирования осуществляется кодирование результата суммы слагаемых, поступающего с выходов сумматора 16.

Третьим блоком 52 неравнозначности осуществляется поразрядное сравнение значений контрольных разрядов сформированных относительно полученной арифметической суммы и сформированных на втором блоке 51 элементов неравнозначности. С выходов третьего блока 52 снимается значение синдрома ошибки.

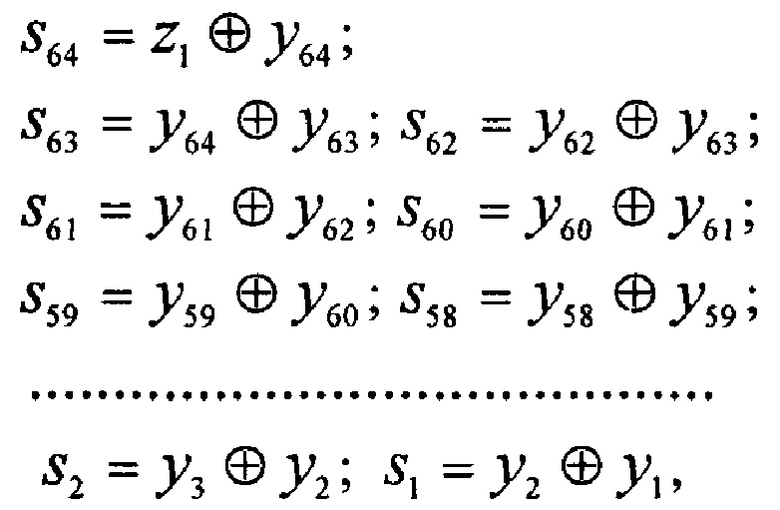

При сдвиге вправо, функциональная схема 48 формирования поправки при выполнении операции сдвига формирует функцию сдвига на основе исходных значений информационных разрядов следующим образом:

где: z1 - значение сигнала переноса из другого регистра, например в старший разряд регистра дополнительного из младшего разряда регистра сумматора при выполнении операции умножения; нумерация информационных разрядов осуществляется справа налево.

Значение разрядов функции сдвигов через первый блок 53 элементов ИЛИ поступают на вход первого блока 55 кодирования, с входов которого снимается значение поправки к контрольным разрядам при сдвиге вправо.

Во втором блоке 51 элементов неравнозначности осуществляется поразрядное сложение значений поправки с значениями контрольных разрядов сдвигаемой информации.

Одновременно результаты сдвига информационных разрядов, через блок 53 элементов ИЛИ поступают на вход второго блока 55 кодирования. Результаты значений контрольных разрядов сформированных на втором блоке 51 элементов неравнозначности и поступающих с выходов второго блока 56 кодирования поразрядно сравниваются третьим блоком 52 элементов неравнозначности, с выходов которого снимается значение синдрома ошибки.

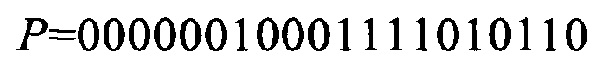

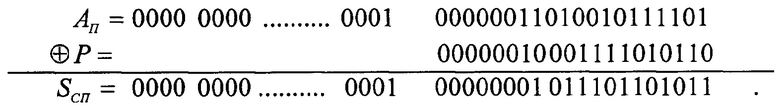

Например, при сдвиге вправо и отсутствии переноса из другого регистра кодового набора:

получим двоичный набор для формирования поправки Р:

При кодировании данного набора с помощью предложенного метода первым блоком 55 кодирования значение поправки составит  . Сложение по mod2 вторым блоком 51 элементов неравнозначности исходного значения контрольных разрядов и значения поправки приведет к правильному значению контрольных разрядов при сдвиге информационных разрядов вправо:

. Сложение по mod2 вторым блоком 51 элементов неравнозначности исходного значения контрольных разрядов и значения поправки приведет к правильному значению контрольных разрядов при сдвиге информационных разрядов вправо:

где SП - результат, полученный при сдвиге исходного кодового набора вправо.

Значения символов поправки при сдвиге влево формируются на основе исходного значения информационных разрядов следующим образом:

где z1 - значение сигнала переноса старшего разряда одного регистра в младший разряд регистра сдвига.

Формирование синдрома ошибки при сдвиге влево осуществляется аналогичным образом.

При выполнении операции логического сложения, значение вектора для вычисления поправки к контрольным разрядам осуществляется схемой 46 формирования поправки при выполнении операции ИЛИ путем выполнения операции И относительно одноименных разрядов слагаемых и кодирования полученного результата рассматриваемым методом..

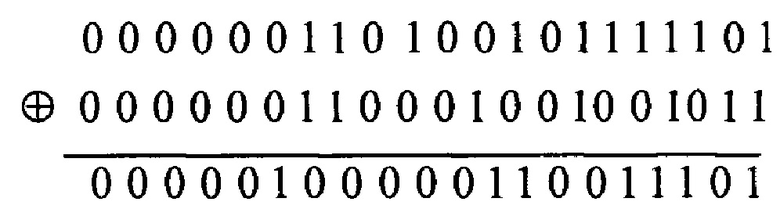

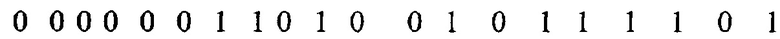

Так, например, при выполнении операции ИЛИ относительно информационных разрядов блоком 43 элементов ИЛИ и сложения по mod2 контрольных разрядов первым блоком 50 элементов неравнозначности (фиг. 2) чисел А и В имеем результат:

Функциональную схему 46 формирования поправки при выполнении операции ИЛИ выполняет операцию И относительно информационных разрядов даст значение вектора для вычисления поправки:

В этом случае первый блок 55 кодирования сформирует значение поправки:

.

.

В результате сложения по mod2 вторым блоком 51 элементов неравнозначности значения поправки и значений контрольных разрядов, поступающих с первого блока 50 элементов неравнозначности, получим результат:  , т.е. имеем правильное значение контрольных разрядов для операции ИЛИ.

, т.е. имеем правильное значение контрольных разрядов для операции ИЛИ.

Результаты значений контрольных разрядов сформированных на втором блоке 51 элементов неравнозначности и поступающих с выходов второго блока 56 кодирования поразрядно сравниваются третьим блоком 52 элементов неравнозначности, с выходов которого снимается значение синдрома ошибки.

Аналогичным образом формируется поправка при выполнении логического умножения, только при формировании вектора поправки схемой 47 формирования поправки при выполнении операции И, реализуется поразрядная операция ИЛИ относительно одноименных разрядов множимого и множителя.

Для операций логического сложения по mod2 блоком 41 сложения по mod2 формирование поправки к контрольным разрядам не требуется.

Так, например, при выполнении операции сложения по mod2 информационных разрядов блоком 41 сложения по mod2 и контрольных разрядов первым блоком 49 элементов неравнозначности (фиг. 2) чисел А и В имеем результат:

Значения контрольных разрядов, сформированные вторым блоком 56 кодирования относительно информационных разрядов, полученных при выполнении арифметических и логических операций, поразрядно сравниваются третьим блоком 52 элементов неравнозначности с переданными значениями контрольными разрядами с учетом поправки.

При отсутствии ошибок на его выходах имеем нулевое значение сигналов.

Работа процессора начинается с приходом сигнала "Пуск" по входной группе 27 входов устройства обмена процессора с периферийными блоками. По этой команде блок 5 выдает команду на считывание с управляющей памяти 26 содержимого первой ячейки памяти.

В первой ячейке памяти расположена команда "Сброс системы", которая устанавливает в исходное состояние регистры и блоки процессора, В счетчик 9 команд записывается "1", устройство управления 1 выдает микрокоманды в следующей последовательности:

1) На первом такте сигналы микрокоманды поступает на вход считывания счетчика 9 команд и на вход записи регистра 11 адреса, при этом содержимое счетчика 9 команд пересылается в регистр 11 адреса (или через первый коммутатор 6 на адресные входы запоминающего устройства при естественной выборке команд непосредственно со счетчика 9 команд);

2) На втором такте к содержимому счетчика 9 команд прибавляется единица - подготавливается адрес следующей команды;

1) На третьем такте сигналы микрокоманды поступают на вход считывания регистра 11 адреса и на вход считывания содержимого ячейки памяти запоминающего устройства по указанному адресу. При этом команда, хранящаяся в первой ячейке памяти, записывается в регистр 12 числа;

2) На четвертом такте сигналы микрокоманды подаются на вход считывания регистра 12 числа, вход второго коммутатора 7 и на вход дешифратора 3 кода операции, где раскодируются, после чего управляющий узел 1 переходит ко второму этапу работы.

Для примера рассмотрим порядок исполнения одной из команд, записанной в регистре 12 числа после выполнения первых четырех тактов.

Пусть в поле кода операции команды содержимого регистра 12 числа записана команда сложения содержимого регистра 13 сумматора с числом расположенным запоминающем устройстве по адресу, указанному в поле адреса регистра 12 числа, (при использовании одноадресной команды).

Управляющий узел 1 при этом выдает следующие микрокоманды:

3) на пятом такте сигналы микрокоманды подаются на вход считывания регистра 12 числа, на вход второго коммутатора 7, первого коммутатора 6 и на вход записи регистра 11 адреса (адрес, хранящийся в регистре 12 числа записывается в регистр 11 адреса, содержимое регистра 12 числа обнуляется);

4) На шестом такте сигналы микрокоманды подаются на вход считывания регистра 11 адреса, на вход первого коммутатора 6, на вход считывания запоминающего устройства и на вход записи регистра 12 числа (из запоминающего устройства в регистр 12 числа записывается второе слагаемое (считаем, что первое слагаемое уже находится в регистре 13 сумматора);

5) На седьмом такте сигналы микрокоманды подаются на вход считывания регистра 12 числа и регистра 13 сумматора, при этом арифметико-логическое устройство осуществляет операцию сложения и запись результата сложения в регистр 13 сумматора следующим образом.

Результат суммы с выхода сумматора 16, поступает на блок 17 логических операций и контроля (фиг. 2), далее устройство работает в соответствии с примером выполнения арифметических операций, приведенном выше.

При этом сформированные значения контрольных разрядов относительно полученной операции сравниваются с переданными значениями контрольных разрядов третьим блоком 52 элементов неравнозначности (фиг. 2). При отсутствии ошибки на его выходах имеем нулевые значения сигналов.

Пусть, произошла одиночная ошибка в четвертом разряде шестнадцатого блока информации (Р=0001*),

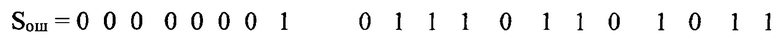

На выходе третьего блоке 52 элементов неравнозначности получим значение синдрома ошибки:

В этом случае, синдром ошибки указывает четвертый ошибочный разряд блока Р (вторая строка табл.2).

На выходе дешифратора 37 появится единичное значение сигнала, которое формирует адрес блока информации, имеющего ошибку и значение вектора ошибки, которые поступают на вход блока 39 элементов И.

При поступлении синхроимпульса на второй вход блока 39 элементов И, значения вектора ошибки поступает на входы корректора 40.

В корректоре 40 осуществляется коррекция ошибочных информационных разрядов, путем поразрядного сложения по mod2 значений вектора ошибки с информационными разрядами байта информации, имеющего ошибку.

С выходов корректора 40, значения информационных разрядов и значения контрольных разрядов с выходов 24 блока 17 логических операций и контроля поступают на входы второго коммутатора 7.

Аналогичным образом процессор функционирует при выполнении логических операций.

При возникновении некорректируемой ошибки, сигналы с выходов дешифратора 37 через блок 38 элементов ИЛИ и второй коммутатор 7 поступают в систему прерывания, где формируется сигнал «Отказ процессора».

8) На восьмом такте выдается микрокоманда "Конец операций" осуществляется переход на следующую операцию, блок 5 управления приводится в исходное состояние и выдает разрешение на начало выполнения следующей команды, адрес которой указан в счетчике 9 команд.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| ОТКАЗОУСТОЙЧИВАЯ ЭВМ | 2018 |

|

RU2704325C1 |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2421786C1 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2579954C2 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2014 |

|

RU2542665C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2422923C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ПРОИЗВОЛЬНЫХ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2450331C1 |

Изобретение относится к области вычислительной техники. Технический результат заключается в коррекции ошибок в двух байтах информации, возникающих в процессоре ЭВМ при выполнении арифметических и логических операций, например, из-за отсутствия или возникновения лишних переносов. Технический результат достигается за счет того, что отказоустойчивый процессор с коррекцией ошибок в двух байтах информации использует алгебраический линейный код для обнаружения и коррекции ошибок в двух байтах информации, который адаптирован для обнаружения и коррекции ошибок при выполнении арифметических и логических операций процессором. 3 ил.

Отказоустойчивый процессор с коррекцией ошибок в двух байтах информации, содержащий управляющий узел, операционный узел, дешифратор кода операции, генератор тактовых импульсов, блок управления, первый коммутатор, второй коммутатор, третий коммутатор, счетчик команд, счетчик сдвигов, регистр адреса, регистр числа, регистр сумматора, регистр дополнительный, регистр дополнительного кода, сумматор, блок логических операций и контроля, включающий блок логического сложения по mod2, блок инвертирования, блок логического сложения, блок логического умножения, функциональную схему формирования поправки при выполнении арифметических операций, функциональную схему формирования поправки при выполнении операции ИЛИ, функциональную схему формирования поправки при выполнении операции И, функциональную схему формирования поправки при выполнении операции сдвига, элемент задержки, первый блок элементов неравнозначности, второй блок элементов неравнозначности, третий блок элементов неравнозначности, первый блок элементов ИЛИ, второй блок элементов ИЛИ, блок кодирования, первый блок элементов И, второй блок элементов И, элемент И, первый, вторые, третьи, четвертые, пятые входы блока логических операций и контроля, первые, вторые, третьи выходы блока логических операций и контроля, управляющую память, входы от устройства обмена, входы данных из запоминающего устройства, включающих значения контрольных разрядов r1f, r2f, r3f, r4f, r5f, r6f, r7f, r8f, r9g, r10g, r11g, r12g, r13g, r14g, r15g, r16g, r17g, r18g, r19g, r20g, сформированных путем сложения по модулю 2 информационных символов а0 a1 а2 а3, b0 b1 b32b3, с0 c1c2c3, d0 d1 d2 d3, e0 e1 e2 e3, f0 f1 f2 f3, g0 g1 g2 g3, h0 h1 h2 h3, i0 i1 i2 i3, j0 j1 j2 j3, k0 k1 k2 k3, l0 l1 l2 l3, m0 m1 m2 m3, n0 n1 n2 n3, o0 o1 o2 o3, p0 p1 p2 р3 в соответствии с правилом кодирования информации:

выход на устройство обмена, выходы данных на запоминающее устройство, выход адрес запоминающего устройства, выходы синхроимпульсов, выходы для сигналов управления, выходы для команды считывание, выходы для сигналов записи, выходы для сигналов установки в нулевое состояние, выходы устройства обмена подключены к первому входу блока управления и к первому входу второго коммутатора, вторые входы которого подключены к выходам запоминающего устройства, первые выходы второго коммутатора поступают на вход устройства обмена, вторые выходы поступают на вход запоминающего устройства, а третьи выходы подключены соответственно к первым входам счетчика команд, счетчика сдвигов, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к входам дешифратора кода операции, ко вторым входам блока управления, к первому входу первого коммутатора, первый выход которого подключен к первому входу регистра адреса, третий вход блока управления подключен к выходам дешифратора кода операции, а четвертый вход подключен к выходам генератора тактовых импульсов, а пятый вход подключен к первому выходу управляющей памяти, первый выход блока управления подключен к входу управляющей памяти, второй выход блока управления подключен ко второму входу первого коммутатора, третьи и четвертые входы которого подключены соответственно к выходам регистра адреса и счетчика команд, а со второго выхода снимается адрес ячейки памяти запоминающего устройства, третий выход блока управления подключен ко вторым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к первому входу блока логических операций и контроля и является входом синхроимпульсов, вторые, третьи, четвертые и пятые выходы блока управляющей памяти подключены соответственно к третьим, четвертым, пятым и шестым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, ко вторым входам блока логических операций и контроля и являются выходами управляющих сигналов, сигналов считывания, сигналов записи, сигналов установки устройств в нулевое состояние, выходы регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода подключены ко вторым входам третьего коммутатора и к четвертым входам второго коммутатора, выход счетчика сдвигов подключен к пятым входам второго коммутатора, первые выходы третьего коммутатора подключены соответственно к входам сумматора и к третьим входам блока логических операций и контроля, выходы сумматора подключены к четвертым входам блока логических операций и контроля, вторые выходы третьего коммутатора подключены к пятым входам блока логических операций и контроля, отличающийся тем, что он дополнительно содержит дешифратор, блок элементов ИЛИ, блок элементов И, корректор, блок памяти, причем первые выходы блока логических операций и контроля подключены к первым входам корректора, вторые выходы подключены к шестым входам второго коммутатора, третьи выходы блока логических операций и контроля подключены к входам дешифратора, первая группа выходов которого подключена к входам блока памяти, выходы блока памяти подключены к первым входам блока элементов И, второй вход которого подключен к третьему выходу блока управления, а выход подключен ко второму входу корректора, выходы корректора подключены к седьмым входам второго коммутатора, вторая группа выходов дешифратора подключена к входам блока элементов ИЛИ, выход которого подключен к восьмому входу второго коммутатора, для обнаружения и коррекции ошибок, возникающих при выполнении арифметической операции сложения, в блоке логических операций и контроля, осуществляется поразрядное сложение по mod2 значений контрольных разрядов слагаемых и поразрядное сложение по mod2 полученного результата со значением поправки, полученной путем формирования функции переносов и кодирования ее рассматриваемым методом кодирования информации, 64-разрядная функция переносов формируется по правилу: s1=0, S2=y1A ^ y1B, s3=у2A ^ y2B v (у2A ^ у2B) ^ s2. s4=у3A ^ у3B v (у3А ^ у3B) ^ s3, s5=у4А ^ у4B v (у4А ^ у4В) ^ s4, …, s64=у63А ^ у63В v (у63А ^ у63B) ^ s63, в результате поразрядного сложения по mod2 полученных значений контрольных разрядов со значением контрольных разрядов, сформированных от результата арифметической суммы информационных разрядов, получим значение синдрома ошибки, для обнаружения и коррекции ошибок, возникающих при выполнении логической операции И в блоке логических операций и контроля, осуществляется поразрядное сложение по mod2 значений контрольных разрядов операндов и поразрядное сложение по mod2 полученного результата со значением поправки, сформированной функциональной схемой формирования поправки при выполнении операции И, в которой относительно рассматриваемых операндов реализуется логическая операция ИЛИ, а ее результат кодируется рассматриваемым методом кодирования информации, в результате поразрядного сложения по mod2 полученных значений контрольных разрядов со значением контрольных разрядов, сформированных от результата логического умножения, получим значение синдрома ошибки, для обнаружения и коррекции ошибок, возникающих при выполнении логической операции ИЛИ в блоке логических операций и контроля, осуществляется поразрядное сложение по mod2 значений контрольных разрядов операндов и поразрядное сложение по mod2 полученного результата со значением поправки, сформированной функциональной схемой формирования поправки при выполнении операции ИЛИ, в которой относительно рассматриваемых операндов реализуется логическая операция И, а ее результат кодируется рассматриваемым методом кодирования информации, в результате поразрядного сложения по mod2 полученных значений контрольных разрядов со значением контрольных разрядов, сформированных от результата логического сложения, получим значение синдрома ошибки, для обнаружения и коррекции ошибок, возникающих при выполнении логической операции сдвига вправо, в блоке логических операций и контроля, осуществляется поразрядное сложение по mod2 исходных значений контрольных разрядов со значением поправки, сформированной функциональной схемой формирования поправки при выполнении операции сдвига, полученной путем формирования функции сдвига вправо и кодирования ее рассматриваемым методом кодирования информации, 64-разрядная функция сдвига вправо формируется по правилу: s64= z ⊕ у64, s63= у63 ⊕ у64, s62= у61 ⊕ у62, …, s1=у2 ⊕ y1, в результате поразрядного сложения по mod2 полученных значений контрольных разрядов со значением контрольных разрядов, сформированных от результата сдвига информационных разрядов вправо, получим значение синдрома ошибки, для обнаружения и коррекции ошибок, возникающих при выполнении логической операции сдвига влево, в блоке логических операций и контроля, осуществляется поразрядное сложение по mod2 исходных значений контрольных разрядов со значением поправки, сформированной функциональной схемой формирования поправки при выполнении операции сдвига, полученной путем формирования функции сдвига влево и кодирования ее рассматриваемым методом кодирования информации, 64-разрядная функция сдвига влево формируется по правилу: s1= z ⊕ у1, s2= y1 ⊕ у2, s3= у2 ⊕ у3, …, s64= у63 ⊕ у64, в результате поразрядного сложения по mod2 полученных значений контрольных разрядов со значением контрольных разрядов, сформированных от результата сдвига информационных разрядов влево, получим значение синдрома ошибки, для обнаружения и коррекции ошибок, возникающих при выполнении операции логического сложения по mod2, в блоке логических операций и контроля, осуществляется поразрядное сложение по mod2 значений информационных разрядов и значений контрольных разрядов слагаемых, формирование поправки к полученной сумме контрольных разрядов не требуется, в результате поразрядного сложения по mod2 полученных значений контрольных разрядов со значением контрольных разрядов, сформированных от результата логического сложения по mod2 информационных разрядов, получим значение синдрома ошибки.

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2448359C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ПРОИЗВОЛЬНЫХ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2450331C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2009 |

|

RU2403615C2 |

| US 5933436 A, 03.08.1999. | |||

Авторы

Даты

2021-10-28—Публикация

2021-01-26—Подача