Изобретение относится ко входным устройствам многоканальных анализаторов амнлитуд электрических импульсов. Устройство может быть применено в ядерной физике и других областях техники.

Известны преобразователи амплитуды импульсов в цифровой код, в которых применен принцип преобразования амплитуды во временной интервал с дальнейшим заполнением этого интервала пачкой импульсов, с открытым входом и индикацией конца заряда, зарядом емкости через диод с обратной связью, схемой блокировки входа на время кодирования и регистрации импульса.

В известных устройствах входная блокировка срабатывает от дискриминатора тока, служащего одновременно индикатором конца заряда и разряда. Для продления блокировки входа включают быстрый разряд. В индикации конца разряда участвуют диод с обратной связью, специальный усилитель, ключ запретов и дискриминатор тока, включенные последовательно. Схема управления считыванием отсутствует. Сигнал считывания попадает на одновибраторы, которые задают постоянное мертвое время, продлевая блокировку входа на время регистрации. Фазировка конца пачки - однократная и производится положительной фазой генератора кода.

када управления блокировкой подключен ко входу блокировки зарядного устройства, другой вход которого соединен с выходом нульоргана блока предварительного анализа, а

вход импульсов запуска - с выходом триггера блокировки. Вход запуска последнего соединен с выходом индикатора конца заряда, а вход сброса - с выходом формирователя импульсов считывания регистра адреса. Оба входа каскада индикации конца разряда соединены непосредственно с выводами запоминающего конденсатора, а выход подключен ко в.ходу запуска каскада управления считыванием, выход которого соединен со входом формирователя импульсов считывания.

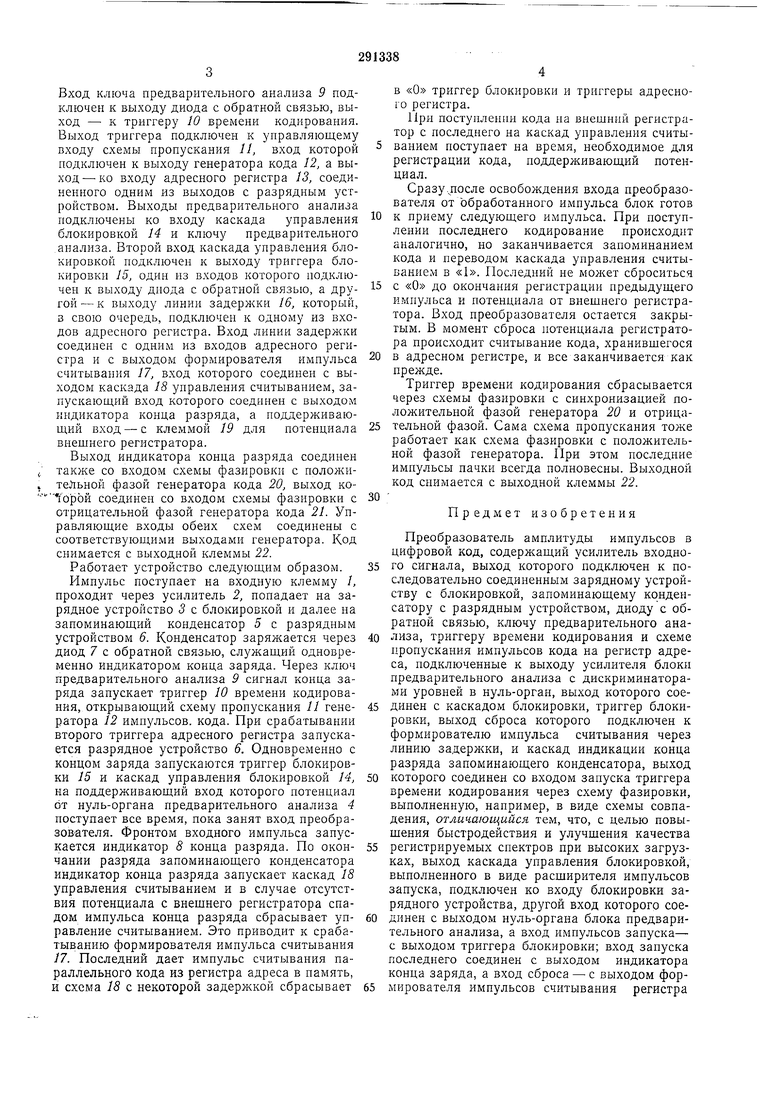

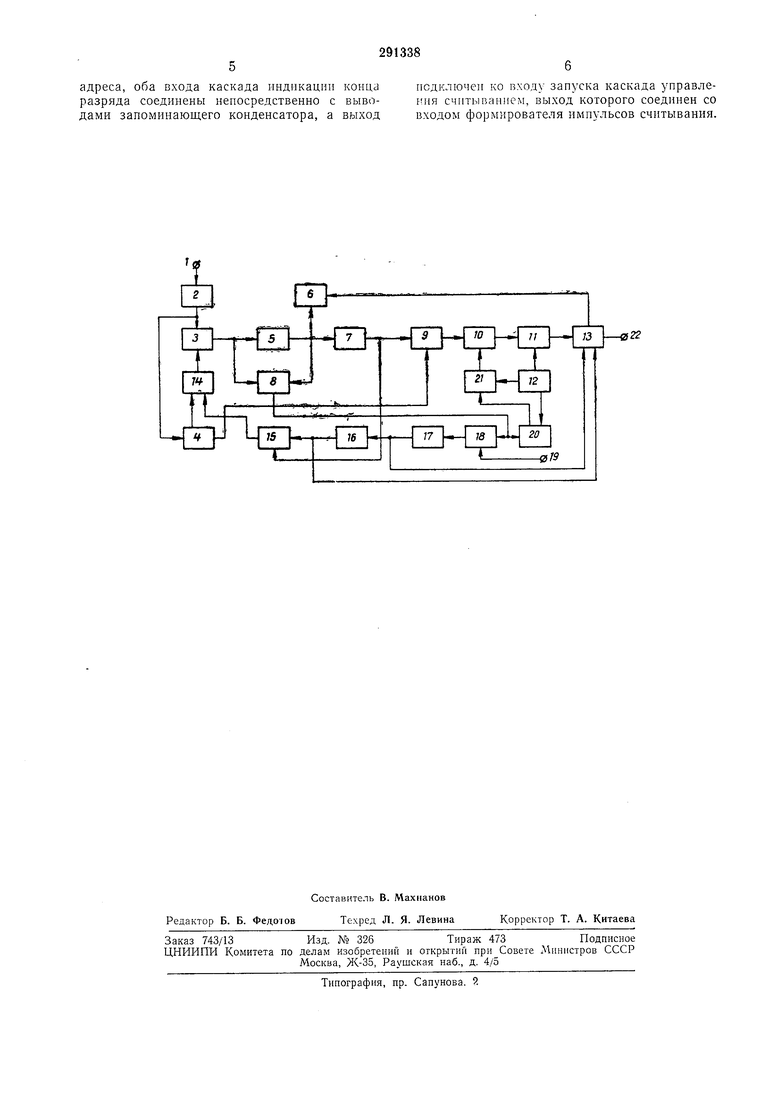

Это позволяет повысить быстродействие устройства и улучщить качество регистрируемых спектров при высоких загрузках. На чертеже приведена блок-схема преобразователя.

Входная клемма / соединена со входом усилителя 2. Выход усилителя одновременно подключен ко входу зарядного устройства 3 с блокировкой и входу блока предварительного анализа 4. Выход зарядного устройства подключен к обкладке запоминающего конденсатора J, к другой обкладке которого подключены разрядное устройство 6 и вход диода 7 с обратной связью. К обеим обкладкам конденсаВход ключа предварительного анализа 9 подключен к выходу диода с обратной связью, выход - к триггеру 10 времени кодирования. Выход триггера подключен к управляющему входу схемы пропускания //, вход которой подключен к выходу генератора кода 12, а выход--ко входу адресного регистра 13, соединенного одним из выходов с разрядным устройством. Выходы предварительного анализа подключены ко входу каскада управления блокировкой 14 и ключу предварительного анализа. Второй вход каскада управления блокировкой подключен к выходу триггера блокировки 15, один из входов которого подключен к выходу диода с обратной связью, а другой - к выходу линии задержки 16, который, в свою очередь, подключен к одному из входов адресного регистра. Вход линии задержки соединен с одним из входов адресного регистра и с выходом формирователя импульса считывания 17, вход которого соединен с выходом каскада IS управления считыванием, запускающий вход которого соединен с выходом индикатора конца разряда, а поддерживающий вход - с клеммой 19 для потенциала внешнего регистратора. Выход индикатора конца разряда соединен (, таклсе со входом схемы фазировки с ноложи. теЛьной фазой генератора кода 20, выход ко Торой соединен со входом схемы фазировки с отрицательной фазой генератора кода 21. Управляющие входы обеих схем соединены с соответствующими выходами генератора. Код снимается с выходной клеммы 22. Работает устройство следующим образом. Импульс поступает на входную клемму /, проходит через усилитель 2, попадает на зарядное устройство 3 с блокировкой и далее на запоминающий конденсатор 5 с разрядным устройством 6. Конденсатор заряжается через диод 7 с обратной связью, служащий одновременно индикатором конца заряда. Через ключ предварительного анализа 9 сигнал конца заряда запускает триггер 10 времени кодирования, открывающий схему нронускания 11 генератора 12 имиульсов. кода. При срабатывании второго триггера адресного регистра запускается разрядное устройство 6. Одновременно с концом заряда запускаются триггер блокировки 15 и каскад управления блокировкой 14, на поддерживающий вход которого потенциал от нуль-органа нредварительного анализа 4 поступает все время, пока занят вход преобразователя. Фронтом входного импульса запускается индикатор 8 конца разряда. По окончании разряда запоминающего конденсатора индикатор конца разряда запускает каскад 18 управления считыванием и в случае отсутствия потенциала с внешнего регистратора спадом импульса конца разряда сбрасывает управление считыванием. Это приводит к срабатыванию формирователя импульса считывания /7. Последний дает импульс считывания параллельного кода из регистра адреса в память, и схема 18 с некоторой задержкой сбрасывает в «О триггер блокировки и триггеры адресного регистра. При поступлении кода на внешний регистратор с последнего на каскад управления считыванием поступает на время, необходимое для регистрации кода, поддерживающий потенциал. Сразу.после освобождения входа преобразователя от обработанного импульса блок готов к приему следующего импульса. При поступлении последнего кодирование происходит аналогично, но заканчивается запоминанием кода и переводом каскада управления считыванием в «1. Последний не может сброситься с «О до окончания регистрации предыдущего импульса и потенциала от внешнего регистратора. Вход преобразователя остается закрытым. В момент сброса потенциала регистратора происходит считывание кода, хранившегося в адресном регистре, и все заканчивается как прежде. Триггер времени кодирования сбрасывается через схемы фазировки с синхронизацией положительной фазой генератора 20 и отрицательной фазой. Сама схема пропускания тоже работает как схема фазировки с положительной фазой генератора. При этом последние импульсы пачки всегда полновесны. Выходной код снимается с выходной клеммы 22. Предмет изобретения Преобразователь амплитуды импульсов в цифровой код, содержащий усилитель входного сигнала, выход которого подключен к последовательно соединенным зарядному устройству с блокировкой, запоминающему конденсатору с разрядным устройством, диоду с обратной связью, ключу предварительного анализа, триггеру времени кодирования и схеме пропускания импульсов кода на регистр адреса, подключенные к выходу усилителя блоки предварительного анализа с дискриминаторами уровней в нуль-орган, выход которого соединен с каскадом блокировки, триггер блокировки, выход сброса которого подключен к формирователю импульса считывания через линию задержки, и каскад индикации конца разряда запоминающего конденсатора, выход которого соединен со входом запуска триггера времени кодирования через схему фазировки, выполненную, например, в виде схемы совпадения, отличающийся тем, что, с целью повышения быстродействия и улучшения качества регистрируемых спектров при высоких загрузках, выход каскада управления блокировкой, выполненного в виде расширителя импульсов запуска, подключен ко входу блокировки зарядного устройства, другой вход которого соединен с выходом нуль-органа блока предварительного анализа, а вход импульсов запуска- с выходом триггера блокировки; вход запуска последнего соединен с выходом индикатора конца заряда, а вход сброса - с выходом формирователя импульсов считывания регистра

адреса, оба входа каскада индикации конца разряда соедииены непосредственно с выводами запоминающего конденсатора, а выход

иодключел ко входу заиуска каскада управления считыванием, выход которого соединен со входом формирователя имиульсов считывания.

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ ЧИСЕЛ В КОДЕ ХЭММИНГАЬ-'СЕСОЮЗНДЯ|^ДШ1НО-Г?ХЩ»;?еКДЯ^ИЗЯНОТЕНА' | 1971 |

|

SU310389A1 |

| УСТРОЙСТВО для КОДИРОВАНИЯ ЧИСЕЛ в РЕКУРРЕНТНОЛ!КОДЕ | 1972 |

|

SU353346A1 |

| Устройство для сопряжения цифровой вычислительной машины | 1987 |

|

SU1444793A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1970 |

|

SU287422A1 |

| Многоканальное телеизмерительное устройство | 1980 |

|

SU959127A1 |

| Преобразователь амплитуд импульсов в цифровой код | 1974 |

|

SU746920A1 |

| Цифровой преобразователь электрической емкости | 1987 |

|

SU1553922A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

А

Даты

1971-01-01—Публикация