135

нения, блок 4 масштабного усиления, блок 5 коммутации, А1Щ 6, формирователь 7 кода, блок 8 управления, блок 9 формирования кода инерционной шкалы, бл ок 10 проверки разрядов на ран- нозначность, блок 11 формироватшя сигнала (ФС) перегрузки, управляемый аттенюатор 12, блок 13 анализа кода шкалы, блок 14 ФС конца перегрузкиj

1

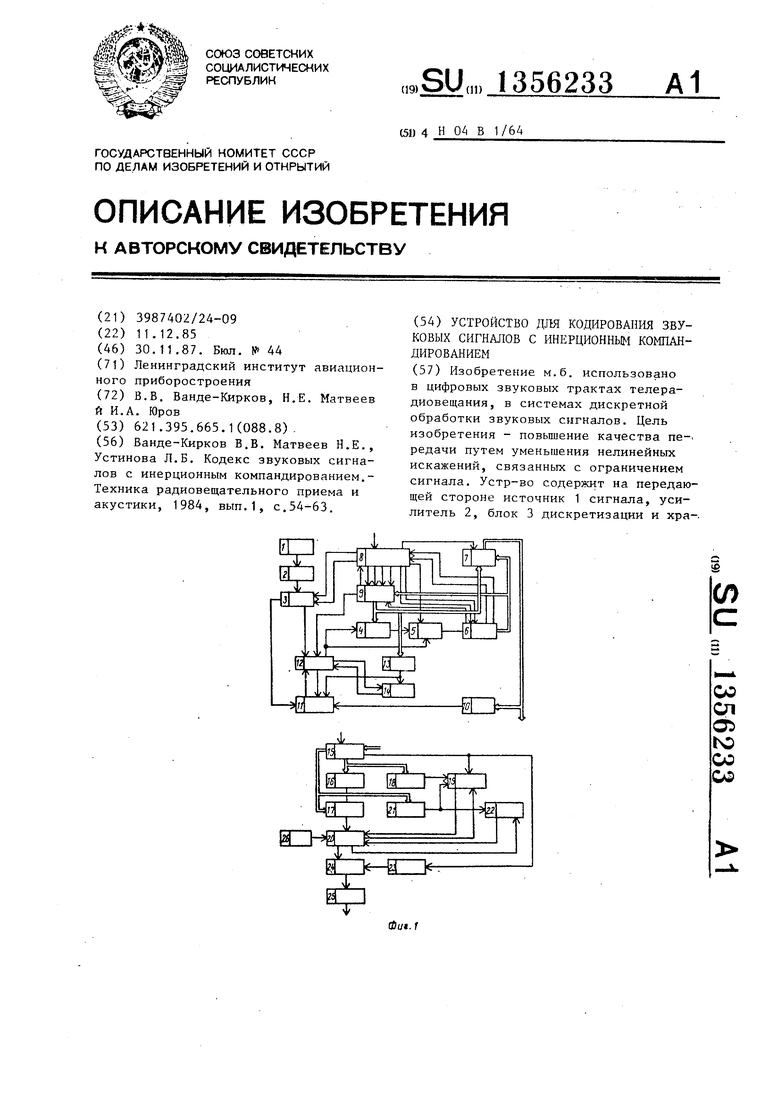

Изобретение относится к технике передачи информации и может быть использовано в цифровых звуковых трактах телерадиовещания, в системах дискретной обработки звуковых сигналов.

Цель изобретения - повышение качества передачи путем уменьшения нелинейных искажений, связанных с ограничением сигнала.

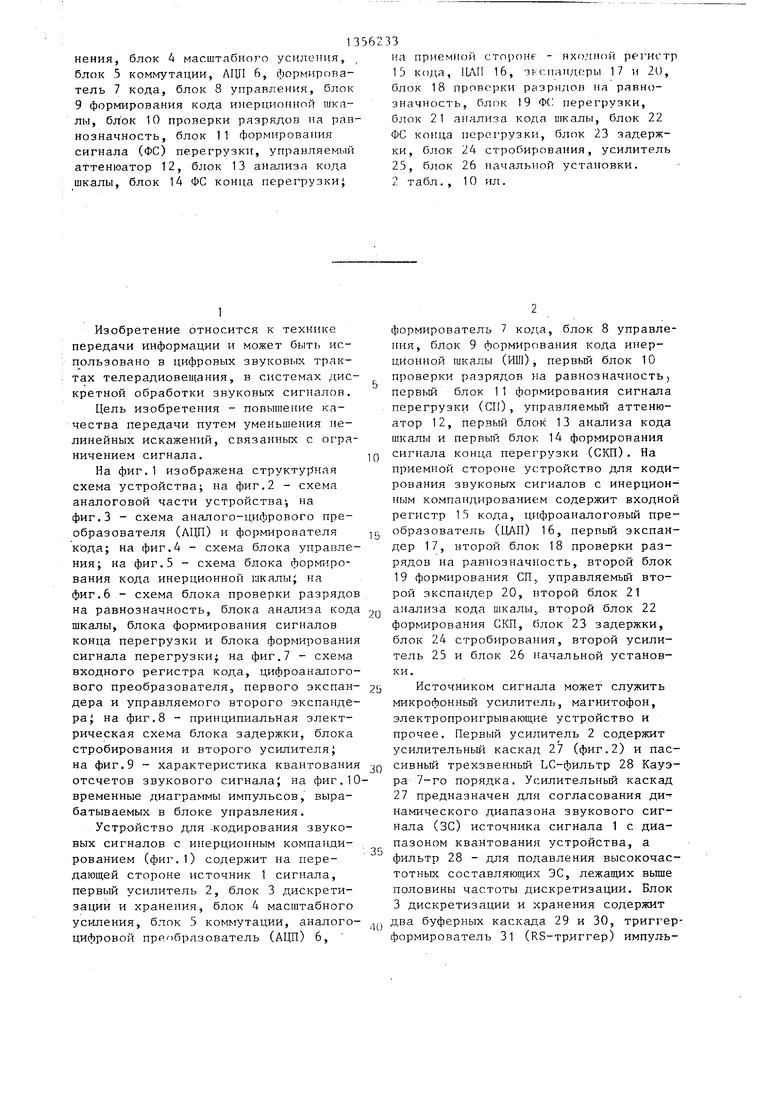

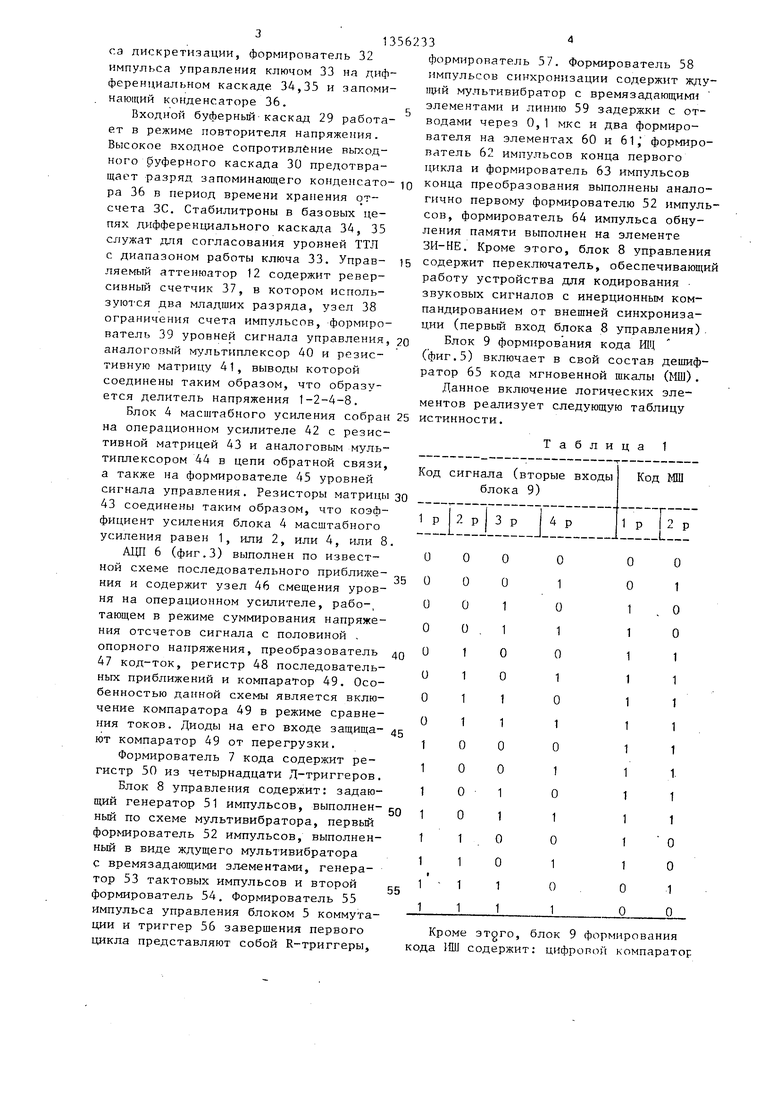

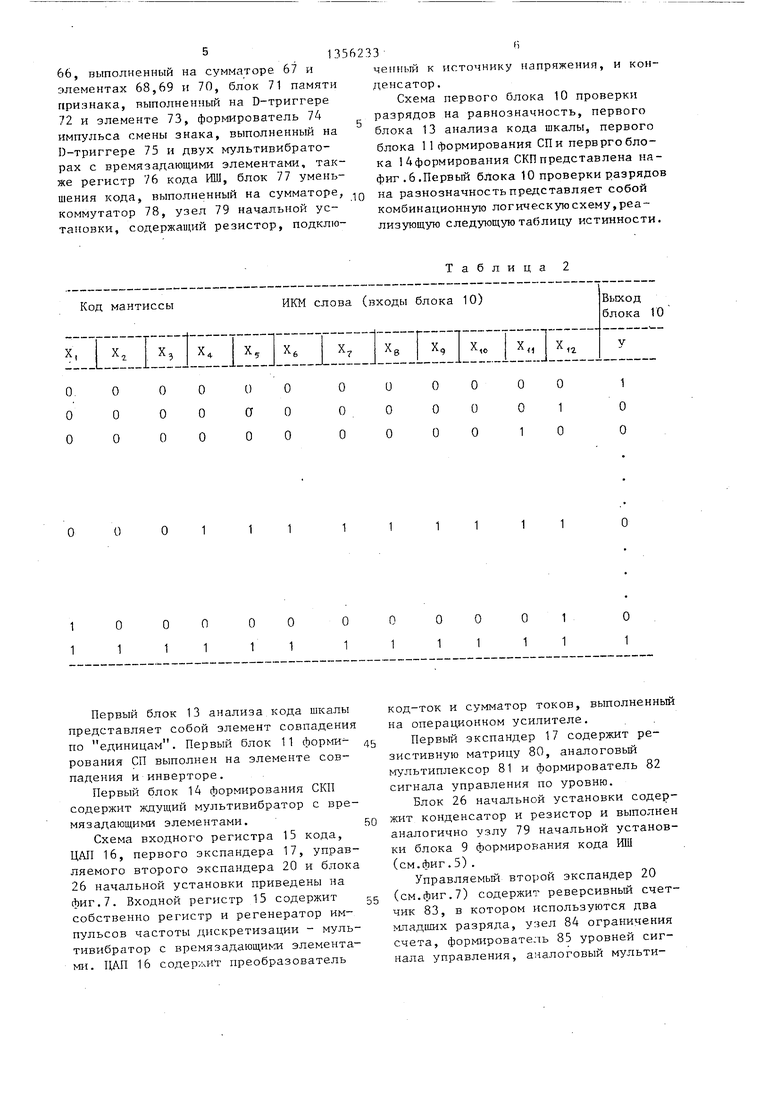

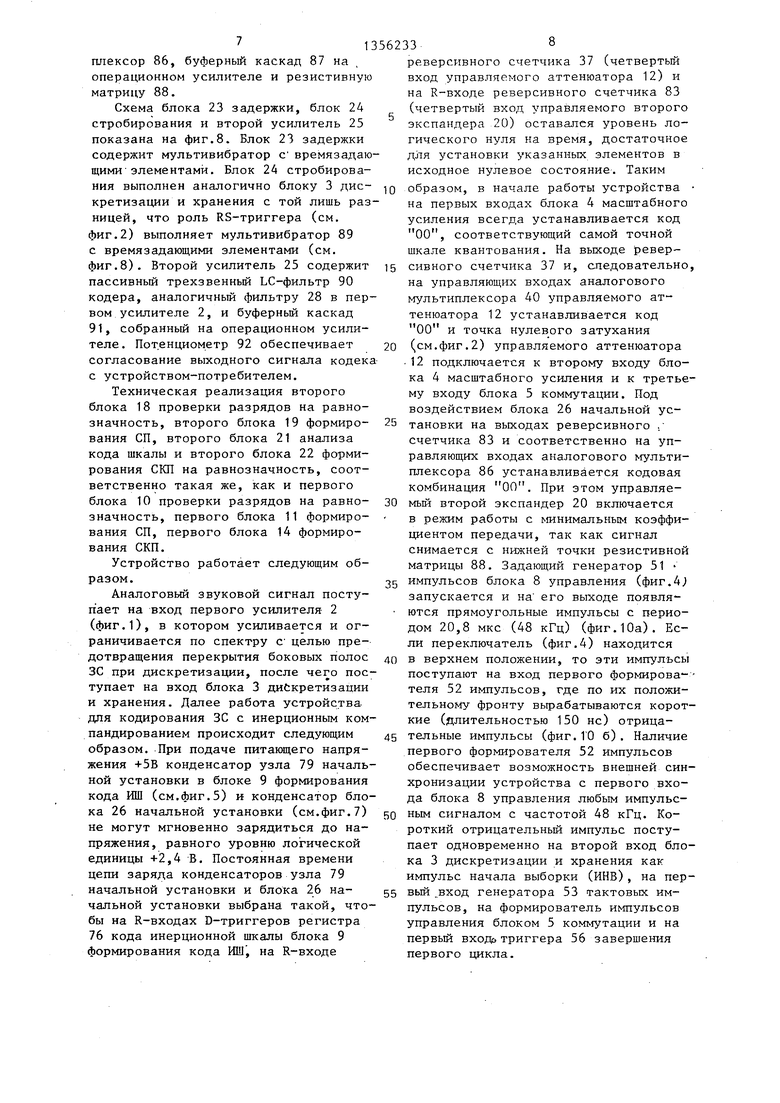

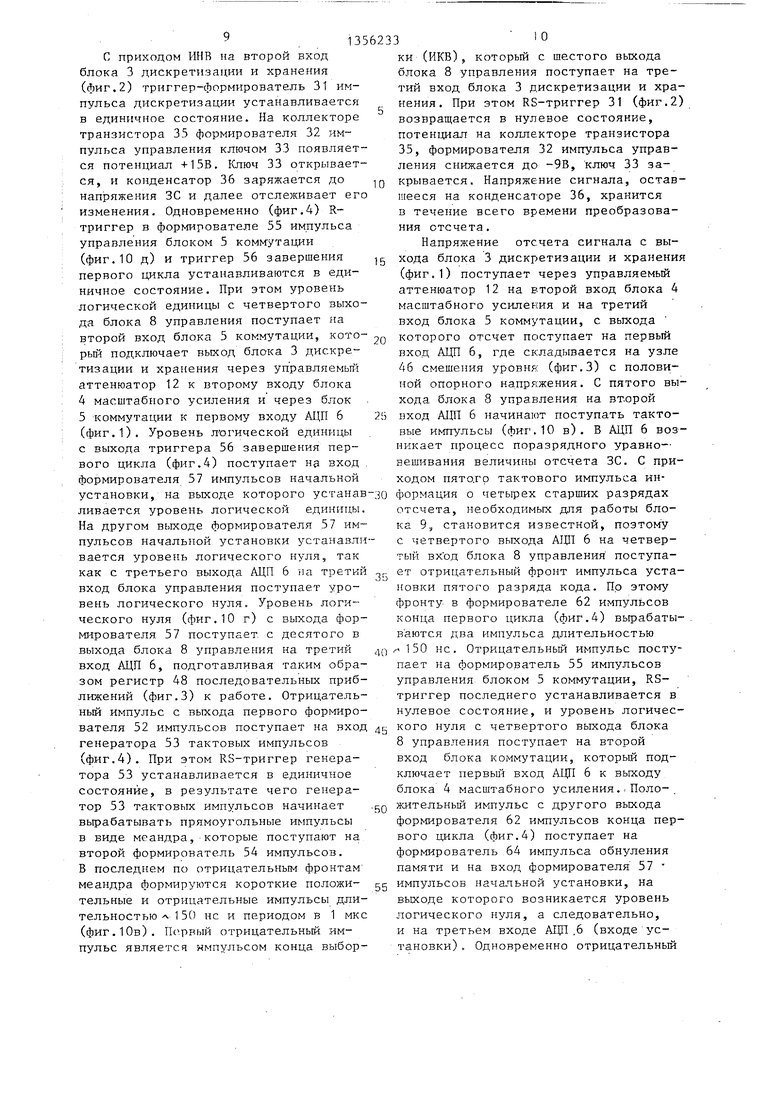

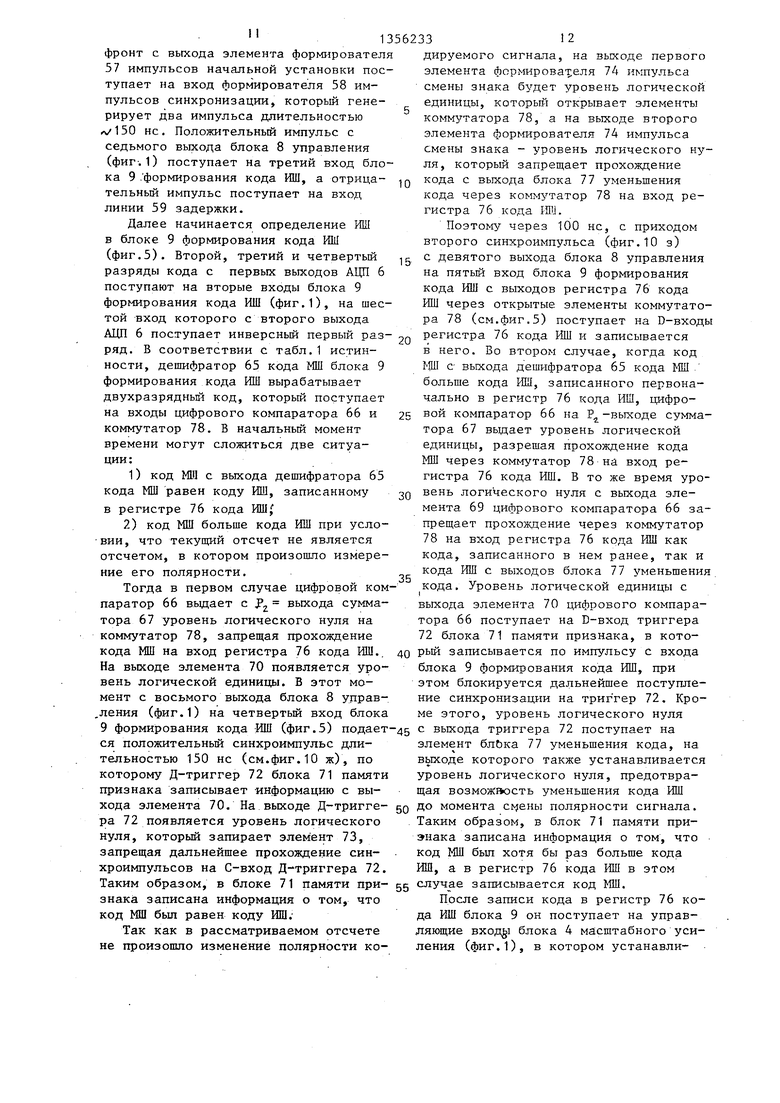

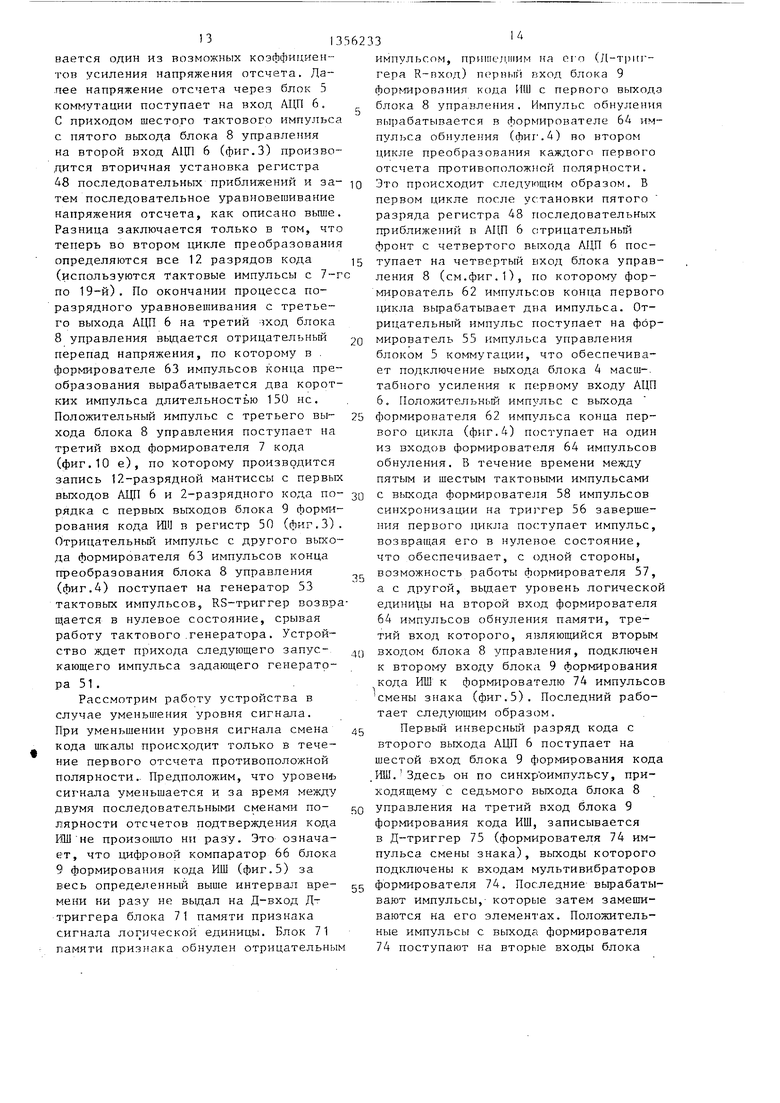

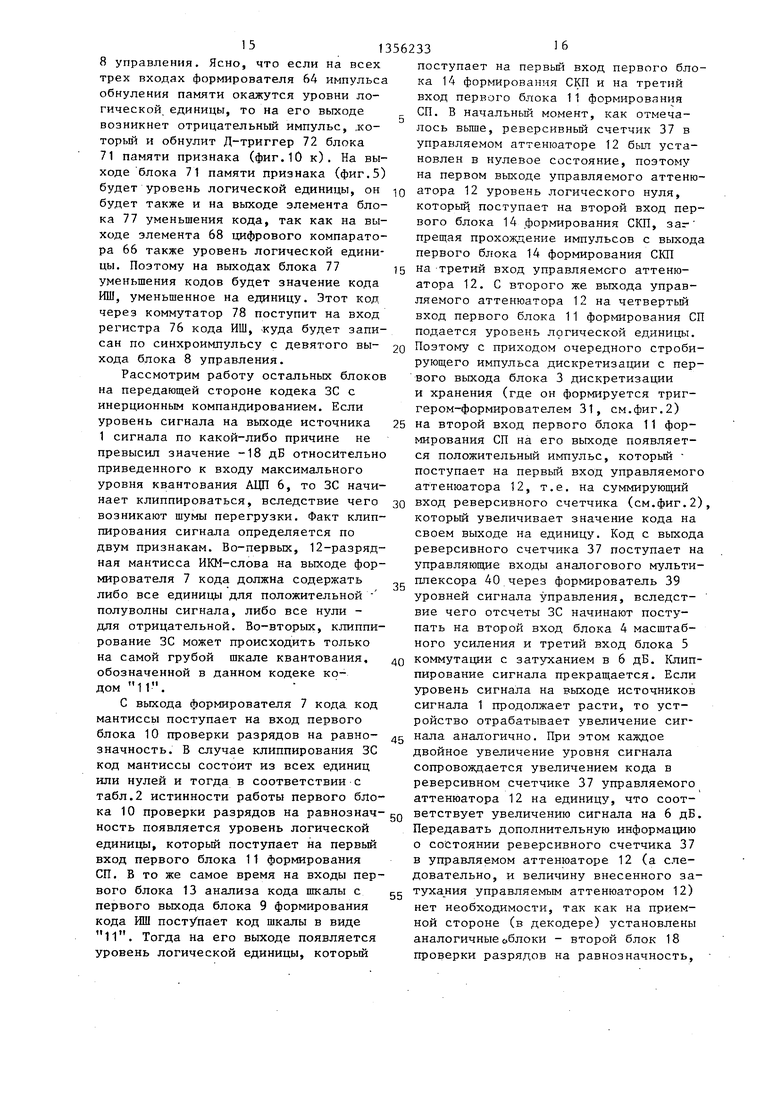

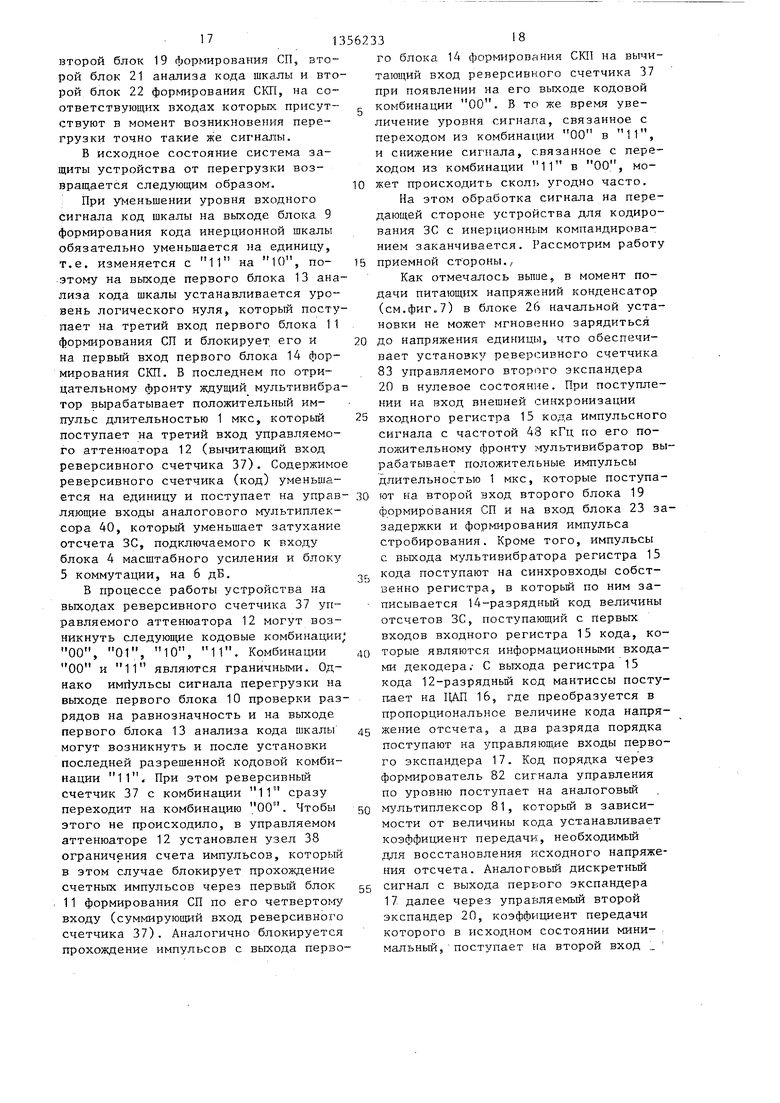

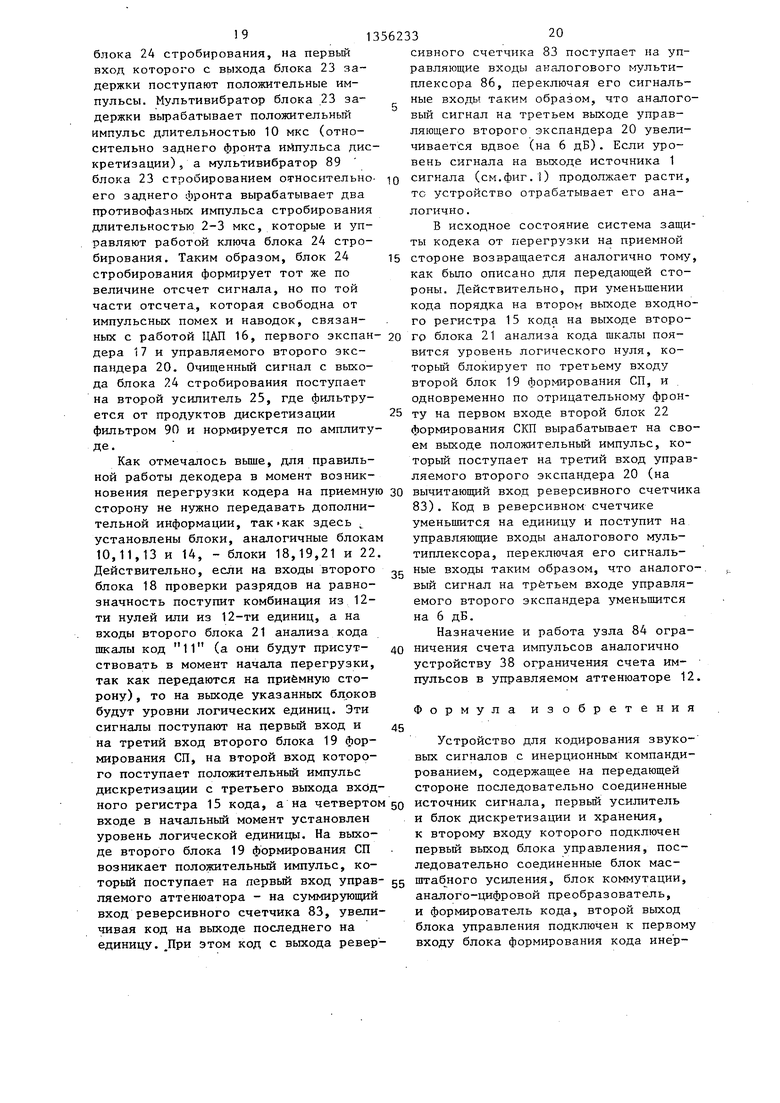

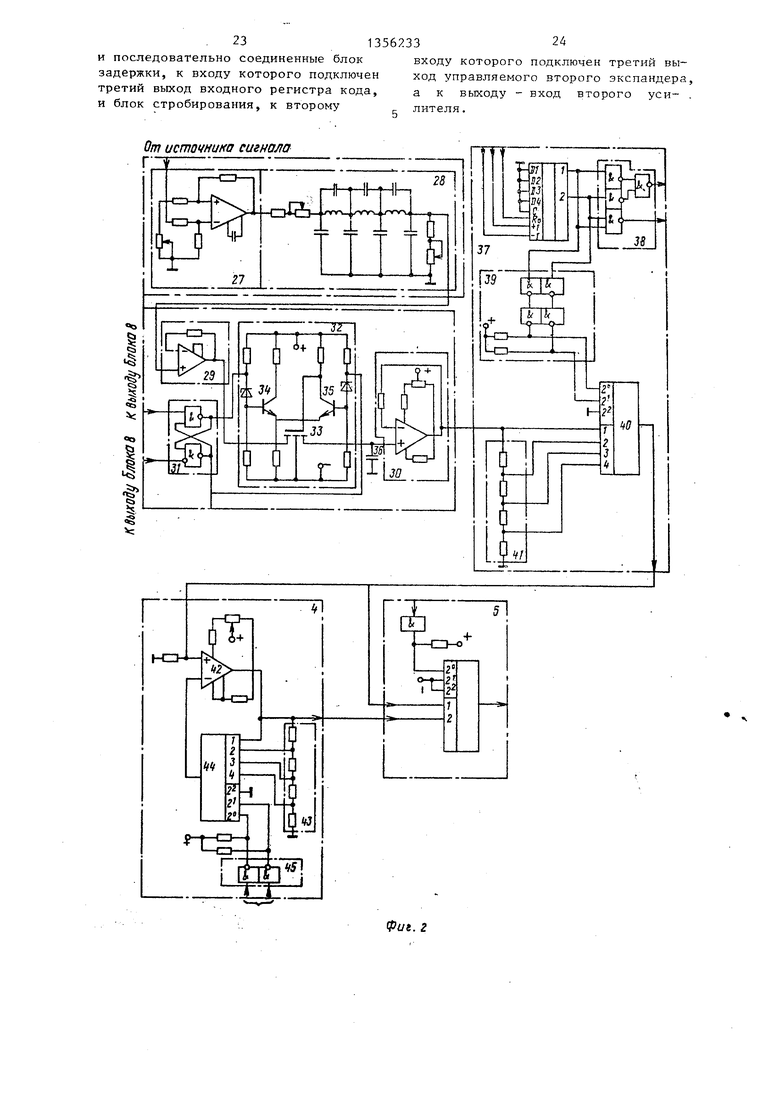

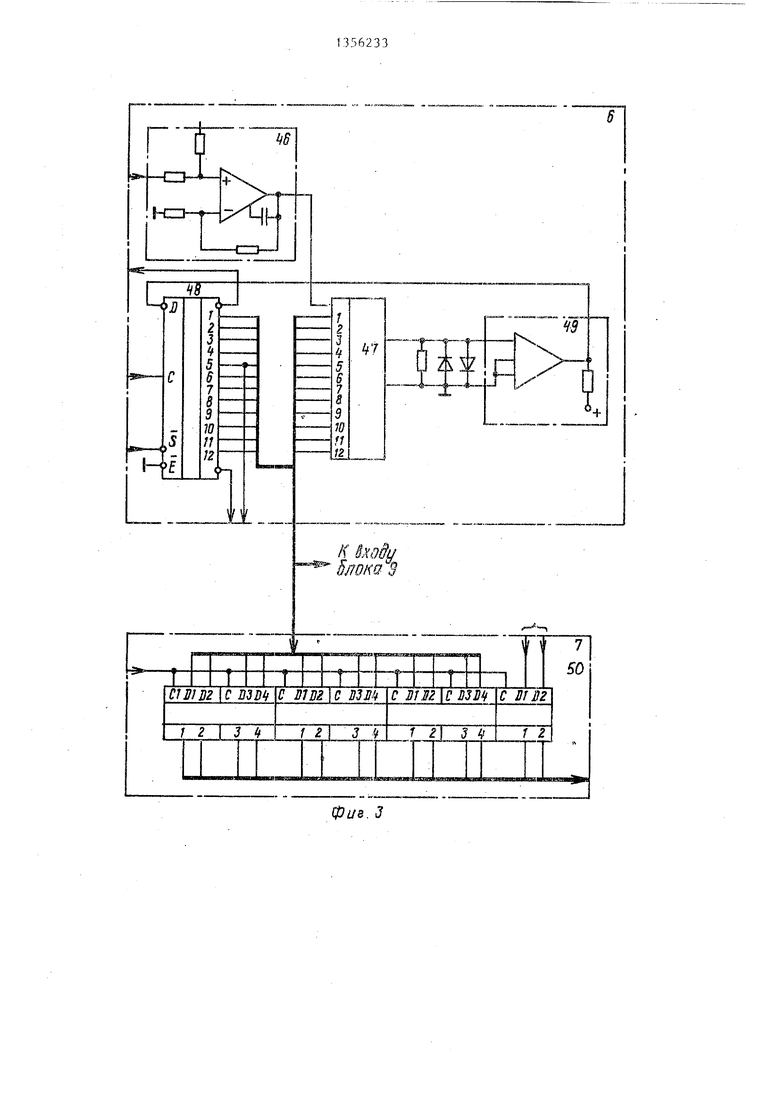

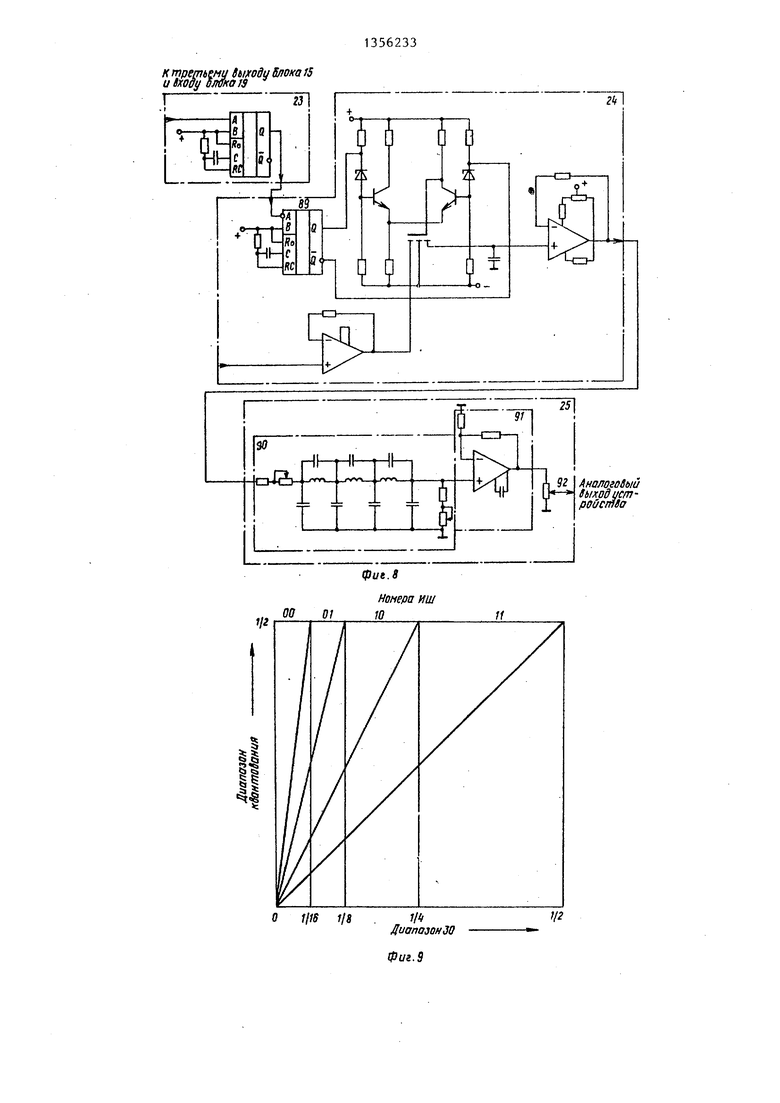

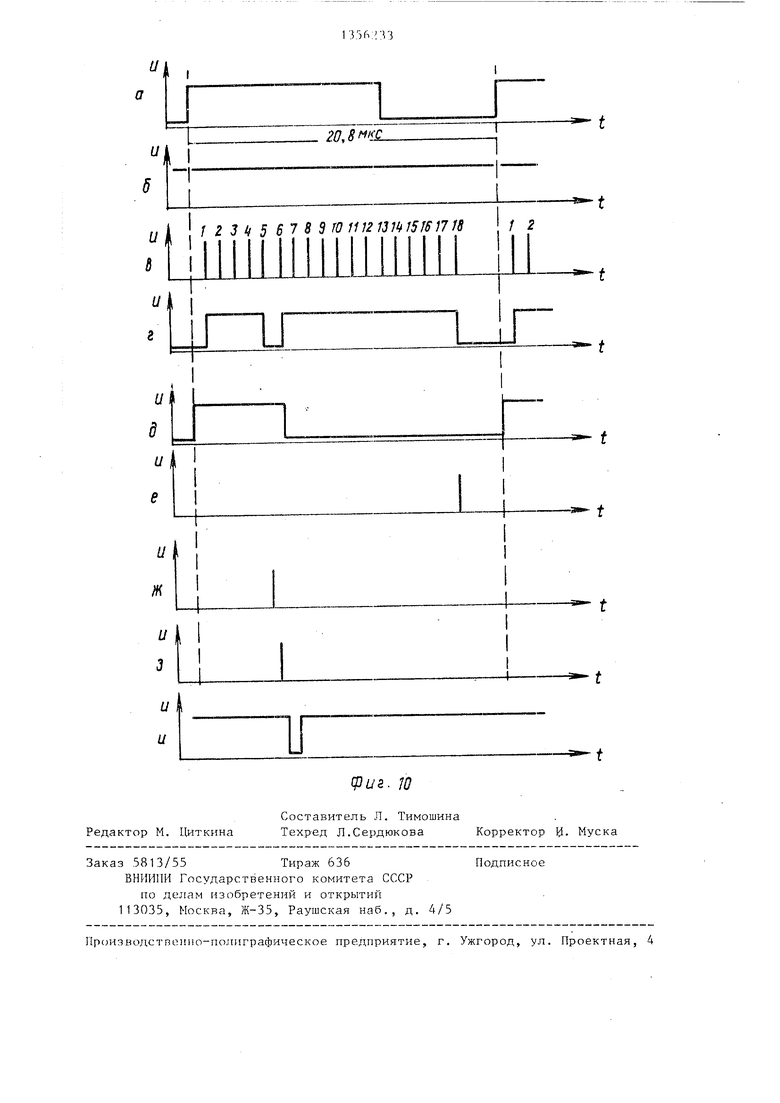

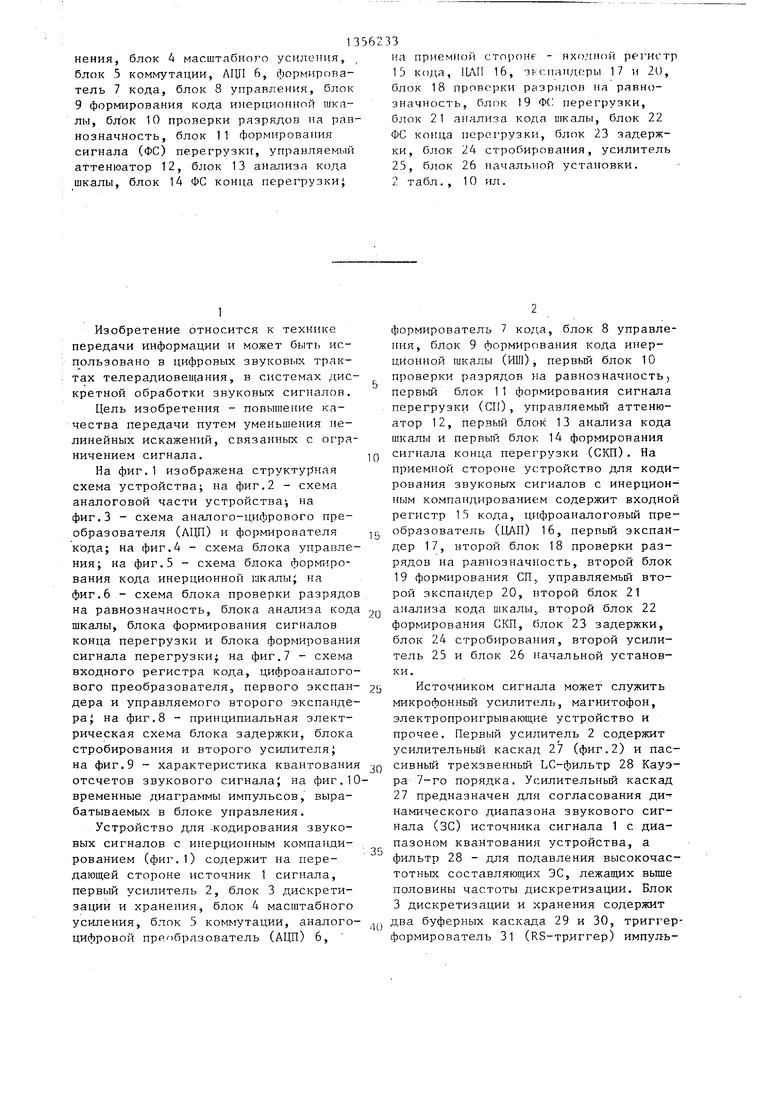

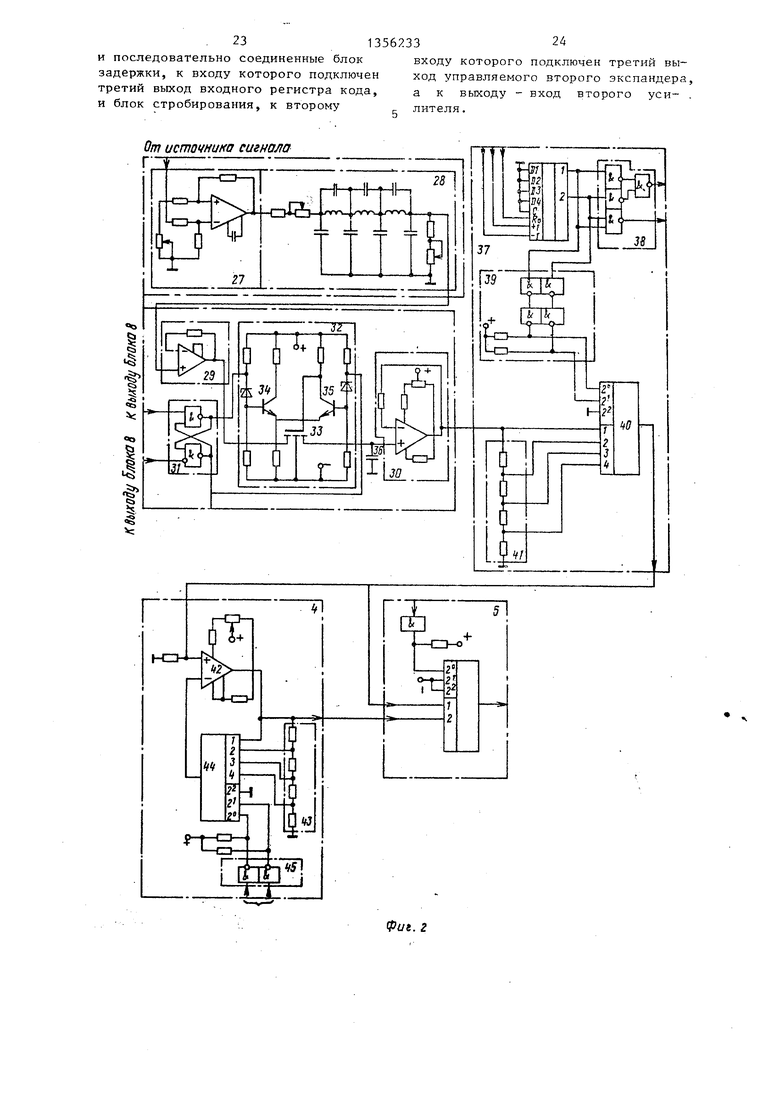

На фиг.1 изображена структур ная схема устройства; на фиг.2 - схема аналоговой части устройства , на фиг.З - схема аналого-цифрового преобразователя (АЦП) и формирователя к ода; на фиг.4 - схема блока управления; на фиг.5 - схема блока формирования кода инерционной шкалы; на фиг.6 - схема блока проверки разрядов на равнозначность, блока анализа кода шкалы, блока формирования сигналов конца перегрузки и блока формирования сигнала перегрузки; на фиг.7 - схема входного регистра кода, цифроаналого- вого преобразователя, первого экспандера и управляемого второго экспандера J на фиг.8 - принципиальная электрическая схема блока задержки, блока стробирования и второго усршителя} на фиг.9 - характеристика квантования отсчетов звукового сигнала; на фиг.10 временные диаграммы импульсов, вырабатываемых в блоке управления.

Устройство для .кодирования звуковых сигналов с инерционным компанди- рованием (фиг.1) содержит на пере- даюш;ей стороне источник 1 сигнала, первый усилитель 2, блок 3 дискретизации и хранения, блок 4 масштабного усиления, блок 5 коммутации, аналого- цифровой преобразователь (АЦП) 6,

::33

на приемной сторон - нходной регист 13 кода, 11АП 16, экспандеры 17 и 20, блок 18 проверки разрядорз на равнозначность, блок 19 ФС1 перегрузки, блок 21 анализа кода шкалы, блок 22 ФС конца перегрузки, блок 23 задержки, блок 24 стробирования, усилитель 25, блок 26 начальной установки. 2 табл., 10 ил.

2

формирователь 7 кода, блок 8 управления, блок 9 формирования кода инерционной шкалы (ИШ), первый блок 10

проверки разрядов на равнозначность,

первый блок 11 формирования сигнала

перегрузки (СП), управляемьй аттенюатор 12, первый блок 13 анализа кода шкалы и первый блок 14 формирования

сигнала конца перегрузки (СКП). На приемной стороне устройство для кодирования звуковых сигналов с инерционным компандированием содержит входной регистр 15 кода, цифроаналоговый преобразователь (ЦАП) 16, первый экспандер 17, второй блок 18 проверки разрядов на равнозначность, второй блок 19 формирования СП, управляемый второй экспандер 20, второй блок 21

анализа кода шкалы, второй блок 22 формирования СКП, блок 23 задержки, блок 24 стробирования, второй усилитель 25 и блок 26 начальной установки.

Источником сигнгша может служить микрофонньй усилитель, магнитофон, электропроигрываюш,ие устройство и прочее. Первый усилитель 2 содержит усилительньш каскад 27 (фиг.2) и пассивньм трехзвенный LC-фильтр 28 Кауэ- ра 7-го порядка. Усилительный каскад 27 предназначен для согласования ди- намического диапазона звукового сигнала (ЗС) источника сигнала 1 с диапазоном квантования устройства, а фильтр 28 - для подавления высокочастотных составляюш;их ЭС, лежащих вьше половины частоты дискретизации. Блок 3 дискретизации и хранения содержит

два буферных каскада 29 и 30, триггер- формирователь 31 (RS-триггер) импуль

формирователь 57. Формирователь импульсов синхронизации содержит ПЦ1Й мультивибратор с времязадающ элементами и линию 59 задержки с водами через О,1 МКС и два форми вателя на элементах 60 и 61, фор ватель 62 импульсов конца первог цикла и формирователь 63 импульс конца преобразования выполнены а гично первому формирователю 52 и сов, формирователь 64 импульса о ления памяти выполнен на элемент ЗИ-НЕ. Кроме этого, блок 8 управ содержит переключатель, обеспечи работу устройства для кодировани звуковых сигналов с инерционным пандированием от внешней синхрон ции (первьм вход блока 8 управле

Блок 9 формирования кода ШЧ (фиг.5) включает в свой состав д ратор 65 кода мгновенной шкалы (

Данное включение логических э ментов реализует следующую табли

са дискретизации, формирователь 32 импульса управления ключом 33 на дифференциальном каскаде 34,35 и запоминающий конденсаторе 36.

Входной буферный каскад 29 работает в режиме повторителя напряжения. Высокое входное Сопротивление выходного буферного каскада 30 предотвращает разряд запоминающего конденсато- IQ ра 36 в период времени хранения отсчета ЗС, Стабилитроны в базовых цепях дифференциального каскада 34, 35 служат для согласования уровней ТТЛ с диапазоном работы ключа 33. Управ- 15 ляемый аттенюатор 12 содержит реверсивный счетчик 37, в котором используются два младших разряда, узел 38 ограничения счета импульсов, формирователь 39 уровней сигнала управления, 20 аналоговый мультиплексор 40 и резис- тивную матрицу 41, выводы которой соединены таким образом, что образуется делитель напряжения 1-2-4-8.

Блок 4 масштабного усиления собран 25 истинности.

на операционном усилителе 42 с резис-„ .

„,тТаблица

тивнои матрицей 4J и аналоговым муль-

типлексором 44 в цепи обратной связи, а также на формирователе 45 уровней сигнала управления. Резисторы матрицы зо 43 соединены таким образом, что коэффициент усиления блока 4 масштабного усиления равен 1, или 2, или 4, или 8.

АЦП 6 (фиг.З) выполнен по известной схеме последовательного приближения и содержит узел 46 смещения уровня на операционном усилителе, рабо-, тающем в режиме суммирования напряжения отсчетов сигнала с половиной , опорного напряжения, преобразователь до 47 код-ток, регистр 48 последовательных приближений и компаратор 49. Особенностью данной схемы является включение компаратора 49 в режиме сравнения токов. Диоды на его входе защища- 45 ют компаратор 49 от перегрузки.

Формирователь 7 кода содержит регистр 50 из четырнадцати Д-триггеров.

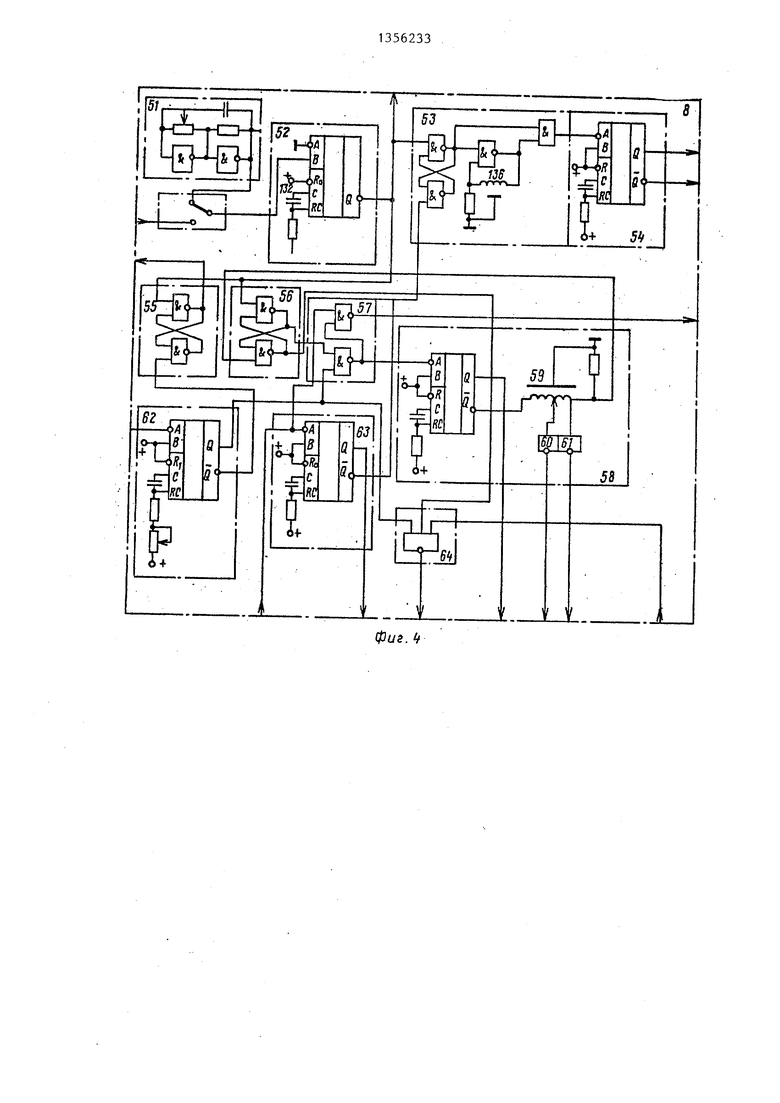

Блок 8 управления содержит: задающий генератор 51 импульсов, выполнен- gQ ный по схеме мультивибратора, первый формирователь 52 импульсов, выполненный в виде ждущего мультивибратора с времязадающими элементами, генератор 53 тактовых импульсов и второй gg формирователь 54. Формирователь 55 импульса управления блоком 5 коммутации и триггер 56 завершения первого цикла представляют собой R-триггеры,

35

Кроме 3Tgro, блок 9 формирован кода IfflJ содержит: цифровой компар

формирователь 57. Формирователь 58 импульсов синхронизации содержит жду- ПЦ1Й мультивибратор с времязадающими элементами и линию 59 задержки с отводами через О,1 МКС и два формирователя на элементах 60 и 61, формирователь 62 импульсов конца первого цикла и формирователь 63 импульсов конца преобразования выполнены аналогично первому формирователю 52 импульсов, формирователь 64 импульса обнуления памяти выполнен на элементе ЗИ-НЕ. Кроме этого, блок 8 управления содержит переключатель, обеспечивающи работу устройства для кодирования звуковых сигналов с инерционным ком- пандированием от внешней синхронизации (первьм вход блока 8 управления)

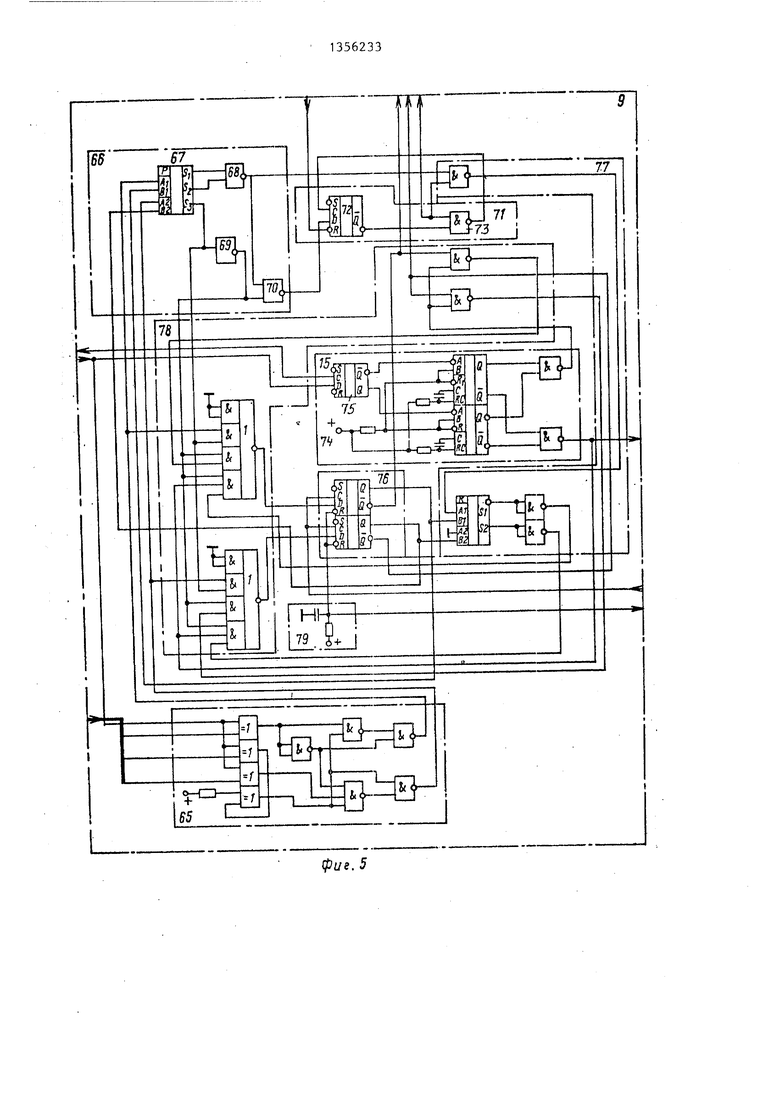

Блок 9 формирования кода ШЧ (фиг.5) включает в свой состав дешифратор 65 кода мгновенной шкалы (МШ).

Данное включение логических элементов реализует следующую таблицу

до 45

35

Кроме 3Tgro, блок 9 формирования кода IfflJ содержит: цифровой компаратор

66, выполненный на сумматоре 67 и элементах 68,69 н 70, блок 71 памяти признака, выполненный на D-триггере 72 и элементе 73, фор1 отрователь 74 импульса смены знака, выполненный на 1)-триггере 75 н двух мультивибраторах с времязадающими элементами, также регистр 76 кода ИШ, блок 77 уменьшения кода, выполненный на сумматоре, коммутатор 78, узел 79 начальной установки, содержащий резистор, подклго000000 000000 1

О О 00 ао 00 00 oi о

000000 000010 о

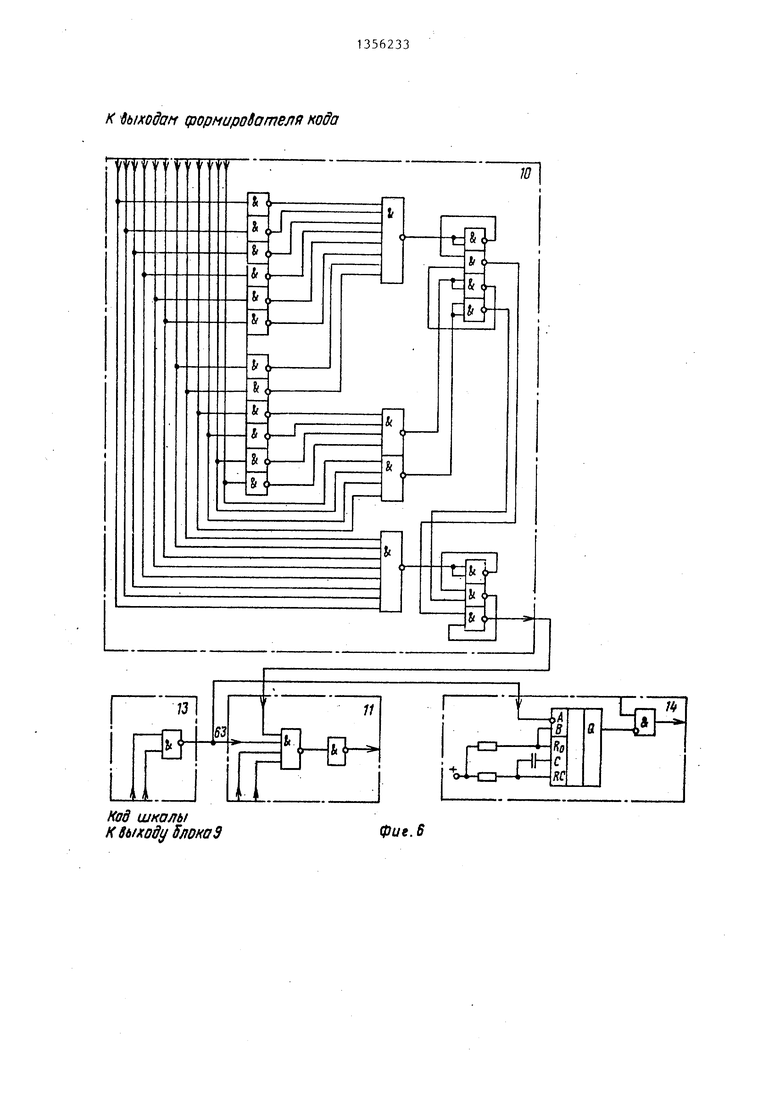

Первый блок 13 анализа кода шкалы представляет собой элемент совпадения по единицам. Первый блок 11 форми- рования СП выполнен на элементе совпадения и инверторе.

Первый блок 14 формирования СКП содержит ждущий мультивибратор с времязадающими элементами.

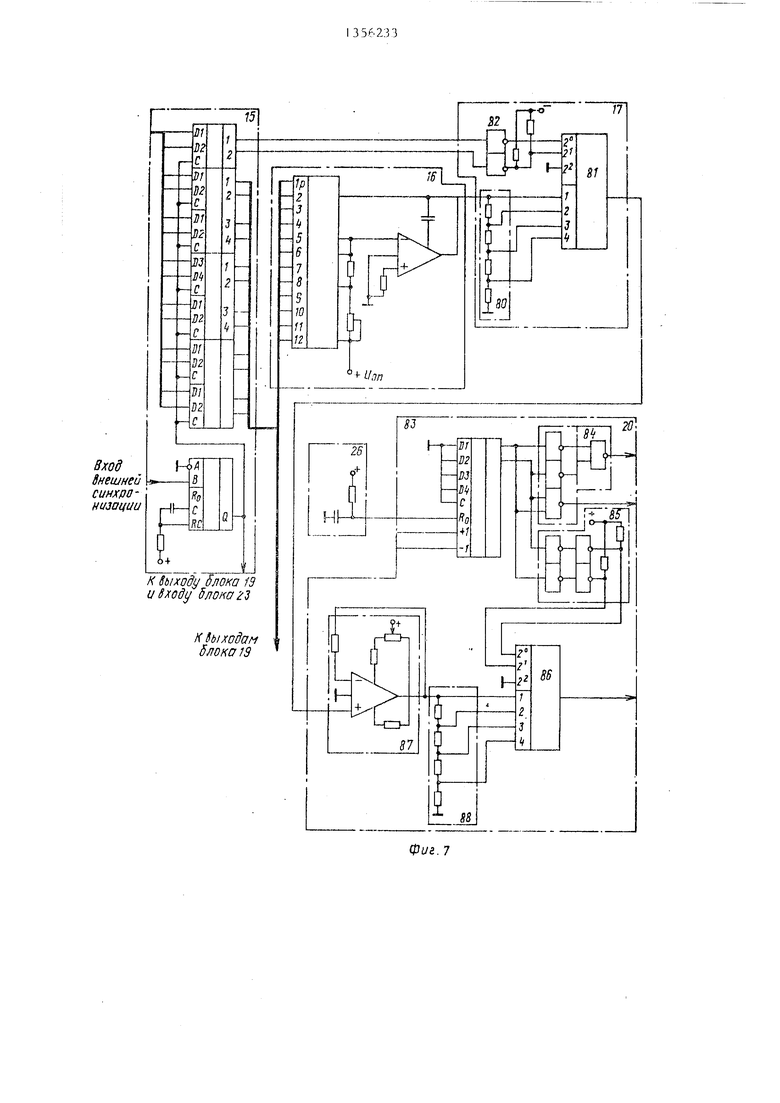

Схема входного регистра 15 кода, ЦАП 16, первого экспандера 17, управляемого второго экспандера 20 и блока 26 начальной установки приведены на фиг.7. Входной регистр 15 содержит собственно регистр и регенератор импульсов частоты дискретизации - мультивибратор с времязадающи1-м элементами. ПДП 16 содер /чИ г преобразователь

Q6233

к источнику напряжения, и конденсатор .

Схема первого блока 10 проверки разрядов на равнозначность, первого блока 13 анализа кода шкалы, первого блока 11 формирования СП и перврго блока 1 Сформирования СКП представлена на- фиг.б.Первьш блока 10 проверки разрядов на разнозначностьпредставляет собой комбинационную логическую схему,реализующую следующую таблицу истинности.

код-ток и сумматор токов, выполненный на операционном усилителе.

Первый экспандер 17 содержит ре- зистивную матрицу 80, аналоговьй мультиплексор 81 и формирователь 82 сигнала управления по уровню.

Блок 26 начальной установки содержит конденсатор и резистор и выполнен аналогично узлу 79 начальной установки блока 9 формирования кода ИШ (см.фиг.5).

Управляемый второй экспандер 20 (см.фиг.7) содержит реверсивный счетчик 83, в котором используются два младших разряда, узел 84 ограничения счета, формирователь 85 уровней сигнала управления, аналоговый мульти

штексор 86, буферный каскад 87 на операционном усилителе и резистивную матрицу 88.

Схема блока 23 задержки, блок 24 стробирования и второй усилитель 25 показана на фиг.8. Блок 23 задержки содержит мультивибратор с времязадаю щими элементами. Блок 24 стробирования выполнен аналогично блоку 3 дис- кретизации и хранения с той лишь разницей, что роль RS-триггера (см. фиг.2) выполняет мультивибратор 89 с времязадающими элементами (см. фиг.8). Второй усилитель 25 содержит пассивный трехзвенный LC-фильтр 90 кодера, аналогичный фильтру 28 в первом усилителе 2, и буферный каскад 91, собранный на операционном усилителе. Пот.енциометр 92 обеспечивает согласование выходного сигнала кодек с устройством-потребителем.

Техническая реализация второго блока 18 проверки разрядов на равнозначность, второго блока 19 формирования СП, второго блока 21 анализа кода шкалы и второго блока 22 формирования СКП на равнозначность, соответственно такая же, как и первого блока 10 проверки разрядов на равнозначность, первого блока 11 формирования СП, первого блока 14 формирования СКП.

Устройство работает следующим образом.

Аналоговый звуковой сигнал поступает на вход первого усилителя 2 (фиг.1), в котором усиливается и ограничивается по спектру С целью предотвращения перекрытия боковых полос ЗС при дискретизации, после чего поступает на вход блока 3 дискретизации и хранения. Далее работа устройства для кодирования ЗС с инерционным ком пандированием происходит следующим образом. При подаче питающего напряжения +5В конденсатор узла 79 начальной установки в блоке 9 формирования кода ИШ (см.фиг.5) и конденсатор блока 26 начальной установки (см.фиг.7) не могут мгновенно зарядиться до напряжения, равного уровню логической единицы +2,4 В. Постоянная времени цепи заряда конденсаторов узла 79 начальной установки и блока 26 начальной установки выбрана такой, чтобы на R-входах D-триггеров регистра 76 кода инерционной шкалы блока 9 формирования кода ИШ, на R-входе

15

20

25

- Q

356233о

реверсивного счетчика 37 (четвертьш вход управляемого аттенюатора 12) и на R-входе реверсивного счетчика 83 (четвертый вход управляемого второго экспандера 20) оставался уровень логического нуля на время, достаточное для установки указанных элементов в исходное нулевое состояние. Таким образом, в начале работы устройства на первых входах блока 4 масштабного усиления всегда устанавливается код 00, соответствующий самой точной шкале квантования. На выходе реверсивного счетчика 37 и, спедовательно, на управляющих входах аналогового мультиплексора 40 управляемого аттенюатора 12 устанавливается код 00 и точка нулевого затухания (см.фиг.2) управляемого аттенюатора 12 подключается к второму входу блока 4 масштабного усиления и к третьему входу блока 5 коммутации. Под воздействием блока 26 начальной установки на выходах реверсивного . счетчика 83 и соответственно на уп- равляюшдх входах аналогового мультиплексора 86 устанавливается кодовая комбинация 00. При этом управляе- мьм второй экспандер 20 включается в режим работы с минимальным коэффициентом передачи, так как сигнал снимается с нижней точки резистивной матрицы 88. Задающий генератор 51

35 импульсов блока 8 управления (фиг.4; запускается и на его выходе появля- ются прямоугольные импульсы с периодом 20,8 МКС (48 кГц) (фиг.Юа). Если переключатель (фиг.4) находится

40 в верхнем положении, то эти импульсы поступают на вход первого формирова- - теля 52 импульсов, где по их положительному фронту вьфабатываются короткие (длительностью 150 не) отрица45 тельные импульсы (фиг.ТО б). Наличие первого формирователя 52 импульсов обеспечивает возможность внешней синхронизации устройства с первого входа блока 8 управления любым импульс50 ным сигналом с частотой 48 кГц. Короткий отрицательный импульс поступает одновременно на второй вход блока 3 дискретизации и хранения как импульс начала выборки (ИНВ), на пер55 вьш вход генератора 53 тактовых импульсов, на формирователь импульсов управления блоком 5 коммутации и на первый входа триггера 56 завершения первого цикла.

30

С приходом ИНВ на второй вход блока 3 дискретизации и хранения (фиг.2) триггер-формирователь 31 импульса дискретизации устанавливается в единичное состояние. На коллекторе транзистора 35 формирователя 32 импульса управления ключом 33 появляется потенциал +15В. Ключ 33 открывается, и конденсатор 36 заряжается до напряжения ЗС и дапее отслеживает его изменения. Одновременно (фиг.4) R- триггер в формирователе 55 импульса управления блоком 5 коммутации (фиг.10 д) и триггер 56 завершения первого цикла устанавливаются в единичное состояние. При этом уровень логической единицы с четвертого выхода блока 8 управления поступает па второй вход блока 5 коммутации, кото- рьш подключает выход блока 3 дискретизации и хранения через уп равляемьй аттенюатор 12 к второму входу блока

4масштабного усиления и через блок

5коммутации к первому входу АЦП 6 (фиг.1). Уровень логической единицы с выхода триггера 56 завершения первого цикла (фиг.4) поступает на вход формирователя 57 импульсов начальной установки, на выходе которого устанавливается уровень логической единицы. На другом выходе формирователя 57 импульсов начальной установки устанавливается уровень логического нуля, так как с третьего выхода АДП 6 иа третий вход блока управления поступает уровень логического нуля. Уровень логического нуля (фиг.10 г) с выхода формирователя 57 поступает, с десятого в выхода блока 8 управления на третий вход АЦП 6, подготавливая таким образом регистр 48 последовательных приближений (фиг.З) к работе. Отрицательный импульс с выхода первого формирователя 52 импульсов поступает на вход 45 кого нуля с четвертого выхода блока

генератора 53 тактовых импульсов (фиг.4). При этом RS-триггер генератора 53 устанавливается в единичное состояние, в результате чего генератор 53 тактовых импульсов начинает вырабатывать прямоугольные импульсы в виде меандра, которые поступают на второй формирователь 54 импульсов. В последнем по отрицательным фронтам меандра формируются короткие положительные и отрицательные импульсы длительностью . 1 50 НС и периодом в 1 мкс (фиг.Юв). отрицательный импульс является ммпульсом конца выбор50

55

о управления поступает на второй вход блока коммутации, который подключает первый вход АДП 6 к выходу блока 4 масштабного усиления.Положительный импульс с другого выхода формирователя 62 импульсов конца пер вого цикла (фиг.4) поступает на формирователь 64 импульса обнуления памяти и на вход формирователя 57 импульсов начальной установки, на выходе которого возникается уровень логического нуля, а следовательно, и на третьем входе АДП ,6 (входе установки) , Одновременно отрицательный

0

5

0

5

5

0

ки (ИКВ), который с шестого выхода блока 8 управления поступает на третий вход блока 3 дискретизации и хранения. При этом RS-триггер 31 (фиг.2) возвращается в нулевое состояние, потенциал на коллекторе транзистора 35, формирователя 32 импульса управления снижается до -9В, ключ 33 закрывается. Напряжение сигнала, остав- на конденсаторе 36, хранится в течение всего времени преобразования отсчета.

Напряжение отсчета сигнала с выхода блока 3 дискретизации и хранения (фиг.1) поступает через управляемый аттенюатор 12 на второй вход блока 4 масштабного усиления и на третий вход блока 5 коммутации, с выхода которого отсчет поступает на первый вход АДП 6, где складывается на узле 46 смешения уровня (фиг.З) с половиной опорного напряжения. С пятого выхода блока 8 управления на второй вход AJjn 6 начинают поступать тактовые импульсы (фиг.10 в). В АДП 6 возникает процесс поразрядного уравно-- вешивания величины отсчета ЗС. С приходом пято.гр тактового импульса информация о четырех старших разрядах отсчета, необходимых для работы блока 9s становится известной, поэтому с четвертого выхода АЩ1 6 на четвертый вход блока 8 управления поступает отрицательный фронт импульса установки пятого разряда кода. По этому фронту в формирователе 62 импульсов конца первого цикла (фиг.4) вьфабаты- . в аются два импульса длительностью . 150 НС. Отрицательный импульс поступает на формирователь 55 импульсов управления блоком 5 коммутации, RS- триггер последнего устанавливается в нулевое состояние, и уровень логичес0

5

о управления поступает на второй вход блока коммутации, который подключает первый вход АДП 6 к выходу блока 4 масштабного усиления.Поло, жительный импульс с другого выхода формирователя 62 импульсов конца первого цикла (фиг.4) поступает на формирователь 64 импульса обнуления памяти и на вход формирователя 57 импульсов начальной установки, на выходе которого возникается уровень логического нуля, а следовательно, и на третьем входе АДП ,6 (входе установки) , Одновременно отрицательный

фронт с выхода элемента формирователя 57 импульсов начальной установки поступает на вход формирователя 58 импульсов синхронизации, который генерирует два импульса длительностью л/150 НС. Положительный импульс с седьмого выхода блока 8 управления (фиг-. 1) поступает на третий вход блока 9 . формирования кода ИШ, а отрицательный импульс поступает на вход линии 59 задержки.

Далее начинается определение ИШ в блоке 9 формирования кода ИШ (фиг.5), Второй, третий и четвертый разряды кода с первых выходов АЦП 6 поступают на вторые входы блока 9 формирования кода ИШ (фиг.1), на шестой вход которого с второго выхода АЦП 6 поступает инверсный первый разряд. В соответствии с табл.1 истинности, дешифратор 65 кода МШ блока 9 формирования кода ИШ вырабатывает двухразрядньй код, который поступает на входы цифрового компаратора 66 и коммутатор 78. В начальный момент времени могут сложиться две ситуации :

1) код ML1 с выхода дешифратора 65 кода МШ равен коду ИШ, записанному в регистре 76 кода ИШ

2) код МШ больше кода ИШ при усло- вии, что текущий отсчет не является отсчетом, в котором произошло измерение его полярности.

Тогда в первом случае цифровой компаратор 66 вьщает с J выхода сумматора 67 уровень логического нуля на коммутатор 78, запрещая прохождение

кода МШ на вход регистра 76 кода ИШ., 40 Рый записывается по импульсу с входа На выходе элемента 70 появляется уро- блока 9 формирования кода ИШ, при

этом блокируется дальнейшее поступление синхронизации на триг гер 72. Кроме этого, уровень логического нуля

вьтходе которого также устанавливается уровень логического нуля, предотвращая возможность уменьшения кода ИШ

вень логической единицы. В этот момент с восьмого выхода блока 8 управ- ,Ленин (фиг.1) на четвертьй вход блока 9 формирования кода :ИШ (фиг.5) подает-дб с выхода триггера 72 поступает на ся положительньй синхроимпульс дли- элемент блЬка 77 уменьшения кода, на тельностью 150 не (см.фиг.10 ж), по которому Д-триггер 72 блока 71 памяти признака записывает -информацию с выхода элемента 70. На выходе Д-тригге- 50 Д° момента полярности сигнала, ра 72 появляется уровень логического Таким образом, в блок 71 памяти при- нуля, который запирает элемент 73, энака записана информация о том, что запрещая дальнейшее прохождение син- код МШ был хотя бы раз больше кода хроимпульсов на С-вход Д-триггера 72. ИШ, а в регистр 76 кода ИШ в этом Таким образом, в блоке 71 памяти при- 55 Учае записывается код МШ. знака записана информация о том, что После записи кода в регистр 76 ко- код МШ был равен коду ИШ.-да ИШ блока 9 он поступает на управТак как в рассматриваемом отсчете ляющие блока 4 ма1сштабного уси- не произошло изменение полярности ко- ления (фиг.1), в котором устанавли

дируемого сигнала, на выходе первого элемента формирова еля 74 иьшульса смены знака будет уровень логической единицы, который открывает элементы коммутатора 78, а на выходе второго элемента формирователя 74 импульса смены знака - уровень логического нуля, который запрещает прохождение кода с выхода блока 77 уменьшения кода через коммутатор 78 на вход регистра 76 кода 1Ш.

Поэтому через 100 не, с приходом второго синхроимпульса (фиг.ТО з)

g с девятого выхода блока 8 управления на пятьй вход блока 9 формирования кода ИШ с выходов регистра 76 кода ИШ через открытые элементы коммутатора 78 (см.фиг.5) поступает на D-входы регистра 76 кода ИШ и записывается в него. Во втором случае, когда код ЩI с выхода дешифратора 65 кода МШ больше кода ИШ, записанного первоначально в регистр 76 кода ИШ, цифро5 вой компаратор 66 на Р -выходе сумматора 67 вьщает уровень логической единицы, разрешая прохождение кода МШ через коммутатор 78 на вход регистра 76 кода ИШ. В то же время уровень логического нуля с выхода элемента 69 цифрового компаратора 66 запрещает прохождение через коммутатор 78 на вход регистра 76 кода ИШ как кода, записанного в нем ранее, так и кода ИШ с выходов блока 77 уменьшения кода. Уровень логической единицы с выхода элемента 70 цифрового компаратора 66 поступает на D-вход триггера 72 блока 71 памяти признака, в кото0

0

5

ме этого, уровень логического нуля

с выхода триггера 72 поступает на элемент блЬка 77 уменьшения кода, н Д° момента полярности сигнала Таким образом, в блок 71 памяти при энака записана информация о том, чт код МШ был хотя бы раз больше кода ИШ, а в регистр 76 кода ИШ в этом Учае записывается код МШ. После записи кода в регистр 76 к да ИШ блока 9 он поступает на управ

вьтходе которого также устанавливается уровень логического нуля, предотвращая возможность уменьшения кода ИШ

с выхода триггера 72 поступает на элемент блЬка 77 уменьшения кода, на Д° момента полярности сигнала, Таким образом, в блок 71 памяти при- энака записана информация о том, что код МШ был хотя бы раз больше кода ИШ, а в регистр 76 кода ИШ в этом Учае записывается код МШ. После записи кода в регистр 76 ко- да ИШ блока 9 он поступает на управ

31

вается один из возможных коэффициентов усиления напряжения отсчета. Далее напряжение отсчета через блок 5 коммутации поступает на вход АЦП 6. С приходом шестого тактового импульс с пятого выхода блока 8 управления на второй вход А1Щ 6 (фиг.З) производится вторичная установка регистра 48 последовательных приближенирЧ и за тем последовательное уравновешивание напряжения отсчета, как описано выше Разница заключается только в том, чт теперь во втором цикле преобразовани определяются все 12 разрядов кода (используются тактовые импульсы с 7по 19-й). По окончании процесса поразрядного уравновешивания с третьего выхода АЦП 6 на третий -зход блока

8управления вьщается отрицательный перепад напряжения, по которому в . формирователе 63 импульсов конца преобразования вырабатывается два коротких импульса длительностью 150 не. Положительный импульс с третьего выхода блока 8 управления поступает на третий вход формирователя 7 кода (фиг.10 е), по которому производится запись 12-разрядной мантиссы с первы выходов АЦП 6 и 2-разрядного кода порядка с первых выходов блока 9 формирования кода И11 в регистр 50 (фиг.З) Отрицательный импульс с другого выхода формирователя 63 импульсов преобразования блока 8 управления (фиг.4) поступает на генератор 53 тактовых импульсов, RS-триггер возвр щается в нулевое состояние, срывая работу тактового .генератора . Устройство ждет прихода следующего запускающего импульса задающего генератора 5 1 .

Рассмотрим работу устройства в случае уменьшения уровня сигнала. При уменьшении уровня сигнала смена кода шкалы происходит только в течение первого отсчета противоположной полярности.. Предположим, что уровень сигнала уменьшается и за время между двумя последовательными сменами полярности отсчетов подтверждения кода ИШ не произошло ни разу. Это означает, что цифровой компаратор 66 блока

9формирования кода ИШ (фиг.5) за весь определенный выше интервал времени ни разу не вьщал на Д-вход Д- триггера блока 71 памяти признака сигнала логической единицы. Блок 71 памяти признака обнулен отрицательны

15

0

5

6233

Q

14

импульсом, пришедшим на его (Д-триг- гера R-вход) первый вход блока 9 формирования кода ИИ) с первого выхода блока 8 управления. Импульс обнуления вырабатывается в формирователе 64 импульса обнуления (фи1 .4) во втором цикле преобразования каждого первого отсчета противоположной полярности. Это происходит следующим образом. В первом цикле после установки пятого разряда регистра 48 последовательных приближений в АЦП 6 отрицательный фронт с четвертого вь1хода АЦП 6 поступает на четвертый вход блока управления 8 (см.фиг.1), по которому формирователь 62 импульсов конца первого вырабатывает два импульса. Отрицательный импульс поступает на формирователь 55 импульса управления блоком 5 коммутации, что обеспечивает подключение выхода блока 4 масш-. табного усиления к первому входу АЦП 6. Поломсительный импульс с выхода формирователя 62 импульса конца первого цикла (фиг.4) поступает на один из входов формирователя 64 импульсов обнуления. В течение времени между и шестым тактовыми импульсами с выхода формирователя 58 импульсов синхронизации на триггер 56 завершения первого цикла поступает импульс, возвращая его в нулевое состояние, что обеспечивает, с одной стороны, возможность работы формирователя 57, а с другой, выдает уровень логической едини ды на второй вход формирователя 64 импульсов обнуления памяти, третий вход которого, я зляюш;ийся вторым входом блока 8 управления, подключен к второму входу блока 9 формирования кода ИШ к формирователю 74 импульсов смены знака (фиг.5). Последний работает следующим образ(зм.

Первый инверсный разряд кода с второго выхода АЦП 6 поступает на шестой вход блока 9 формирования кода ИШ. Здесь он по синхр оимпульсу, приходящему с седьмого выхода блока 8 управления на третий вход блока 9 формирования кода ИШ, записывается в Д-триггер 75 (формирователя 74 импульса смены знака), выходы которого подключены к входам мультивибраторов формирователя 74. Последние вьграбаты- вают импульсы,- которые затем замешиваются на его элементах. Положительные импульсы с выхода формирователя 74 поступают на вторые входы блока

0

0

5

0

8 управления. Ясно, что если на всех трех входах формирователя 64 импульса обнуления памяти окажутся уровни логической единицы, то на его выходе возникнет отрицательный импульс, ,ко- Topbtfi и обнулит Д-триггер 72 блока 71 памяти признака (фиг.10 к). На выходе блока 71 памяти признака (фиг.5) будет уровень логической единицы, он будет также и на выходе элемента блока 77 уменьшения кода, так как на выходе элемента 68 цифрового компаратора 66 также уровень логической единицы. Поэтому на выходах блока 77 уменьшения кодов будет значение кода ИШ, уменьшенное на единицу. Этот код через коммутатор 78 поступит на вход регистра 76 кода ИШ, -куда будет записан по синхроимпульсу с девятого выхода блока 8 управления.

Рассмотрим работу остальных блоков на передающей стороне кодека ЗС с инерционным компандированием. Если уровень сигнала на выходе источника 1 сигнала по какой-либо причине не превысил значение -18 дБ относительно приведенного к входу максимального уровня квантования АЦП 6, то ЗС начинает клиппироваться, вследствие чего возникают шумы перегрузки. Факт клип- пирования сигнала определяется по двум признакам. Во-первых, 12-разрядная мантисса ИКМ-слова на выходе формирователя 7 кода должна содержать либо все единицы для положительной полуволны сигнала, либо все нули - для отрицательной. Во-вторых, клиппи- рование ЗС может происходить только на самой грубой шкале квантования, обозначенной в данном кодеке кодом 11.

С выхода формирователя 7 кода код мантиссы поступает на вход первого блока 10 проверки разрядов на равнозначность. В случае клиппирования ЗС код мантиссы состоит из всех единиц или нулей и тогда в соответствии с табл.2 истинности работы первого блока 10 проверки разрядов на равнозначность появляется уровень логической единицы, который поступает на первый вход первого блока 11 формирования СП. В то же самое время на входы первого блока 13 анализа кода шкалы с первого выхода блока 9 формирования кода ИШ поступает код шкалы в виде 11. Тогда на его выходе появляется уровень логической единицы, который

5

Q g

0

поступает на первый вход первого блока 14 формирования СКП и на третий вход первого блока 11 формирования СП. В начальный момент, как отмечалось вьшзе, реверсивный счетчик 37 в управляемом аттенюаторе 12 бьш установлен в нулевое состояние, поэтому на первом выходе управляемого аттенюатора 12 уровень логического нуля, который поступает на второй вход первого блока 14 формирования СКП, заг прещая прохождение импульсов с выхода первого блока 14 формирования СКП на третий вход управляемого аттенюатора 12. С второго же выхода управляемого аттенюатора 12 на четвертый вход первого блока 11 формирования СП подается уровень логической единицы.

0 Поэтому с приходом очередного строби- рующего импульса дискретизации с первого выхода блока 3 дискретизации и хранения (где он формируется триггером-формирователем 31, см.фиг.2)

5 на второй вход первого блока 11 формирования СП на его выходе появляется положительный импульс, который поступает на первый вход управляемого аттенюатора 12, т.е. на суммирующий вход реверсивного счетчика (см.фиг.2), который увеличивает значение кода на своем выходе на единицу. Код с выхода реверсивного счетчика 37 поступает на управляющие входы аналогового мультиплексора 40 через формирователь 39 уровней сигнала управления, вследствие чего отсчеты ЗС начинают поступать на второй вход блока 4 масштабного усиления и третий вход блока 5 коммутации с затуханием в 6 дБ. Клип- пирование сигнала прекращается. Если уровень сигнала на выходе источников сигнала 1 продолжает расти, то устройство отрабатывает увеличение сигнала аналогично. При этом каждое двойное увеличение уровня сигнала сопровождается увеличением кода в реверсивном счетчике 37 управляемого аттенюатора 12 на единицу, что соответствует увеличению сигнала на 6 дБ. Передавать дополнительную информацию о состоянии реверсивного счетчика 37 в управляемом аттенюаторе 12 (а следовательно, и величину внесенного затухания управляемым аттенюатором 12) нет необходимости, так как на приемной стороне (в декодере) установлены аналогичныеоблоки - второй блок 18 проверки разрядов на равнозначность,

5

0

5

1зторой блок 19 формирования СП, второй блок 21 анализа кода шкалы и второй блок 22 формирования СКП, на соответствующих входах которых присут- ствуют в момент возникновения перегрузки точно такие же сигнаг(ы.

В исходное состояние система защиты устройства от перегрузки возвращается следующим образом.

При уменьшении уровня входного сигнала код шкалы на выходе блока 9 формирования кода инерционной шкалы обязательно уменьшается на единицу, т.е. изменяется с 11 на 10, по- этому на выходе первого блока 13 анализа кода шкалы устанавливается уровень логического нуля, который поступает на третий вход первого блока 11 формирования СП и блокирует его и на первый вход первого блока 14 формирования СКП. В последнем по отрицательному фронту ждущий мультивибратор вырабатывает положительный импульс длительностью 1 мкс, которьм поступает на третий вход управляемого аттенюатора 12 (вычитающий вход реверсивного счетчика 37). Содержимо реверсивного счетчика (код) уменьшается на единицу и поступает на управ ляющие входы аналогового мультиплексора 40, который уменьшает затухание отсчета ЗС, подключаемого к входу блока 4 масштабного усиления и блоку 5 коммутации, на 6 дБ.

В процессе работы устройства на выходах реверсивного счетчика 37 управляемого аттенюатора 12 могут возникнуть следующие кодовые комбинации 00, 01, 10, 11. Комбинации 00 и 11 являются граничными. Однако импульсы сигнала перегрузки на выходе первого блока 10 проверки разрядов на равнозначность и на выходе первого блока 13 анализа кода шкалы могут возникнуть и после установки последней разрешенной кодовой комбинации 11. При этом реверсивный счетчик 37 с комбинации 11 сразу переходит на комбинацию 00. Чтобы этого не происходило, в управляемом аттенюаторе 12 установлен узел 38 ограничения счета импульсов, который в этом случае блокирует прохождение счетных импульсов через первьй блок 11 формирования СП по его четвертому входу (суммируюшзий вход реверсивного счетчика 37). Аналогично блокируется прохождение импульсов с выхода перво

5 0 5 О

0 5 0 g

5

го блока 14 формирования СКП на вычитающий вход реверсивного счетчика 37 при появлении на его выходе кодовой комбинации 00. В то же время увеличение уровня сигнала, связанное с переходом из комбинации 00 в 11, и снижение сигнала, связанное с переходом из комбинации 11 в 00, может происходить сколь угодно часто.

На этом обработка сигнала на передающей стороне устройства для кодирования ЗС с инерционнь м компандирова- нием заканчивается. Рассмотрим работу приемной стороны./

Как отмечалось вьпие, в момент подачи питающих напряжений конденсатор (см.фиг.7) в блоке 26 начальной установки не может мгновенно зарядиться до напряжения единицы, что обеспечивает установку реверсивного счетчика 83 управляемого второго экспандера 20 в нулевое состояние. При поступлении на вход внешней синхронизации входного регистра 15 кода импульсного сигнала с частотой 48 кГц по его положительному фронту мультивибратор вырабатывает положительные импульсы длительностью 1 мкс, которые поступают на второй вход второго блока 19 формирования СП и на вход блока 23 за- задержки и формирования импульса стробирования. Кроме того, импульсы с выхода мультивибратора регистра 15 кода поступают на синхровходы собственно регистра, в которьм по ним записывается 14-разрядньй код величины отсчетов ЗС, поступающий с первых входов входного регистра 15 кода, которые являются информационными входами декодера; С выхода регистра 15 кода 12-разрядный код мантиссы поступает на ПДП 16, где преобразуется в пропорциональное величине кода напряжение отсчета, а два разряда порядка поступают на управляющие входы первого экспандера 17. Код порядка через формирователь 82 сигнала управления по уровню поступает на аналоговый м льтиплексор 81, который в зависимости от величины кода устанавливает коэффициент передачи, необходимый для восстановления исходного напряжения отсчета. Аналоговьш дискретный сигнал с выхода первого экспандера 17 далее через управляемый второй экспандер 20, коэффициент передачи которого в исходном состоянии минимальный, поступает на второй вход

19

блока 24 стробирования, на первый вход которого с выхода блока 23 задержки поступают положительные импульсы. Мультивибратор блока 23 задержки вырабатывает положительный импульс длительностью 10 мкс (относительно заднего фронта иМпульса дискретизации) , а мультивибратор 89 блока 23 стробированием относительно, его заднего фронта вырабатывает два противофазных импульса стробирования длительностью 2-3 мкс, которые и управляют работой ключа блока 24 стробирования. Таким образом, блок 24 стробирования формирует тот же по величине отсчет сигнала, но по той части отсчета, которая свободна от импульсных помех и наводок, связан13

ных с работой ЦАП 16, первого экспан- 20 го блока 21 анализа кода шкалы поя- дера 17 и управляемого второго экспандера 20. Очищенный сигнал с выхода блока 24 стробирования поступает на второй усилитель 25, где фильтруется от продуктов дискретизации фильтром 90 и нормируется по амплитуде.

Как отмечалось вьше, для правильной работы декодера в момент возникновения перегрузки кодера на приемную зо сторону не нужно передавать дополнительной информации, так-как здесь , установлены блоки, аналогичные блокам 10,11,13 и 14, - блоки 18,19,21 и 22. Действительно, если на входы второго блока 18 проверки разрядов на равнозначность поступит комбинация из 12- ти нулей или из 12-ти единиц, а на входы второго блока 21 анализа кода шкалы код 11 (а они будут присутствовать в момент начала перегрузки, так как передаются на приёмную сторону) , то на выходе указанных блоков будут уровни логических единиц. Эти сигналы поступают на первый вход и на третий вход второго блока 19 формирования СП, на второй вход которого поступает положительный импульс дискретизации с третьего выхода входвится уровень логического нуля, который блокирует по третьему входу второй блок 19 формирования СП, и одновременно по отрицательному фрон25 ту на первом входе второй блок 22

формирования СКП вырабатывает на сво ем выходе положительный импульс, который поступает на третий вход управ ляемого второго экспандера 20 (на вычитающий вход реверсивного счетчик 83). Код в реверсивном счетчике уменьшится на единицу и поступит на управляющие входы аналогового мультиплексора, переключая его сигналь2g вые входы таким образом, что аналого вый сигнал на третьем входе управляемого второго экспандера уменьшится на 6 дБ.

Назначение и работа узла 84 ограничения счета импульсов аналогично устройству 38 ограничения счета им- пульсов в управляемом аттенюаторе 12

40

45

Формула изобретения

Устройство для кодирования звуковых сигналов с инерционным компанди- р-ованием, содержащее на передающей стороне последовательно соединенные

кого регистра 15 кода, а на четвертом 50 источник сигнала, первый усилитель входе в начальный момент установлен и блок дискретизации и хранения, уровень логической единицы. На выходе второго блока 19 формирования СП возникает положительный импульс, который поступает на первьй вход управ- gg штабного усиления, блок коммутации, ляемого аттенюатора - на суммирующий аналого-цифровой преобразователь, вход реверсивного счетчика 83, увеличивая код на выходе последнего на единицу. При этом код с выхода реверк второму входу которого подключен первый выход блока управления, последовательно соединенные блок маси формирователь кода, второй выход блока управления подключен к первом входу блока формирования кода ине р

35623320

сивного счетчика 83 поступает на управляющие входы аналогового мультиплексора 86, переключая его сигнальные входы таким образом, что аналоговый сигнал на третьем выходе управляющего второго экспандера 20 увеличивается вдвое (на 6 дБ). Если уровень сигнала на выходе источника 1

10 сигнала (см.фиг.1) продолжает расти, то устройство отрабатывает его аналогично .

В исходное состояние система защиты кодека от перегрузки на приемной

15 стороне возвращается аналогично тому, как было описано для передающей стороны. Действительно, при уменьшении кода порядка на втором выходе входного регистра 15 кода на выходе второго блока 21 анализа кода шкалы поя-

вится уровень логического нуля, который блокирует по третьему входу второй блок 19 формирования СП, и одновременно по отрицательному фронту на первом входе второй блок 22

формирования СКП вырабатывает на своем выходе положительный импульс, который поступает на третий вход управляемого второго экспандера 20 (на вычитающий вход реверсивного счетчика 83). Код в реверсивном счетчике уменьшится на единицу и поступит на управляющие входы аналогового мультиплексора, переключая его сигнальвые входы таким образом, что аналого-, вый сигнал на третьем входе управляемого второго экспандера уменьшится на 6 дБ.

Назначение и работа узла 84 ограничения счета импульсов аналогично устройству 38 ограничения счета им- пульсов в управляемом аттенюаторе 12.

Формула изобретения

Устройство для кодирования звуко вых сигналов с инерционным компанди- р-ованием, содержащее на передающей стороне последовательно соединенные

источник сигнала, первый усилитель и блок дискретизации и хранения, штабного усиления, блок коммутации, аналого-цифровой преобразователь,

к второму входу которого подключен первый выход блока управления, последовательно соединенные блок масисточник сигнала, первый усилитель и блок дискретизации и хранения, штабного усиления, блок коммутации, аналого-цифровой преобразователь,

и формирователь кода, второй выход блока управления подключен к первому входу блока формирования кода ине р21

вторым входам котоционнои шкалы, к рого подключены первые выходы аналого-цифрового преобразователя, первы вр)1ходы блока формирования кода инерционной шкалы - к первым входам блока масштабного усиления и к вторым входам формирователя кода, к третье fy входу которого подключены третий выход блока управления, четвертый и пятый выходы которого подключены соответственно к вторым входам блок коммутации и аналого-цифрового пре- Ьбразователя, при этом первый вход блока управления является входом внешней синхронизации передающей чати устройства для кодирования звуковых сигналов с инерционным компанди рованием, а выходы формирователя кода являются информационным - выходам передающей части устройства для кодирования звуковых сигналов с инерционным компандированием, на приемной стороне - последовательно соединенные входной регистр кода, первые входы которого являются информационными входами, а второй вход - входом внешней синхронизации приемной части устройства для кодировани звуковых сигналов с инерционным ком пандированием, цифроаналоговый преобразователь и первый экспандер, к управляющим входам которого подключены вторые выходы входного регистр кода, а также второй усилитель, выход которого является аналоговым выходом устройства для кодирования звуковых сигналов с инерционным ком пандированием, отличающее с я тем, что, с це льЕо повышения качества передачи путем уменьшения нелинейных искажений, связанных с ограничением сигнала, на передающей стороне введены последовательно соединенные первый блок проверки разря цов на равнозначность, к входам которого подключены выходы формирователя кода, первьш блок фopмIipoвaния сигнала перегрузки, к второму входу которого подключены первьш выход блка дискретизаи;ии и хранения, и уп- paвляe Iый аттенюатор, к второму входу которого подключен второй выход блока дискретизации и хранения, к третьему входу которого подключен шестой выход блока управления, к второму входу и седьмому, восьмому и девятому выходам которого подключны соответственно второй выход, тре

0

0

5

22

тий, четвертый и пятый входы блока формирования кода инергщонной шкалы, к шестому входу которого подключен второй выход аналого-цифрового преобразователя, к третьему входу которого подключен десятый выход блока управления, к третьему и четвертому входам которого подключены третий и четвертый выходы арталого-цифрового преобразователя 5 и последовательно соединенные первый блок анализа кода шкалы, к входам которого подключены первые входы блока масштабного уси- 5 Ленин, и первый блок формирования

сигнала конца перегрузки, первый вход которого подключен к третьему входу первого блока формирования сигнала перегрузки, а второй вход и выход подключен к пepвo ry выходу и третьему входу управляемого аттенюатора, второй выход которого подключен к четвертому входу первого блока формирования сигнала пе)егрузки,, при этом третий выход управляемого атте- Ешатора подключен соответственно к второму входу блока масштабного усиления и третьему входу блока коммутации, а к четвертому входу - третий вьгход блока формирования кода инерционной игкалы, на приемной стороне последовательно соединенные второй блок проверки разрядов на равнозначность, к входам которого подключены первые выходы входного регистра кода, второй блок формирования сигнала перегрузки, к второму входу которого подключен третий вькод входного регистра кода и управляемый второй экспандер, к второму входу которого подключен вьгход первого экспандера, последовательно соединенные второй блок анализа кода шкалы, к управляющим входам которого подключены вторые выходы входного регистра кода, и второй блок формирования сигнала конца перегрузки, к первому входу которого подключен третий вход второго блока формирования сигнала перегрузки, к четвертому входу которого подключен первый выход управляемого второго экспандера, второй вы- ход и третий вход которого подключены соответственно к BTopoNry входу и выходу второго блока формирования сигнала конца перегрузки, а также блок начальной установки, выход ко- торого подключен к четдертоьгу входу управляемого второго экспандера.

0

6

Ь

О

5

23135623324

и последовательно соединенные блок входу которого подключен третий вы- задержки, к входу которого подключен ход управляемого второго экспандера, третий выход входного регистра кода, а к выходу - вход второго уси- и блок стробирования, к второму лителя.

От источника сигнала Г

Фи. г

хц.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1987 |

|

SU1450113A2 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1984 |

|

SU1197085A1 |

| Устройство для кодирования аналоговых сигналов | 1985 |

|

SU1316091A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1983 |

|

SU1109848A1 |

| Устройство для цифрового компандирования звуковых сигналов | 1981 |

|

SU1030975A1 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Устройство цифровой передачи и приема телевизионного сигнала | 1985 |

|

SU1309327A1 |

| Устройство для ввода информации | 1989 |

|

SU1645949A1 |

| Устройство автоматической дискретной регулировки чувствительности радиоприемника | 1989 |

|

SU1748226A1 |

| УЛЬТРАЗВУКОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1991 |

|

RU2035692C1 |

Изобретение м.б. использовано в цифровых звуковых трактах телерадиовещания, в системах дискретной обработки звуковых сигналов. Цель изобретения - повышение качества пе- редачи путем уменьшения нелинейных искажений, связанных с ограничением сигнала. Устр-во содержит на передающей стороне источник 1 сигнала, усилитель 2, блок 3 дискретизации и хра(Л со ел Oi ts: со со

жФ

/

f9

„..J

Г

С1 шHZ с зщс таг

t

50

1 2 3

ТТ 3 f

ЮЕЮ

1 Z

физ. 3

фиб. ff

(риг, 5

К Sbixodafi дзормироботеля кода

Код шкалы KSdixDdydflDHaS

фие.6

Вход Йнешней синхронизации

фуг. 7

К третеми Пыходу блока tS и txoffu ешо S

Аналогобыи Sыход ист- ройстйо

00 01

фие.8

Монета иш Ю

и

О niS 1/8

. ДиапазонЗО

Ц2

и

Редактор М. Цнткнна

иг. Ю

Составитель Л. Тимошина

Техред Л.Сердюкова Корректор у. Муска

Заказ .5813/55Тираж 636

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

IIp()Извoдcтne нo-пoJПIгpaфичecкoe предприятие, г. Ужгород, ул. Проектная, А

Подписное

| Ванде-Кирков В.В | |||

| Матвеев Н.Е., Устинова Л.Б | |||

| Кодекс звуковых сигналов с инерционным компандированием.- Техника радиовещательного приема и акустики, 1984, вып.1, с.54-63. |

Авторы

Даты

1987-11-30—Публикация

1985-12-11—Подача