Изобретение относится к области радиоэлектроники и может быть использовано для усовершенствования цифровых устройств, основанных на использовании модульных конструкций.

Известны методы улучшения основных технико-экономических показателей цифровых узлов, основанные на использовании прогрессивной технологии. В связи с интенсивным внедрением прогрессивных методов производства микроэлектронных схем особенно быстро возникла задача минимизации функциональных связей и межмодульных соединений. Это обусловлено прежде всего тем фактом, что надежность полупроводниковых интегральных схем в отличие от схем на обычных дискретных компонентах мало зависит от их сложности и определяется, в основном, качеством сборки и количеством внешних связей.

Достигнутый мировой уровень производства интегральных схем на МОП-структурах позволяет в массовом масштабе реализовать на одной пластине кремния размером до 15 мм схемы, содержащие до 1000 полевых транзисторов. Для упаковки интегральных схем используют видоизмененные круглые транзисторные или плоские корпуса, имеющие 10-16 выводов. Если учесть, что обычно три вывода должны использоваться для питания схем, то для функциональных связей остается

всего 7-13 выводов. Так как количество внешних выводов ограничено технологическими соображениями, то при конструировании модулей на интегральных схемах, и в первую очередь со структурой МОП, этот фактор является существенно ограничивающим как с точки зрения дальнейщего улучшения технологичности и надежности, так и с точки зрения дальнейщего снижения габаритов и веса. Поэтому при реализации схем на основе модульных конструкций пытаются использовать всевозможные способы сокращения функциональных соединений и, по возможности, количества модулей.

Известны также способы уменьшения числа межмодульных соединений и корпусов, основанные на создании и на использовании высокоэффективных многовходных логических схем. Под эффективностью в данном

случае понимают возможность реализации в данной схеме достаточно большого числа логических операций с меньшим числом переменных.

Недостатком известных способов является

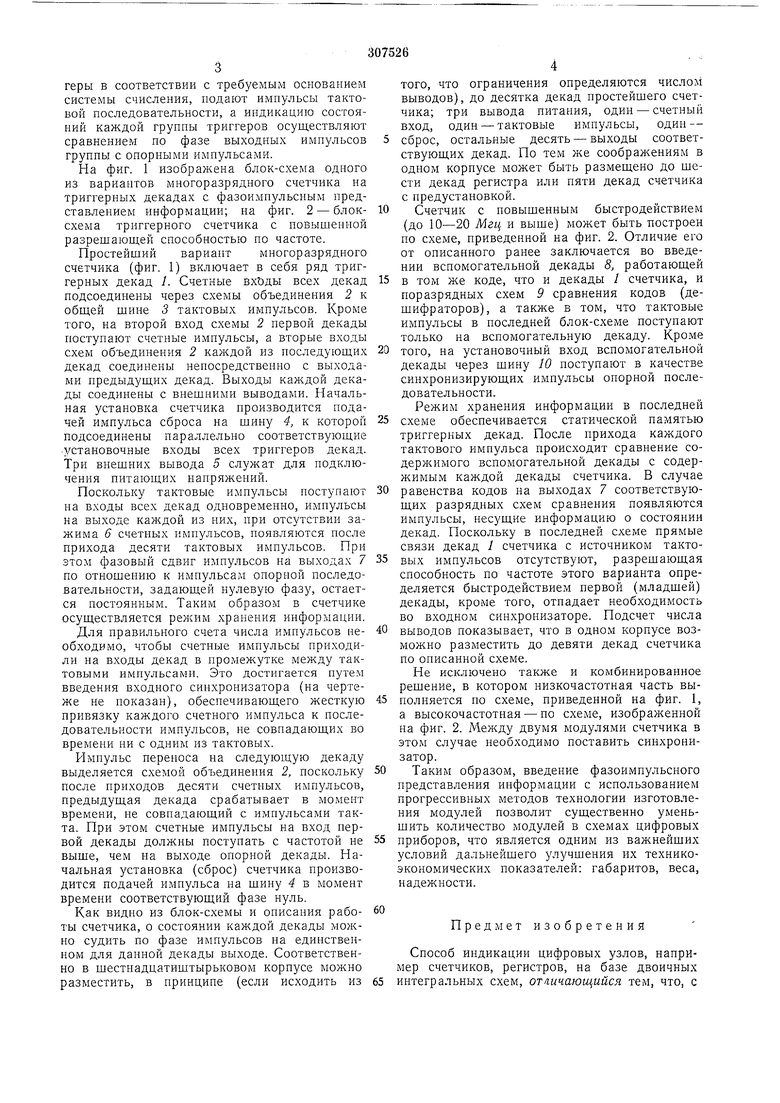

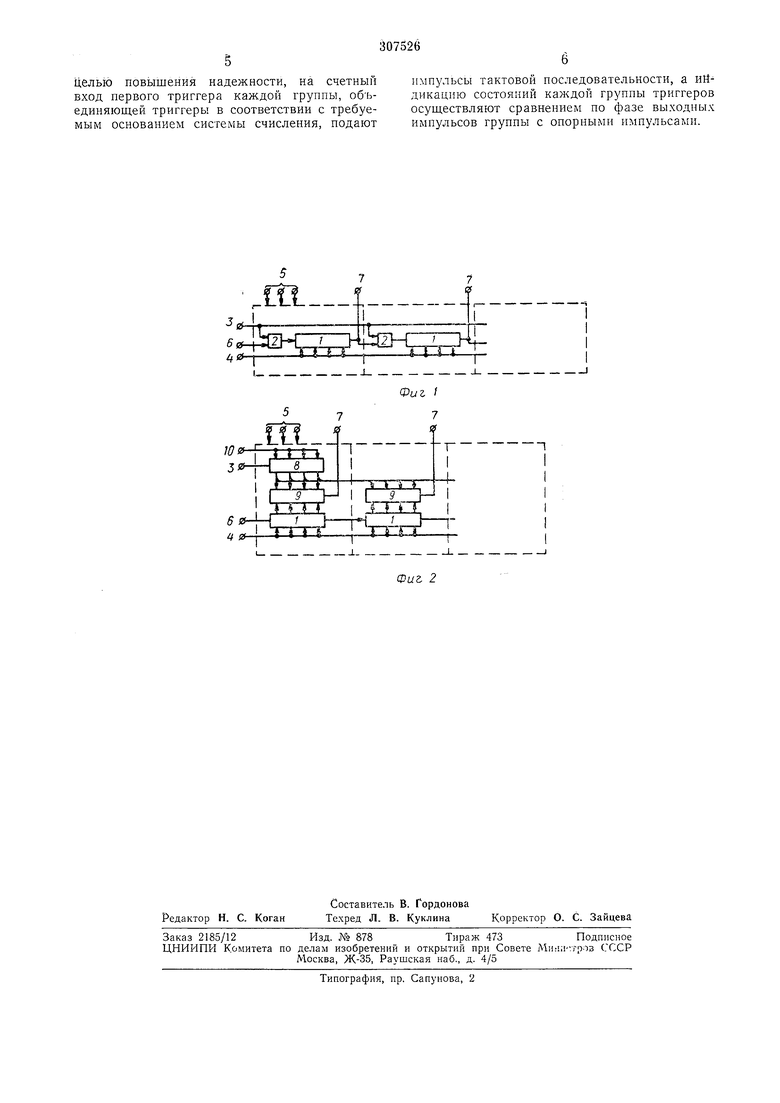

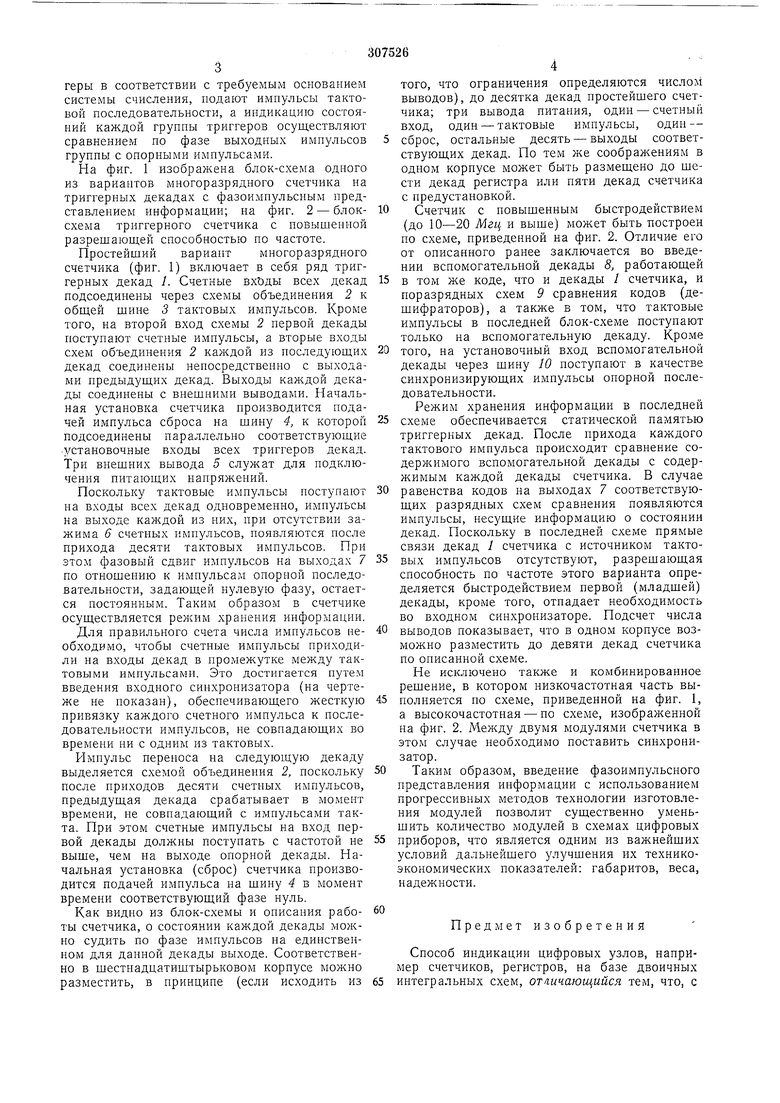

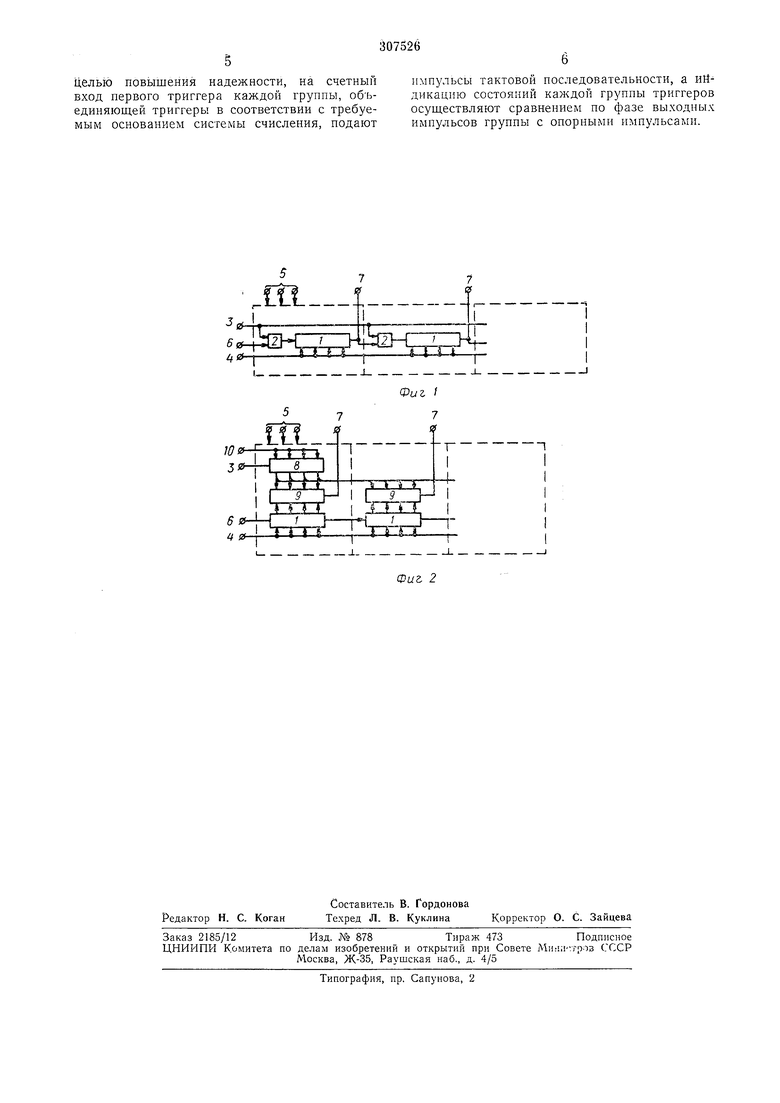

сравнительно малая эффективность и, кроме того, сложность отыскания критериев оценки логической эффективности модулей. геры в соответствии с треоуемым основанием системы счисления, подают импульсы тактовой последовательпости, а ипдикапию состояний каждой группы триггеров осуществляют сравнением по фазе выходных импульсов группы с опорными импульсами. На фиг. 1 изображена блок-схема одного из вариантов многоразрядного счетчика на триггерных декадах с фазоимпульсным представлением информации; на фиг. 2 - блоксхема триггерного счетчика с повышенной разрешающей способностью по частоте. Простейший вариант многоразрядного счетчика (фиг. 1) включает в себя ряд триггерных декад 1. Счетные вхЬды всех декад подсоединены через схемы объединения 2 к общей шине 3 тактовых импульсов. Кроме того, на второй вход схемы 2 первой декады поступают счетные импульсы, а вторые входы схем объединения 2 каждой из последующих декад соединены непосредственно с выходами предыдущих декад. Выходы каждой декады соединены с внешними выводами. Начальная установка счетчика производится подачей импульса сброса на шину 4, к которой подсоединены параллельно соответствующие установочные входы всех триггеров декад. Три внешних вывода 5 служат для подключения питающих напряжений. Поскольку тактовые импульсы поступают на входы всех декад одновременно, имнульсы на выходе каждой из них, при отсутствии зажима 6 счетных импульсов, появляются после прихода десяти тактовых импульсов. При этом фазовый сдвиг импульсов на выходах 7 по отношению к импульсам опорной последовательности, задающей нулевую фазу, остается постоянным. Таким образом в счетчике осуществляется режим хранения информапии. Для правильного счета числа импульсов необходимо, чтобы счетные импульсы приходили на входы декад в промежутке между тактовыми импульсами. Это достигается путем введения входного синхронизатора (на чертеже не показан), обеспечивающего жесткую привязку каждого счетного импульса к последовательности импульсов, пе совпадающих во времени пи с одним из тактовых. Импульс переноса на следующую декаду выделяется схемой объединения 2, поскольку после приходов десяти счетных импульсов, предыдущая декада срабатывает в момент времени, не совпадающий с импульсами такта. При этом счетные импульсы на вход первой декады должны поступать с частотой пе выше, чем на выходе опорной декады. Начальная установка (сброс) счетчика производится подачей импульса па щину 4 в момент времени соответствующий фазе нуль. Как видно из блок-схемы и описания работы счетчика, о состоянии декады можно судить по фазе импульсов на единственном для данной декады выходе. Соответственно в шестнадцатищтырьковом корпусе можно разместить, в принципе (если исходить из того, что ограничения определяются числом выводов), до десятка декад простейшего счетчика; три вывода питания, один - счетный вход, один - тактовые импульсы, один - сброс, остальные десять - выходы соответствующих декад. По тем же соображениям в одном корпусе может быть размещено до шести декад регистра или пяти декад счетчика с предустановкой. Счетчик с повышенным быстродействием (до 10-20 Мгц и выше) может быть построен по схеме, приведенной на фиг. 2. Отличие его от описанного ранее заключается во введении вспомогательной декады 8, работающей в том же коде, что и декады / счетчика, и поразрядных схем 9 сравнения кодов (дешифраторов), а также в том, что тактовые импульсы в последней блок-схеме поступают только на вспомогательную декаду. Кроме того, на установочный вход вспомогательной декады через шину 10 поступают в качестве синхронизирующих импульсы опорной последовательности. Режим хранения информации в последней схеме обеспечивается статической памятью триггерных декад. После прихода каждого тактового импульса происходит сравнение содерл имого вспомогательной декады с содержимым каждой декады счетчика. В случае равенства кодов на выходах 7 соответствующих разрядных схем сравнения появляются импульсы, несущие информацию о состоянии декад. Поскольку в последней схеме прямые связи декад 1 счетчика с источником тактовых импульсов отсутствуют, разрешающая способность по частоте этого варианта определяется быстродействием первой (младшей) декады, кроме того, отпадает необходимость во входном синхронизаторе. Подсчет числа выводов показывает, что в одном корпусе возможно разместить до девяти декад счетчика по описанной схеме. Не исключено также и комбинированное решение, в котором низкочастотная часть выполняется по схеме, приведенной на фиг. 1, а высокочастотная - по схеме, изобрал енной на фиг. 2. Между двумя модулями счетчика в этом случае необходимо поставить синхронизатор. Таким образом, введение фазоимпульспого редставления информации с использованием рогрессивных методов технологии изготовлеия модулей позволит существенно уменьить количество модулей в схемах цифровых риборов, что является одним из важнейших словий дальнейшего улучшения их техникокономических показателей: габаритов, веса, адежности. Предмет изобретения

целью повышения надежности, на счетный вход первого триггера каждой группы, объединяющей триггеры в соответствии с требуемым основанием системы счисления, подают

импульсы тактовой последовательности, а ИЁ дикацпю состояний каждой группы триггеров осуществляют сравнением по фазе выходных импульсов группы с опорными импульсами.

| название | год | авторы | номер документа |

|---|---|---|---|

| БИБЛИОТЕКА 1 | 1971 |

|

SU319907A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1972 |

|

SU325712A1 |

| СЧЕТЧИК ИМПУЛЬСОВ1•) | 1973 |

|

SU394942A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1970 |

|

SU275134A1 |

| СЧЕТЧИК С ПРЕДВАРИТЕЛЬНОЙ УСТАНОВКОЙ | 1971 |

|

SU322855A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1972 |

|

SU425363A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДЕСЯТИЧНЫЙ ФАЗОИМПУЛЬСНЫЙ | 1969 |

|

SU238226A1 |

| СЧЕТЧИК ИЛ'^ПУЛЬСОВ | 1973 |

|

SU365842A1 |

| ОДНОРАЗРЯДНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК | 1971 |

|

SU300958A1 |

| ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1973 |

|

SU383085A1 |

I .ОЛЛ,

e -HZJw 0 ттиг

Даты

1971-01-01—Публикация