Изобретение относится к области импульсной техники и может быть использовано при построении высокоточных усилителей постоянного тока с тиристорными выходными каскадами.

Известны устройства управления усилительным каскадом на тиристорах, -содержащие стабилизатор зарядного тока, интегрирующую цепь, спусковую схему, двухполупериодный коммутатор и формирователь импульсов.

Недостатки известных устройств состоят в низкой чувствительности и небольщом коэффициенте усиления.

С целью повышения чувствительности и коэффициента усиления в предлагаемо -: устройстве интегрирующая цепь содержит два последовательно включенных конденсатора и подключена к параллельно спусковой схеме, собранной на транзисторах противоположного типа проводимости, причем к одному полюсу интегрирующей цепи -подключен эмиттер -п-/7-транзистор и входное сопротивление спусковой схемы, к другому-эмиттер п-р-птранзистора спусковой схемы, средняя точка интегрирующей цепи соединена с эмиттерами транзисторов двухполупериодного коммутатора, а к точке соединения коллектора р-л- э-транзистора и базы л-р-п-транзистора спусковой схемы подключена база транзистора импульсного усилителя.

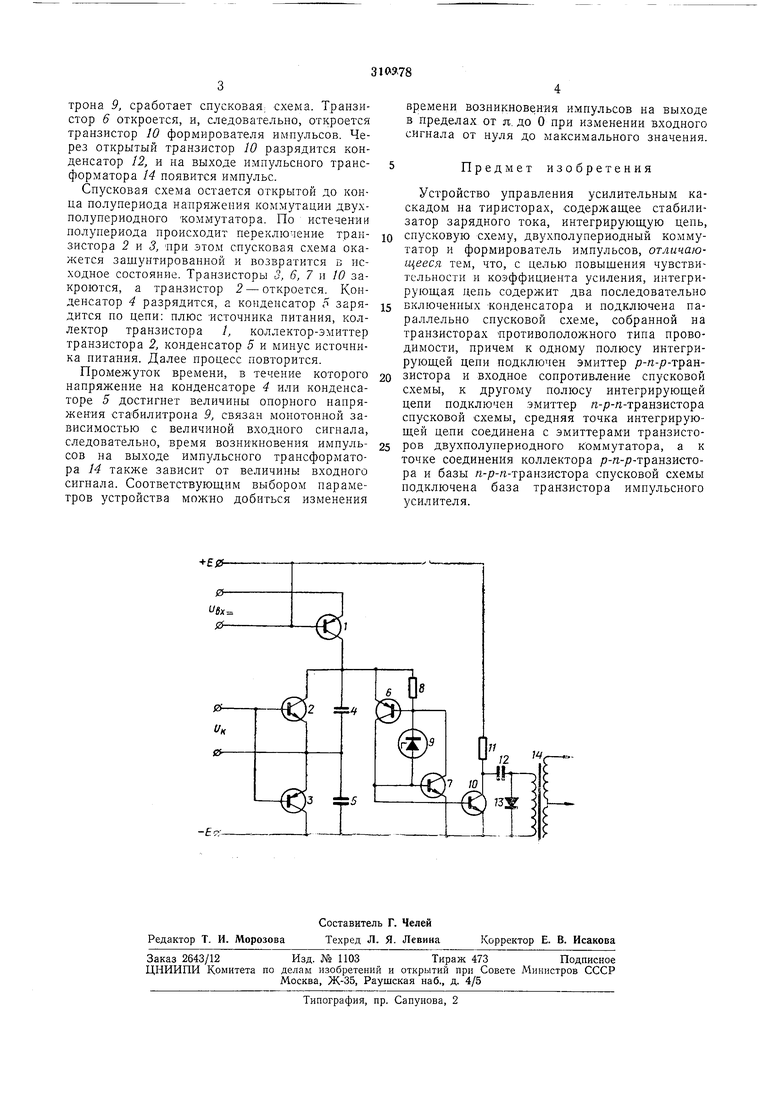

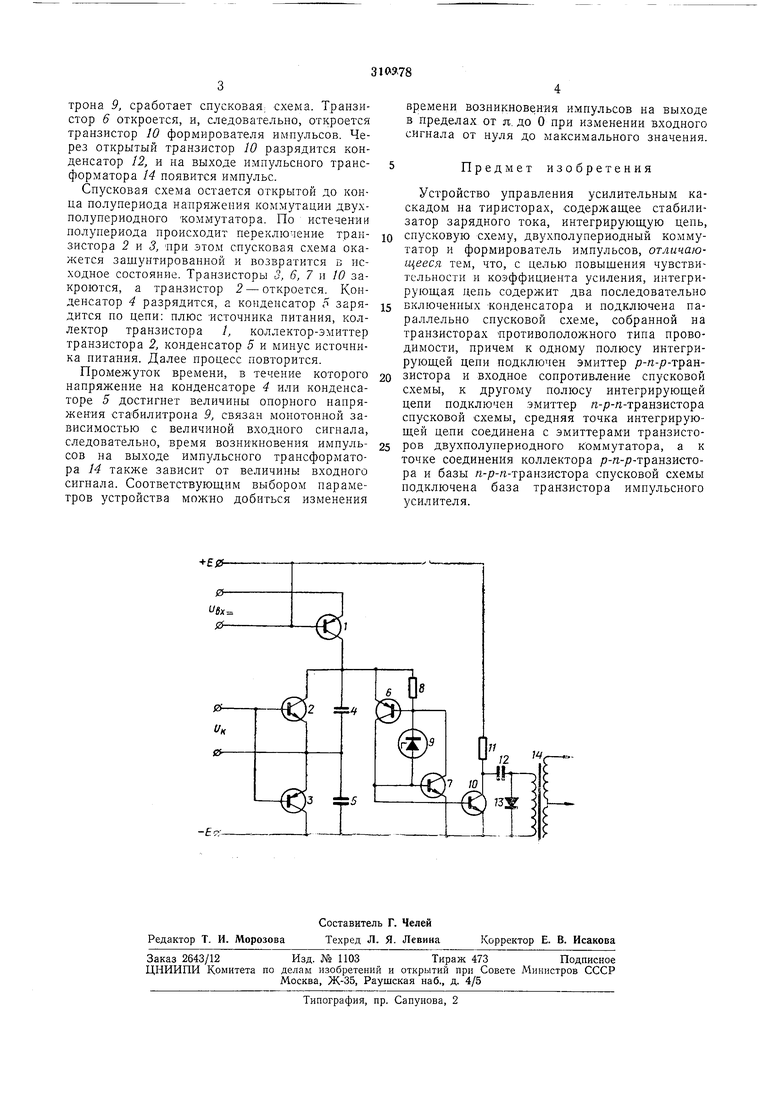

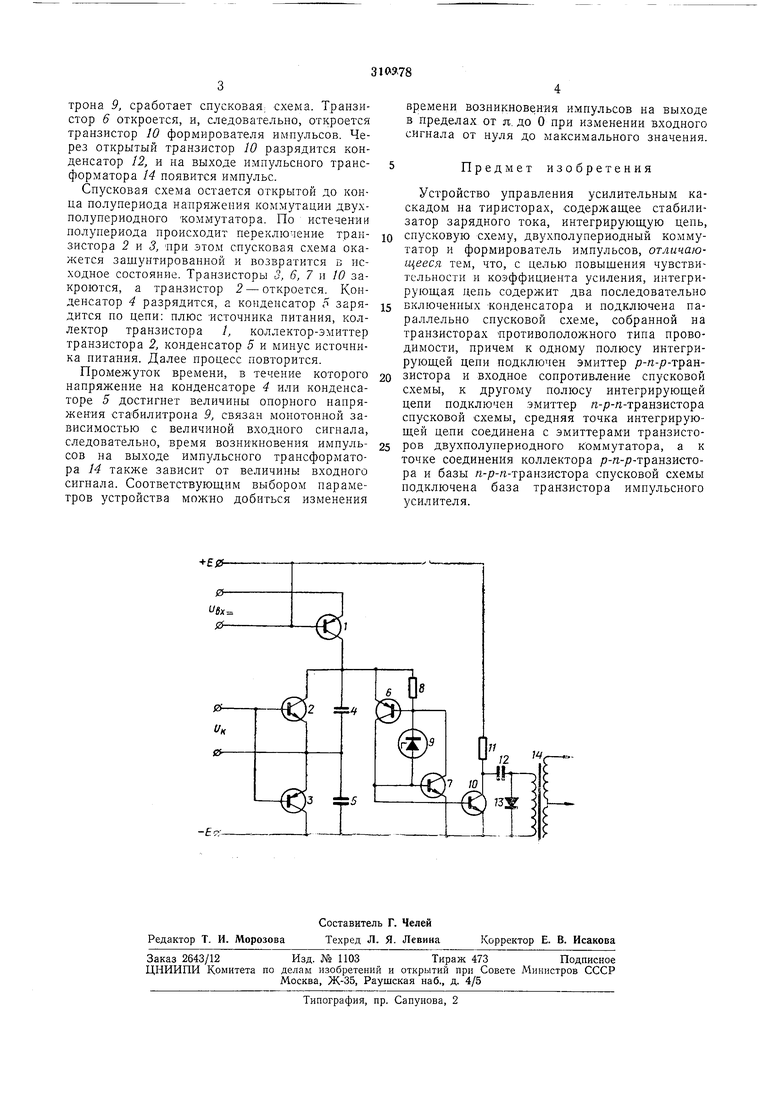

На чертеже дана принципиальная схема предлагаемого устройства формирования импульсов управления усилительным каскадом на тиристорах.

Устройство содержит стабилизатор зарядного тока на транзисторе /, двухполупериодный коммутатор на /г-р-л--транзисторе 2 и уУ-л-р-транзисторе 3, интегрирующую цепь, состоящую из двух последовательно включенных конденсаторов 4 и 5, спусковую схему, собранную на транзисторах противоположного типа проводимости (р-л-р-транзисторе 6 и л-р-л-транзисторе 7), в которую также входят резистор 8 и стабилитрон 9, формирователь импульсов, выполненный на транзисторе 10, резисторе //, конденсаторе 12, диоде 13 и импульсном трансформаторе 14.

Предлагаемое устройство работает следующим образом.

Нри поступлении в цепь база-эмиттер транзистора 1 входного сигнала в цепи коллектора этого транзистора появится ток. Если в первый момент транзистор 2 двухполупериодного коммутатора закрыт, а транзистор 3 - открыт, то конденсатор 4 интегрирующей цепи заряжается по цепи: плюс источника питания, коллектор транзистора 1, конденсатор 4, коллектор-эмиттер транзистора 3, и минус источника питания. Когда напряжение на конденсаторе 4 достигнет величины пробоя стабилитрона 9, сработает спусковая: схема. Транзистор 6 откроется, и, следовательно, откроется транзистор 10 формирователя импульсов. Через открытый транзистор 10 разрядится конденсатор 12, и на выходе импульсного трансформатора 14 появится импульс.

Спусковая схема остается открытой до конца полупериода напряжения коммутации двухполупериодного коммутатора. По истечении полунериода происходит переключение транзистора 2 и 3, при этом спусковая схема окажется зашунтированной и возвратится в исходное состояние. Транзисторы 3, 6, 7 и 10 закроются, а транзистор 2 - откроется. Конденсатор 4 разрядится, а конденсатор 5 зарядится но цепи: плюс источника питания, коллектор транзистора /, коллектор-эмиттер транзистора 2, конденсатор 5 и минус источника питания. Далее процесс повторится.

Промежуток времени, в течение которого напряжение на конденсаторе 4 или конденсаторе 5 достигнет величины опорного напряжения стабилитрона Я связан монотонной зависимостью с величиной входного сигнала, следовательно, время возникновения импульсов на выходе импульсного трансформатора 14 также зависит от величины входного сигнала. Соответствующим выбором параметров устройства можно добиться изменения

времени возникнове:ния импульсов на выходе в пределах от я. до О при изменении входного сигнала от нуля до максимального значения.

Предмет изобретения

Устройство управления усилительным каскадом на тиристорах, содержащее стабилизатор зарядного тока, интегрирующую цепь, спусковую схему, двухполупериодный коммутатор и формирователь импульсов, отличающееся тем, что, с целью повышения чувствительности и коэффициента усиления, интегрирующая цепь содержит два последовательно включенных конденсатора и подключена параллельно спусковой схеме, собранной на транзисторах противоположного типа проводимости, причем к одному полюсу интегрирующей цепи подключен эмиттер /з-«-р-транзистора и входное сопротивление спусковой схемы, к другому полюсу интегрирующей цепи подключен эмиттер п-р-/г-транзистора спусковой схемы, средняя точка интегрирующей цепи соединена с эмиттерамИ транзисторов двухполупериодного коммутатора, а к точке соединения коллектора /7-п-р-транзнстора и базы я-р-п-транзистора спусковой схемы подключена база транзистора импульсного усилителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ФОРМИРОВАНИЯ ИМПУЛЬСОВ с ПЕРЕМЕННЫМ ПОРОГОМ ЧУВСТВИТЕЛЬНОСТИ | 1971 |

|

SU305579A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1971 |

|

SU321932A1 |

| Формирователь импульсов | 1972 |

|

SU473289A1 |

| Интегратор | 1979 |

|

SU824226A1 |

| Формирователь импульсов | 1974 |

|

SU657601A1 |

| Стабилизированный выпрямитель | 1978 |

|

SU748381A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛА ВКЛЮЧЕНИЯ ПОМЕХ | 1993 |

|

RU2122281C1 |

| СПОСОБ УПРАВЛЕНИЯ ТРАНЗИСТОРНЫМ КЛЮЧОМ НА ТИРИСТОРЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2343622C1 |

| Импульсный стабилизатор напряжения | 1985 |

|

SU1325440A1 |

| Устройство для регулирования температуры | 1991 |

|

SU1783500A1 |

Даты

1971-01-01—Публикация