Изобретение относится к области вычислительной техники.

Известны устройства для моделирования сетевого графика, содержащие в соответствии с топологией сетевого графика модели ветвей с триггерами и логическими схемами «И и «ИЛИ, а также масштабные источники напряжения, проводимости, ключи, резисторы и диоды.

В известных устройствах класс решаемых задач ограничен.

Цель изобретения - расширить класс решаемых задач.

В предлагае.мом устройстве это достигается тем, что оно содержит бло-ки стоимостно-ресурсных ограничений, в которых один из зажимов измерительного резистора подключен к Ш1ине нулевого 1потеНЦиала, а второй зажим соединен с выходом блока и одним из полюсов ма-сштабн-ого источника напряжения, второй полюс которого через группу последавателыно соединенных провадимостей и диодов подключен к выходам ключей моделей ветвей, в каждой из которых единичный выход одного из триггеров соединен с единичным входом второго триггера, подключенного своим единичным выходом через диод к выходу модели ветви, причем нулевой выход второго триггера соединен с первыми входами двух- и трехвходовой схем «И, подключенных своими вторыми входами к упра.вляюш,им входам модели ветвИ, третий вход трехвходовой схемы «И подключен к третьему входу модели ветви, выходы обеих схем «И присоединены ко входам схемы

«ИЛИ, третий вход которой соединен с индикационным выходом модели ветви, а ее выход подключен к управляюшему входу ключа, присоединенного своим выходом ко входу схемы индикации.

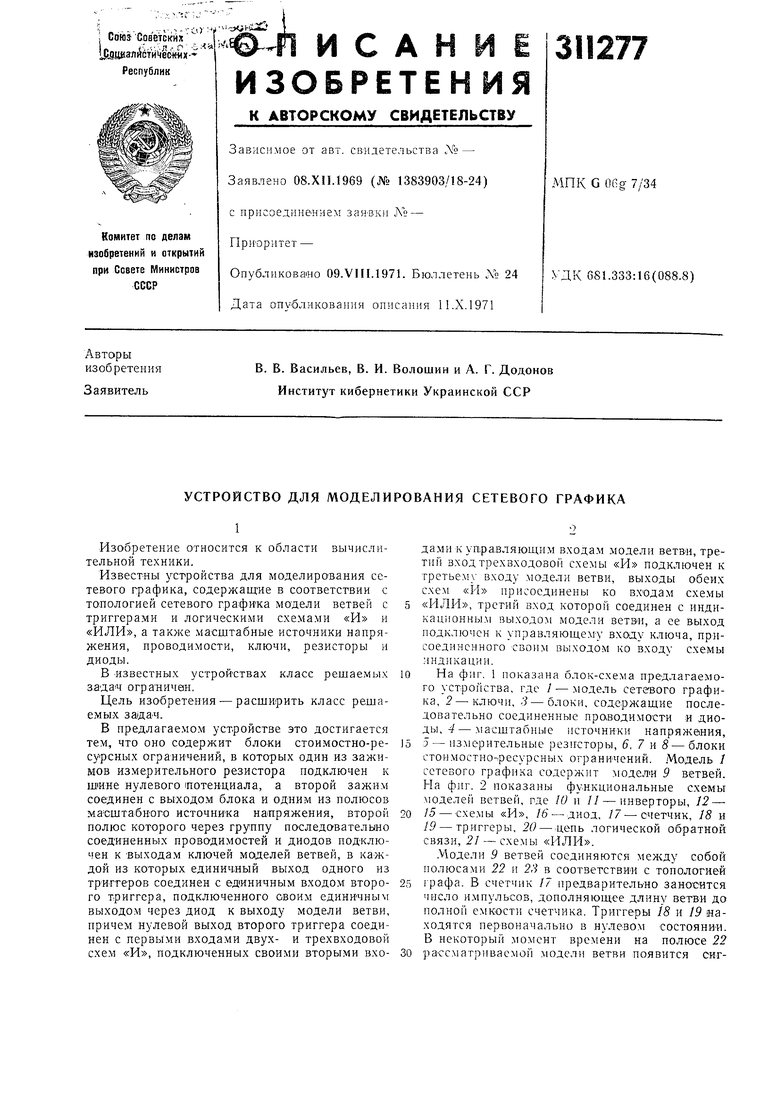

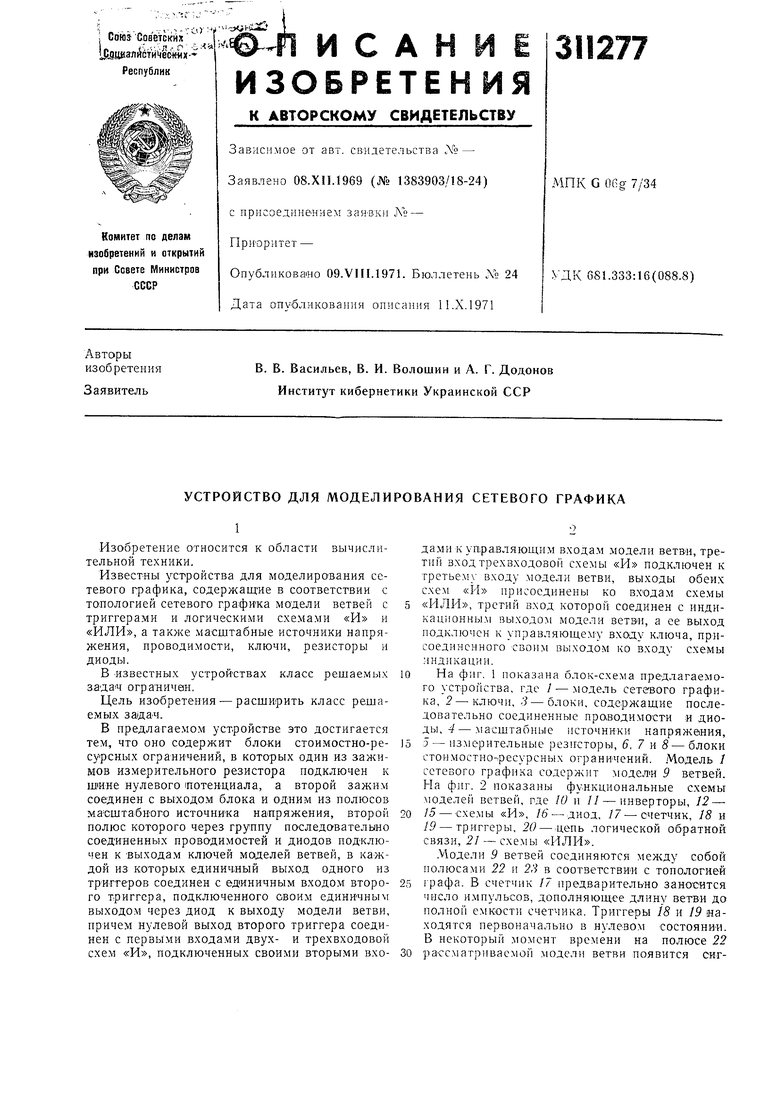

На фиг. 1 показана блок-схема предлагаемого устройства, где / - модель сетевого графика, 2-ключи, 3-блоки, содержащие последовательно соединенные про,водим0сти и диоды, масштабные источники напряжения,

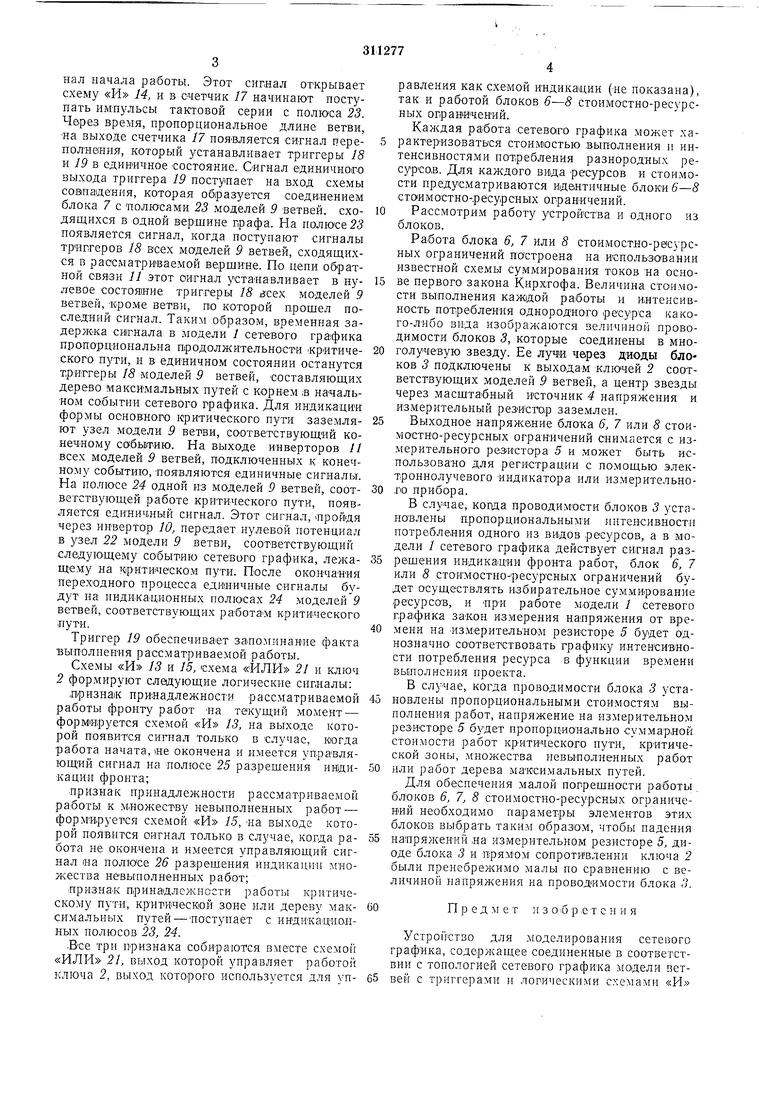

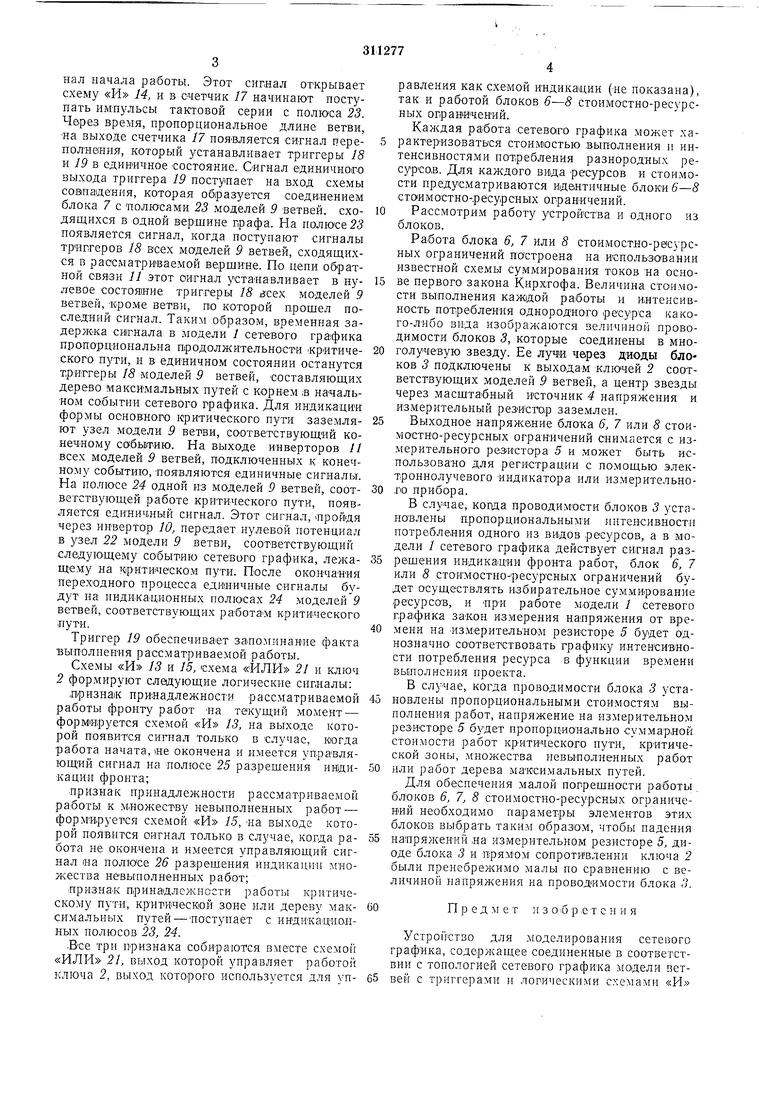

5-измерительные резисторы, 6. 7 и 8 - блоки стоимостно-ресурсных ограничений. Модель / сетевого графика содержит моделИ 9 ветвей. На фиг. 2 показаны функциональные схемы моделей ветвей, рде 10 и // - инверторы, 12 -

/5-схемы «И, /6 - диод, 17-счетчик, 18 и 19 - триггеры, 20 - депь логической обратной связи, 21 - схемы «ИЛИ.

Модели 9 ветвей соединяются между собой нолюсами 22 и 23 в соответствии с топологией

графа. В счетчик 17 предварительно заносится число импульсов, дополняюш,ее длину ветви до полной емкости счетчика. Триггеры 18 и 19 находятся первоначально в нулевом состоянии. В некоторый момент времени на полюсе 22

нал начала работы. Этот сигнал открывает схему «И 14, и в счетчик 17 начинают поступать импульсы тактовой серии с полюса 23. Через время, пролорционалБНое длине ветви, на выходе счетчика 17 появляется сигнал переполнения, который устанавливает триггеры 18 и 19 в единичное состояние. Сигнал единичного выхода триггера 19 поступает на вход схемы сонпайения, которая образуется соединением блока 7 с полюсами 23 моделей 9 ветвей, сходящихся в одной вершине графа. На полюсе25 появляется сигнал, когда поступают сигналы триггеров 18 всех моделей 9 ветвей, сходящихся в рассматриваемой вершкне. По цепи обратной свя:3и // этот сигнал устанавливает в нулевое состоящие триггеры 18 всех моделей 9 ветвей, Кроме ветви, по которой прощел последний сигнал. Таким образом, временная задерлжа сигнала в модели / сетевого графика пропорциональна продолжительности Критического пути, и в единичном состоянии останутся триггеры 18 моделей 9 ветвей, составляющих дерево максимальных путей с корнем ;в начальном сооытии сетевого графика. Для индикации формы основного критического пути заземляют узел модели 9 ветви, соответствующий конечному событию. На выходе инверторов 11 всех моделей 9 ветвей, подключенных к конечному событию, ПОЯВЛЯЮТСЯ единичные сигналы. На полюсе 24 одной нз моделей 9 ветвей, соответствующей работе критического пути, появляется единичный сигнал. Этот сигнал, пройдя через инвертор 10, передает нулевой потенциа;( в узел 22 модели 9 ветви, соответствующий следующему событию сетевого графика, лежащему на критическом пути. После окончаНия переходного нроцесса едиятичные сигналы будут на индика ционных полюсах 24 моделей 9 ветвей, соответствующих работаМ критического пути.

Триггер 19 обеспечивает запоминание факта выполнения рассматриваемой работы.

Схемы «И 13 и 15, схема «ИЛИ 21 и ключ 2 формируют следующие логические сигналы:

признак принадлежности рассматриваемой работы фронту работ на текущий момент - формируется схемой «И 13, на выходе которой появится сигнал только в случае, когда работа начата, не окончена и имеется управляющий сигнал на нолюсе 25 разрешения индикации фронта;

признак принадлежности рассматриваемой работы к мнолсеству невыполненных работ - формируется схемой «И 15, На выходе которой появится сигнал только в случае, когда работа не окончена и имеется управляющий сигнал на полюсе 26 разрешения индикации множества невыполненных работ;

призна-к принадлежности работы критическому пути, кригической зоне или дереву максимальных путей - тюступает с инднка ЦИонных полюсов 23, 24.

равления как схемой индикации (не показана), так и работой блоков 6-8 стоимоСтно-ресурсных ограничений.

Каждая работа сетевого графика может характерИзоватьСя стоимостью выполнения и интенсивностями потребления разнородных ресурсов. Для каждого вида ресурсов и стоимости предусматриваются идентичные блоки стаимостно-ресурсных ограничений.

Рассмотрим работу устройства и одного из блоков.

Работа блока 6, 7 или 8 стоимостно-ресурсных ограничений построена на использовании известной схемы суммирования токов на основе первого закона Кирхгофа. Величина стоимости выполнения кажздой работы и интенсивность потребления однородного ресурса какого-Либо вида изображаются величиной проводимости блоков 5, которые соединены в многолучевую звезду. Ее луч1И через диоды блоков 3 подключены к выходам ключей 2 соответствующих моделей 9 ветвей, а центр звезды через масштабный источник 4 напряжения и измерительный резистор заземлен.

Выходное напряжение блока 6, 7 или 8 стоимостно-ресурсных ограничений снимается с измерительного реэистора 5 и может быть использовано для регистрации с помощью электроннолучевого Индикатора или измерительногю прибора.

В случае, когда проводимости блоков 3 установлены пропордиональными интенсивности потребления одного из видов ресурсов, а в модели 1 сетевого графика действует сигнал разрешения индика-ции фронта работ, блок 6, 7 или 8 стоимостно-ресурсных ограничений будет осуществлять избирательное суммирование ресурсов, и прИ работе модели / сетевого графика закон измерения наяряжения от времени на Измерительном резисторе 5 будет однозначно соответствовать графику интенсиВНости потребления ресурса в функции времени выполнения проекта. В случае, когда проводимости блока 3 установлены пропордиональными стоимостям выполнения работ, напряжение на измерительном резисторе 5 будет пропорционально суммарной стоимости работ критического пути, критической зоны, множества невыполненных работ

или работ дерева магссимальных путей.

Для обеспечения малой погрешности работы . блоков 6, 7, 8 стоимостно-ресурсных ограничений необходимо параметры элементов этих блоков выбрать таким образом, чтобы падения

иапрялсений на измерительном резисторе 5, диоде блока 3 и прямом сопротивлении ключа 2 были пренебрежимо малы по сравнению с величиной напрялсения на проводимости блока /Л

Yip ел 1 е т и з о 6 р е т с н и я

Устройство для моделирования сетевого графика, содерл ащее соединенные в соответствии с топологией сетевого графика модели вет65 вей с триггерами и логическими схемами «И

и «ИЛИ, а также масштабные источники напряжения, проводимости, ключи, резисторы и диоды, отличающееся тем, что, с целью расширения класса решаемых задач, оно содержит блоки стовмостно-ресурсных ограничений, в которых одии из зажимов измерительного резистора подключен к шине нулевого потенциала, а второй залсим соединен с выходом блока и одним из полюсов масштабного источника нацряжения, второй полюс .которого через группу последовательно соединенных проводимостей и диодов подключен к выходам ключей моделей ветвей, в каждой из которых единичный выход одного из триггеров соединен с

единичным входом второго триггера, подключенного своим единичным выходом через диод к выходу модели ветви, причем нулевой выход второго триггера соединен с первыми входами

двух- и трехвходовой схем «И, подключенных своими вторыми входами к управляющим входам модели ветви, третий вход трехвходовой схемы «И подключен к третьему входу модели ветви, выходы обеих схем «И присоединены ко

входам схемы «ИЛИ, третий вход которой соединен с индикационным выходом модели ветви, а ее выход подключен к управляющему входу ключа, присоединенного своим выходом ко входу схемы индикации.

. 26

г

Г:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления текущих ресурсов | 1978 |

|

SU746589A1 |

| Вычислительное устройство для решения задач сетевого планирования | 1978 |

|

SU750503A1 |

| Устройство для моделирования сетевого графика | 1975 |

|

SU570060A1 |

| Устройство для моделированияСЕТЕВыХ гРАфиКОВ | 1979 |

|

SU809221A1 |

| Устройство для расчета сетевыхгРАфиКОВ | 1979 |

|

SU851417A1 |

| Устройство для моделирования экстремальных путей на графе | 1980 |

|

SU926670A1 |

| Устройство для моделирования сетевых графиков | 1985 |

|

SU1300481A2 |

| ВЫЧИСЛИТЕЛЬНАЯ МАШИНА ДЛЯ РАСЧЕТА СЕТЕВЫХ | 1973 |

|

SU367431A1 |

| Устройство для определения оптимального дерева связности графа | 1985 |

|

SU1411782A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПУТЕЙ НА ГРАФЕ | 1972 |

|

SU337792A1 |

22

L.

23

.-J

Даты

1971-01-01—Публикация