тий триггер 1, четвертый триггер 2, счетчик 3, дешифратор кодов 4, первый дополнительньй элемент И 5, второй дополнительный элемент И 6 и третий дополнительный элемент И 7 вход 8 запуска устройства, выходы 9 10 и 11 и входы 12, 13, 14 и 15 устрой- .ства. Использование новых элементов в устройстве обеспечивает повьшение точности за счет обмена информацией между объектом и моделью сетевого графика в реальном масштабе времени для оперативного контроля и передачи управления по сетевому проекту, что позволяет существенно уменьшить время выполнения технологического про- цессао Так, в частности, если сете1

Изобретение относится к вычислительной технике, -а именно к устройству для сопряжения специализированных вычислительных машин с реальньм объектом, и может быть использовано при построении специализированных машин для моделирования сетевых графиков и сопряжения их с объектом в реальном масштабе времени.

Целью изобретения является повышение точности.

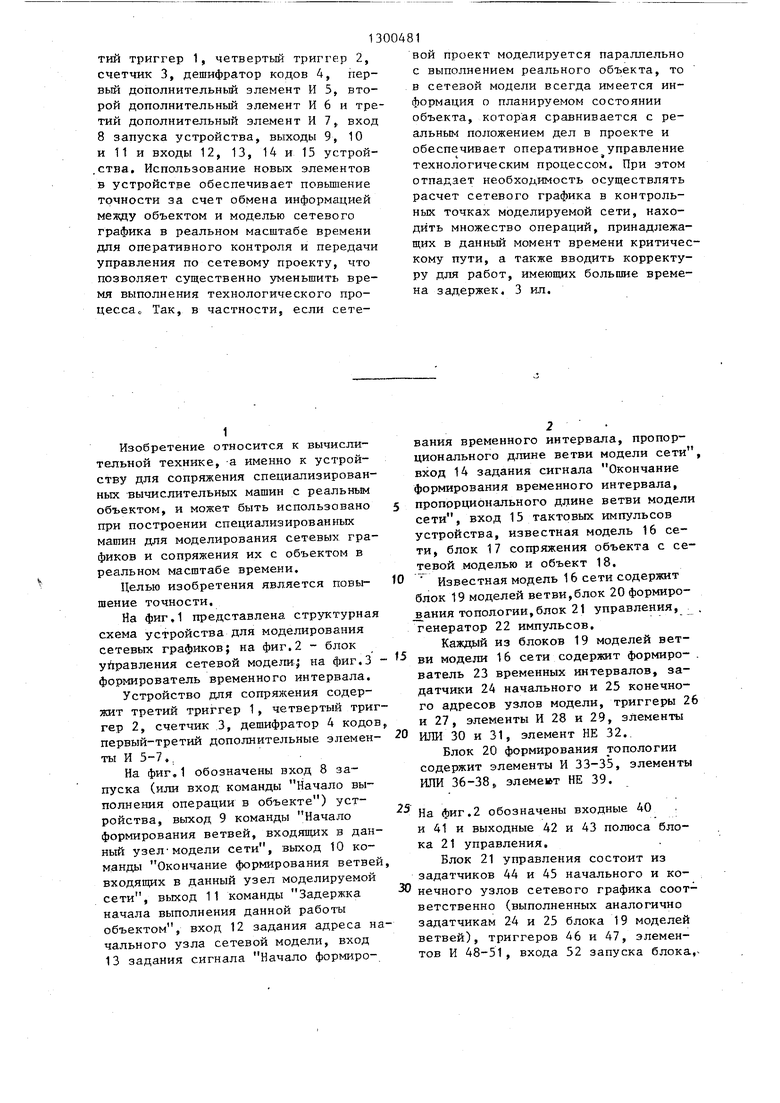

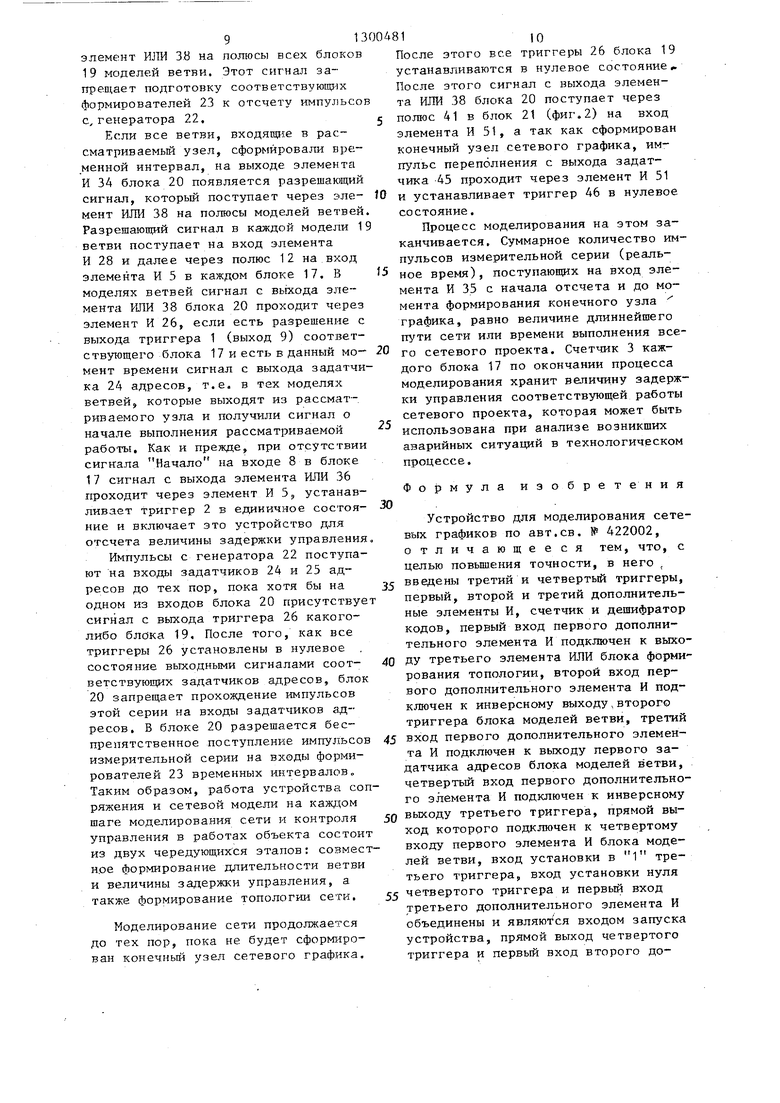

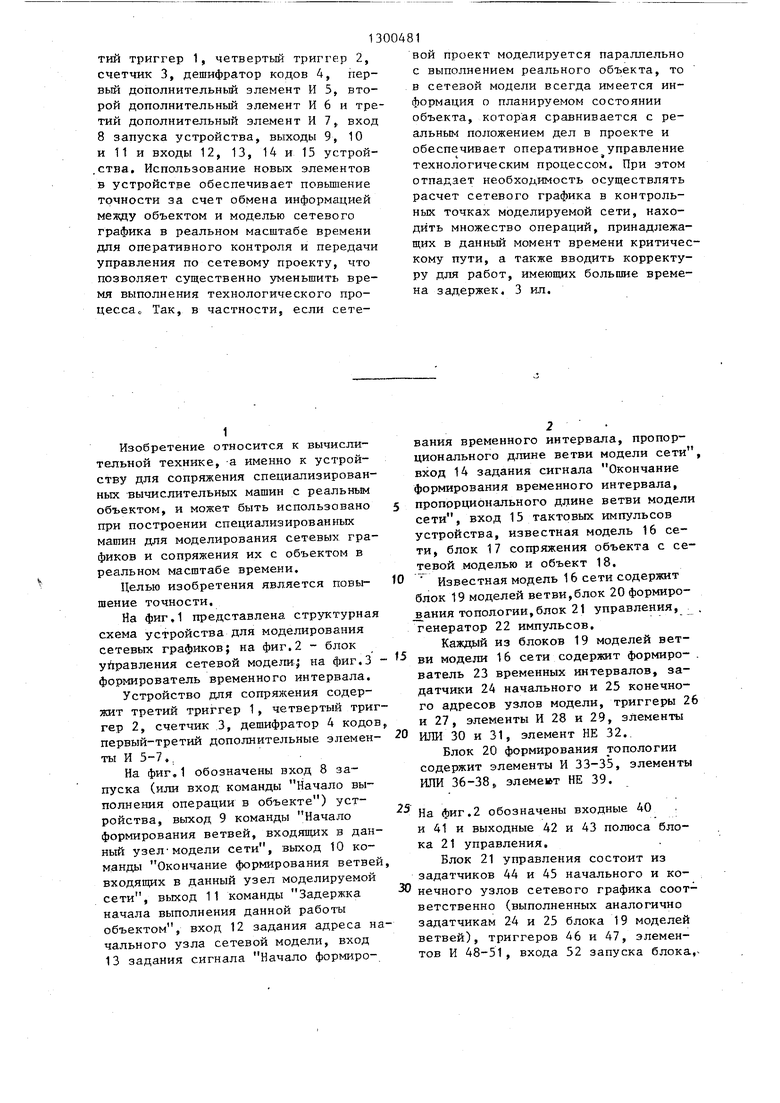

На фиг.1 представлена структурная схема устройства для моделирования сетевых графиков; на фиг.2 - блок управления сетевой модели на фиг.З формирователь временного интервала.

Устройство для сопряжения содержит третий триггер 1, четвертый триггер 2, счетчик 3, дешифратор 4 кодов первый-третий дополнительные элементы И 5-7,

На фиг,1 обозначены вход 8 запуска (или вход команды Начало выполнения операции в объекте) устройства, выход 9 команды Начало формирования ветвей, входяпцих в данный узел-модели сети, выход 10 команды Окончание формирования ветвей входящих в данный узел моделируемой сети, выход 11 команды Задержка начала выполнения данной работы объектом, вход 12 задания адреса начального узла сетевой модели, вход 13 задания сигнала Начало формировой проект моделируется параллельно с выполнением реального объекта, то в сетевой модели всегда имеется информация о планируемом состоянии объекта, которая сравнивается с реальным положением дел в проекте и обеспе чивает оперативное управление технологическим процессом. При этом отпадает необходимость осуществлять расчет сетб вого графика в контрольных точках моделируемой сети, находить множество операций, принадлежащих в данньш момент времени критическому пути, а также вводить корректуру для работ, имеющих большие времена задержек. 3 ил.

вания временного интервала, пропорционального длине ветви модели сети, вход 14 задания сигнала Окончание формирования временного интервала,

пропорцион.:шьного длине ветви модели сети, вход 15 тактовых импульсов устройства, известная модель 16 сети, блок 17 сопряжения объекта с сетевой моделью и объект 18.

Известная модель 16 сети содержит блок 19 моделей ветви,блок 20 формиро- Jsaния топологии,блок 21 управления, , генератор 22 импульсов.

Каждый из блоков 19 моделей ветви модели 16 сети содержит формиро- . ватель 23 временных интервалов, за- датчики 24 начального и 25 конечного адресов узлов модели, триггеры 26 и 27, элементы И 28 и 29, элементы

ИЛИ 30 и 31, элемент НЕ 32..

Блок 20 формирования топологии содержит элементы И 33-35, элементы ИЛИ 36-38,, элемент НЕ 39.

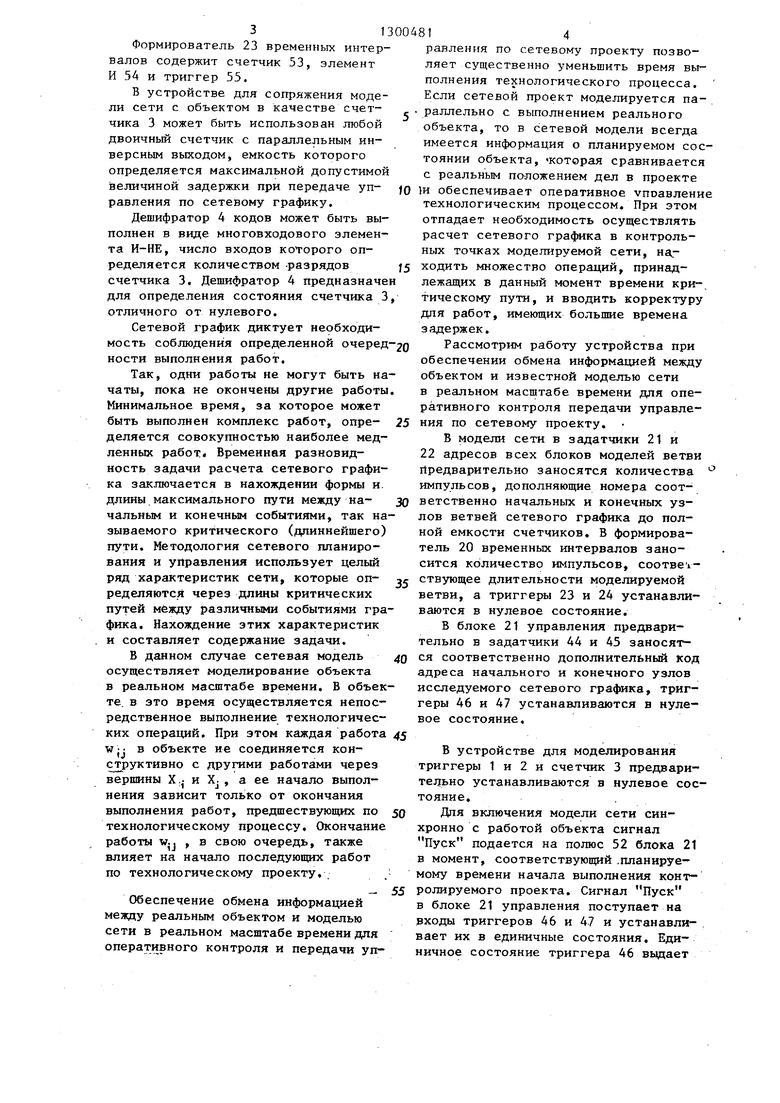

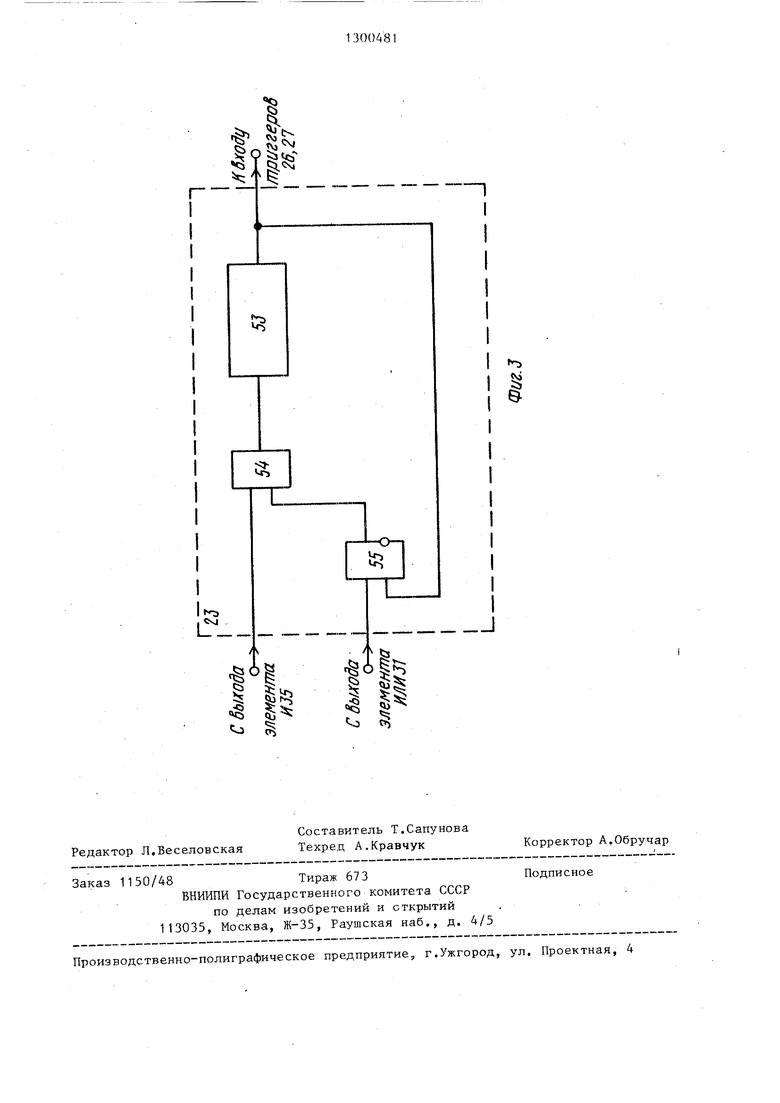

На фиг.2 обозначены входные 40

и 41 и выходные 42 и 43 полюса блока 21 управления.

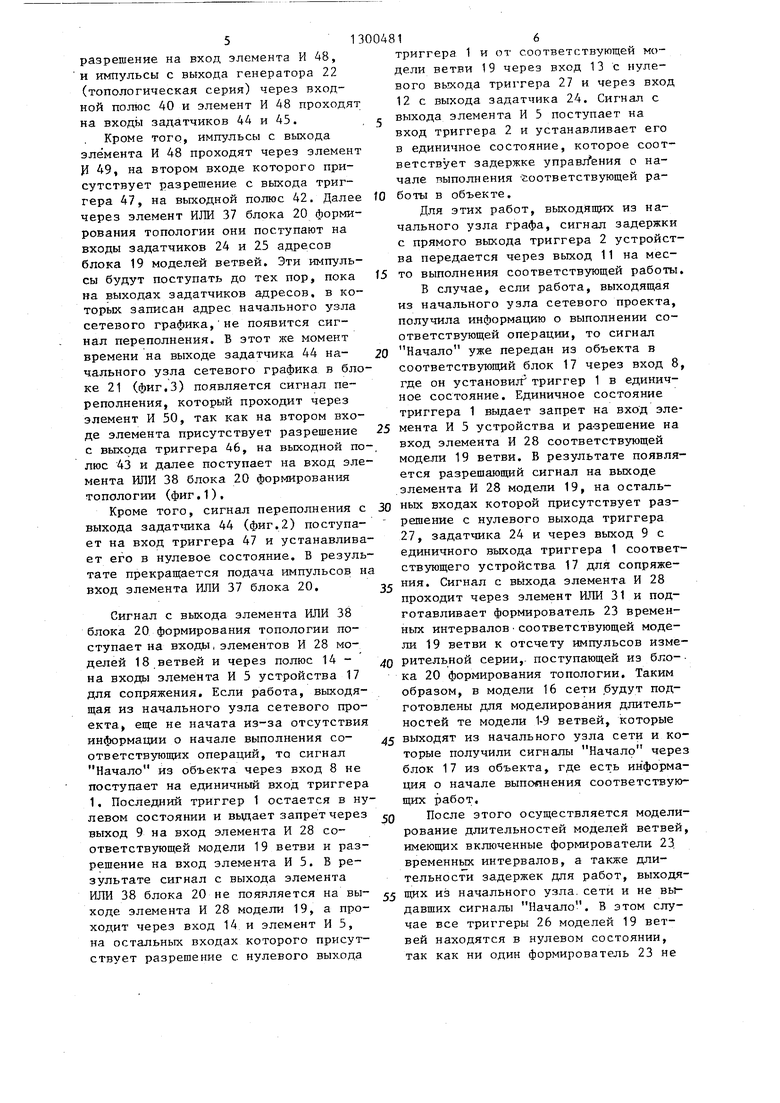

Блок 21 управления состоит из задатчиков 44 и 45 начального и конечного узлов сетевого графика соответственно (выполненных аналогично задатчикам 24 и 25 блока 19 моделей ветвей), триггеров 46 и 47, элементов И 48-51, входа 52 запуска блока,Формирователь 23 временных интервалов содержит счетчик 53, элемент И 54 и триггер 55.

В устройстве для сопряжения модели сети с объектом в качестве счетчика 3 может быть использован любой двоичный счетчик с параллельным ин- верснЫм выходом, емкость которого определяется максимальной допустимой величиной задержки при передаче уп- равнения по сетевому графику.

Дешифратор 4 кодов может быть выполнен в виде многовходового элемента И-НЕ, число входов которого определяется количеством -разрядов счетчика 3, Дешифратор 4 предназначе для определения состояния счетчика 3 отличного от нулевого.

Сетевой график диктует нербходи- мость соблюдения определенной очеред кости выполнения работ.

Так, одни работы не могут быть начаты, пока не окончены другие работы Минимальное время, за которое может быть выполнен комплекс работ, опре- деляется совокупностью наиболее медленных работ. Временная разновидность задачи расчета сетевого графика зак.шочавтся в нахождении формы и. длины максимального пути между на- чальным и конечным событиями, так называемого критического (дпиннейшего) пути. Методология сетевого планирования и управления использует целый ряд характеристик сети, которые оп- ределяются через длины критических путей мбжду различными событиями графика. Нахождение этих характеристик и составляет содержание задачи.

В данном случае сетевая модель осуществляет моделирование объекта в реальном масштабе времени. В объекте, в это время осуществляется непосредственное выполнение технологических операций. При этом каждая работа wjj в объекте не соединяется кон- с груктивно с другими работами через вершины Х,- и Xj , а ее начало выполнения зависит только от окончания выполнения работ, предшествующих по технологическому процессу. Окончание работы W.J , в свою очередь, также влияет на начало последуюпрпс работ по технологическому проекту.

Обеспечение обмена информацией между реальным объектом и моделью сети в реальном масштабе времени дпя оперативного контроля и передачи управления по сетевому проекту позволяет существенно 5 меньшить время выполнения технологического процесса. Если сетевой проект моделируется па- раллельно с выполнением реального объекта, то в сетевой модели всегда имеется информация о планируемом состоянии объекта, -которая сравнивается с реальным положением дел в проекте Ш обеспечивает оперативное упоавлени технологическим процессом. При этом отпадает необходимость осуществлять расчет сетевого графика в контрольных точках моделируемой сети, наг ходить множество операций, принадлежащих в данный момент времени критическому пути, и вводить корректуру для работ, имеющих большие времена задержек.

Рассмотрим работу устройства при обеспечении обмена информацией между объектом и известной моделью сети в реальном масштабе времени для оперативного контроля передачи управления по сетевому проекту.

В модели сети в задатчики 2t и 22 адресов всех блоков моделей ветви йредварительно заносятся количества импульсов, дополняющие номера соответственно начальных и конечных узлов ветвей сетевого графика до полной емкости счетчиков. В формирователь 20 временных интервалов заносится количество импульсов, соответствующее длительности моделируемой ветви, а триггеры 23 и 24 устанавливаются в нулевое состояние.

В блоке 21 управления предварительно в задатчики 44 и 45 заносятся соответственно дополнительный код адреса начального и конечного узлов исследуемого сетевого графика триггеры 46 и 47 устанавливаются в нулевое состояние.

В устройстве для моделирования триггеры 1 и 2 и счетчик 3 предварительно устанавливаются в нулевое состояние..

Дпя включения модели сети синхронно с работой объекта сигнал Пуск подается на полюс 52 блока 21 в момент, соответствующий .планируемому времени начала выполнения контролируемого проекта. Сигнал Пуск в блоке 21 управления поступает на входы триггеров 46 и 47 и устанавливает их в единичные состояния. Единичное состояние триггера 46 выдает

разрешение на вход элемента И 48, и импульсы с выхода генератора 22 (топологическая серия) через входной полюс 40 и элемент И 48 проходят на входы задатчиков 44 и 45.

Кроме того, импульсы с выхода элемента И 48 проходят через элемент И 49, на втором входе которого присутствует разрешение с выхода триггера 47, на выходной полюс 42. Далее через элемент ИЛИ 37 блока 20 формирования топологии они поступают на входы задатчиков 24 и 25 адресов блока 19 моделей ветвей. Эти импульсы будут поступать до тех пор, пока на выходах задатчиков адресов, в которых записан адрес начального узла сетевого графика, не появится сигнал переполнения. В этот же момент времени на выходе задатчика 44 начального узла сетевого графика в блоке 21 (фиг.З) появляется сигнал переполнения, который проходит через элемент И 50, так как на втором входе элемента присутствует разрешение

триггера 1 и от соответствующей модели ветви 19 через вход 13с нулевого выхода триггера 27 и через вход 12 с выхода задатчика 24. Сигнал с с выхода элемента И 5 поступает на вход триггера 2 и устанавливает его в единичное состояние, которое соответствует задержке управления о начале выполнения -йоответствующей ра10 боты в объекте.

Для этих работ, выходящих из начального узла графа, сигнал задержки с прямого выхода триггера 2 устройства передаетс51 через выход 11 на месf5 то выполнения соответствующей работы.

В случае, если работа, выходящая из начального узла сетевого проекта, получила информацию о выполнении соответствующей операции, то сигнал

20 Начало уже передан из объекта в

соответствзгюнщй блок 17 через вход 8, где он установив триггер 1 в единичное состояние. Единичное состояние триггера 1 выдает запрет на вход эле25 мента И 5 устройства и ра-зрешение на

с выхода триггера 46, на выходной по-, вход элемента И 28 соответствующей люс 43 и далее поступает на вход эле- модели 19 ветви. В результате появля- мента ИЛИ 38 блока 20 формирования ется разрещающий сигнал на выходе топологии (фиг,1),элемента И 28 модели 19, на остальКроме того, сигнал переполнения с 30 ньк входах которой присутствует раз- выхода задатчика 44 (фиг.2) поступает на вход триггера 47 и устанавливает его в нулевое состояние. В результате прекращается подача :1мпульсов на

решение с нулевого выхода триггера 27, задатчика 24 и через выход 9 с единичного выхода триггера 1 соответствующего устройства 17 для сопряжения. Сигнал с выхода элемента И 28 проходит через элемент ИЛИ 31 и подготавливает формирователь 23 временных интерваловсоответствующей модели 19 ветви к отсчету импульсов измерительной серии,- поступающей из бло- ка 20 формирования топологии. Таким образом, в модели 16 сети будут подготовлены для моделирования длительностей те модели 1-9 ветвей, которые 45 выходят из начального узла сети и которые получили сигналы Начало через блок 17 из объекта, где есть ин форма- ция о начале выполнения соответствующих работ.

вход элемента ИЛИ 37 блока 20,

Сигнал с выхода элемента ИЛИ 38 блока 20 формирования топологии поступает на входы,элементов И 28 моделей 18 ветвей и через полюс 14 - на входы элемента И 5 устройства 17 для сопряжения. Если работа, выходящая из начального узла сетевого проекта, еще не начата из-за отсутствия информации о начале выполнения соответствующих операций, то сигнал Начало из объекта через вход 8 не поступает на единичный вход триггера 1, Последний триггер 1 остается в нулевом состоянии и вьщает запрет через выход 9 на вход элемента И 28 соответствующей модели 19 ветви и раз- рещение на вход элемента И 5. В результате сигнал с выхода элемента ИЛИ 38 блока 20 не появляется на выходе элемента И 28 модели 19, а проходит через вход 14 и элемент И 5, на остальных входах которого присутствует разрешение с нулевого выхода

триггера 1 и от соответствующей модели ветви 19 через вход 13с нулевого выхода триггера 27 и через вход 12 с выхода задатчика 24. Сигнал с выхода элемента И 5 поступает на вход триггера 2 и устанавливает его в единичное состояние, которое соответствует задержке управления о начале выполнения -йоответствующей работы в объекте.

Для этих работ, выходящих из начального узла графа, сигнал задержки с прямого выхода триггера 2 устройства передаетс51 через выход 11 на место выполнения соответствующей работы.

В случае, если работа, выходящая из начального узла сетевого проекта, получила информацию о выполнении соответствующей операции, то сигнал

Начало уже передан из объекта в

соответствзгюнщй блок 17 через вход 8, где он установив триггер 1 в единичное состояние. Единичное состояние триггера 1 выдает запрет на вход элемента И 5 устройства и ра-зрешение на

30 ньк входах которой присутствует раз-

35

40

решение с нулевого выхода триггера 27, задатчика 24 и через выход 9 с единичного выхода триггера 1 соответствующего устройства 17 для сопряжения. Сигнал с выхода элемента И 28 проходит через элемент ИЛИ 31 и подготавливает формирователь 23 временных интерваловсоответствующей модели 19 ветви к отсчету импульсов измерительной серии,- поступающей из бло- ка 20 формирования топологии. Таким образом, в модели 16 сети будут подготовлены для моделирования длительностей те модели 1-9 ветвей, которые 45 выходят из начального узла сети и которые получили сигналы Начало через блок 17 из объекта, где есть ин форма- ция о начале выполнения соответствующих работ.

После этого осуществляется моделирование длительностей моделей ветвей, имеющих включенные формирователи 23. временных интервалов, а также длительности задержек для работ, выходя- из начального узла, сети и не выдавших сигналы Начало. В этом случае все триггеры 26 моделей 19 ветвей находятся в нулевом состоянии, так как ни один формирователь 23 не

50

55

выработал сигнал переполнения. Элемент ИЛИ 36 блока 20, объединяющий единичные выходы триггеров 26 выра батьшает запрещающий сигнал на прохождение топологической серии генератора 22 через элемент И 33 и через элемент НЕ 39 - разрешающий сигнал на вход элемента И 35, В результате импульсы измерительной серии генератора 22 проходят на входы формирователей 23 временных интервалов всех моделей 19 ветвей, но отсчитывают измерительную серию только формирователи, подготовленные сигналом с выхода элемента ИЛИ 31.

В то же время независимо от элемента И 35 блока 20 импульсы непосредственно с генератора 22 через вход 15 поступают на вход элемента И 6 всех блоков 17, но отсчитьгоают указанную серию в реальном времени только те блоки 17, которые соответствуют работам, имеющим задержку в управлении, т.е. блоки 17, имеющие триггеры 2 в единичном состоянии Счетчик 3 блока 17 отсчитывает величину реальной задержки управления до тех пор, пока на месте выполнения соответствующей работы не .будут приняты экстренные меры по устранению имеющихся неполадок и не будет выработан сигнал Начало через вход 8 на вход соответствующего блока 17. Последний сигнал в этом случае устанавливает триггер 1 в единичное сос- тояни е, триггер 2 - в нулевое состояние, а также проходит через элемент И 7, так как на другом входе элемента присутствует разрешающий сигнал с выхода дешифратора кодов, который определяет состояние счетчика 3, отличное от нулевого.

В результате на вход счетчика 3 блока 17 больще не поступают импульсы измерительной серии, сигнал с выхода элемента И 7 через выход 10 и элемент ИЛИ 31 подготавливает формирователь 23 временного интервала соответствующей модели 19 ветви к моделированию длительности выполнения работы,

Формирователи 23 временных интервалов моделей 19 ветвей отсчитывают

измерительную серию импульсов, соот- только от тех моделей ветвей, которые

ветствующую дпительности данной вет-п ви,. до тех пор, пока хотя бы один из них не вьфаботает сигнал, который установит в единичное состояние тригвходят в рассматриваемый узел, но не сформировали свою длительность, В этом случае запрещающий сигнал проходит на выход элемента И 34 и через

s

0

5

геры 26 и 27 своего блока 19 моделей ветви. С единичного выхода триггера 26 сигнал поступает в блок 20 формирования топологии на один из входов

элемента ИЛИ 36, к остальным входам которого подключены одноименные входы остальных моделей 19 ветвей. Пройдя через элемент ИЛИ 36, сигнал поступает на вход элемента НЕ 39, коO торый вырабатывает запрет на одном из входов элемента И 35. В результате запрещается поступление импульсов измерительной серии на входы ёсех блоков 19 моделей ветви, хотя это не обязательно для устройства дпя сопряжения с сетевой моделью, так как топологическая серия подаётся в ускоренном масштабе времени и коммутация блоков 19 моделей ветви выполнена до прихода следующего импульса измерительной серии. Сигнал с выхода элемента ИЛИ 36 также поступает на вход элемента И 33 и разрещает прохождение импульсов топологической серии с выхода генератора 22, которые проходят через элементы И 33, ИЛИ 37 и поступают на входы задатчиков 24 и 25 адресов всех блоков 19 моделей ветви. Задатчики 24 и 25 адресов начальных и конечных узлов отсчитьшают импульсы до тех пор, пока задатчик 25 адресов блоков 19 моделей ветвей, где сформирован временной интервал формирователем 23, не вьфаботает сигнал пере- 5 полнения. Сигнал с выхода задатчика 25 адресов, в котором записан адрес конечного узла ветви, устанавливает в нулевое состояние триггер 26, а также поступает на первый вход эле0 мента И 29 и на вход элемента НЕ 32.

Если ветвь, в которой появляется импульс на входе задатчика 23 адресов, закончила формирование временного интервала, то разрешакщий сиг5 нал с выхода триггера 27 проходит через элементы И 29 и ИЛИ 30 к одному из входов элемента И 34.

В тех случаях, когда импульсы на 0 выходе задатчика 25 адресов отсутствуют, на вход элемента И 34 разрещаю- щий сигнал поступает с выхода элемента НЕ 32. образом, запрет на входах элемента И 34 поступает

0

входят в рассматриваемый узел, но не сформировали свою длительность, В этом случае запрещающий сигнал проходит на выход элемента И 34 и через

элемент ИЛИ 3,8 на полюсы всех блоков

19моделей ветви. Этот сигнал за- преп;ает подготовку соответствующих формирователей 23 к отсчету импульсо с,генератора 22.

Если все ветви, входяш 5;е в рас- сматриваемьм узел, сформировали временной интервал, на выходе элемента И 34 блока 20 появляется разрешающий сигнёш, который поступает через элемент ИЛИ 38 на полюсы моделей ветвей Разрешающий сигнал в каждой модели 1 ветви поступает на вход элемента И 28 и далее через полюс 12 на вход элемента И 5 в каждом блоке 17, В моделях ветвей сигнал с элемента ШИ 38 блока 20 проходит через элемент И 26, если есть разрешение с выхода триггера 1 (выход 9) соответствующего блока 17 и есть в данный момент времени сигнал с выхода задатчи ка 24 адресов, т.е. в тех моделях ветвей, которые выходят из рассматриваемого узла и получили сигнал о начале выполнения рассматриваемой работы. Как и прежде, при отсутствии сигнала Начало на входе 8 в блоке 17 сигнал с выхода элемента ИЛИ 36 проходит через элемент ИЗ, устанавливает Триггер 2 в единичное состояние и включает это устройство для отсчета величины задержки управления

Импульсы с генератора 22 поступают на входы задатчиков 24 и 25 адресов до тех пор, пока хотя бы на одном из входов блока 20 присутствуе сигнал с выхода триггера 26 какого- либо блока 19. После того, как все триггеры 26 установлены в нулевое состояние выходными сигналами соответствующих задатчиков адресов, блок

20запрещает прохождение импульсов этой серии на входы задатчиков адресов, В блоке 20 разрешается беспрепятственное поступление импульсов измерительной серии на входы формирователей 23 временных интервалов Таким образом, работа устройства соп45 вход первого дополнительного элемента И подключен к выходу первого за- датчика блока моделей ветви, четвертый вход первого дополнительно го элемента И подключен к инверсному

ряжения и сетевой модели на каж;:1;ом шаге моделирования сети и контроля 50 выходу третьего триггера, прямой вы- управления в работах объекта состоит ход которого подключен к четвертому из двух чередующихся этапов: совмест- входу первого элемента И блока моде- ное формирование длительности ветви

лей ветви, вход установки в 1 третьего триггера, вход установки нуля 55 четвертого триггера и первый вход третьего дополнительного элемента И объединены и являются входом запуска устройства, прямой выход четвертого триггера и первый вход второго дои величины задержки управления, а также формирование топологии сети.

Моделирование сети продолжается до тех пор, пока не будет сформирован конечный узел сетевого графика.

1300А81

10

0

После этого все триггеры 26 блока 19 устанавливаются в нулевое состояние После этого сигнал с выхода элемента ИЛИ 38 блока 20 поступает через полюс 41 в блок 21 (фиг.2) на вход элемента И 51, а так как сформирован конечный узел сетевого графика, импульс переполнения с выхода задат- чика 45 проходит через элемент И 51 и устанавливает триггер 46 в нулевое состояние.

Процесс моделирования на этом заканчивается. Суммарное количество импульсов измерительной серии (реаль- нее время), поступающих на вход элемента И 35 с начала отсчета и до момента формирования конечного узла графика, равно величине длиннейшего пути сети или времени выполнения всего сетевого проекта. Счетчик 3 каждого блока 17 по окончании процесса моделирования хранит величину задержки управления соответствующей работы сетевого проекта, которая может быть использована при анализе возникших аззарийных ситуаций в технологическом процессе.

0

5

Формула изобретения

Устройство для моделирования сетевых графиков по авт.св. № 422002, отличающее ся тем, что, с целью повьшения точности, в него

3 введены третий и четвертый триггеры, первый, второй и третий дополнительные элементы И, счетчик и дешифратор кодов, первый вход первого дополнительного элемента И подключен к выхо40 ДУ третьего элемента ИЛИ блока формирования топологии, второй вход первого дополнительного элемента И подключен к инверсному выходу,второго триггера блока моделей ветви, третий

45 вход первого дополнительного элемента И подключен к выходу первого за- датчика блока моделей ветви, четвертый вход первого дополнительного элемента И подключен к инверсному

50 выходу третьего триггера, прямой вы- ход которого подключен к четвертому входу первого элемента И блока моде-

50 выходу третьего триггера, прямой вы- ход которого подключен к четвертому входу первого элемента И блока моде-

лей ветви, вход установки в 1 третьего триггера, вход установки нуля 55 четвертого триггера и первый вход третьего дополнительного элемента И объединены и являются входом запуска устройства, прямой выход четвертого триггера и первый вход второго дополнительного элемента И объединены и являются информационным выходом устройства, выход первого дополнительного элемента И подключен к входу установки в 1 четвертого триггера, выход третьего дополнительного элемента И подключен к первому входу дополнительного элемента ИЛИ блока моделей ветвей, второй вход третьего

Г

L.

дополнительного элемента И подключен к выходу дешифратора кодов, вход которого подключен к выходу счетчика, счетный вход которого подключен к выходу второго элемента И, второй вход которого rtoдключeн к первому выходу генератора импульсов, второй выход которого подключен к тактовому входу блока управления.

21

П

Редактор Л.Веселовская

Составитель Т.Сапунова Техред А.Кравчук

Заказ 1150/48Тираж 673

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

fr

„.I

Корректор А.Обручар

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования сетевого графика | 1985 |

|

SU1374252A1 |

| Устройство для моделирования сетевых графиков | 1983 |

|

SU1119024A1 |

| Устройство для моделирования сетевых графиков | 1983 |

|

SU1128272A2 |

| Устройство для моделирования сетевых графиков | 1976 |

|

SU556460A2 |

| Устройство для моделированияСЕТЕВОгО гРАфиКА | 1980 |

|

SU849232A2 |

| Вычислительное устройство для решения задач сетевого планирования | 1978 |

|

SU750503A1 |

| Устройство для моделирования сетевого графика | 1975 |

|

SU608169A1 |

| Устройство для расчета сетевыхгРАфиКОВ | 1979 |

|

SU851417A1 |

| Устройство для моделирования сетевых графиков | 1977 |

|

SU636635A2 |

| Устройство для моделирования сетевого графика | 1981 |

|

SU1012267A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения специализированных вычислительпых машин с реальным объектом. Целью изобретения является повышение точности. Устройство для моделирования содержит тре-о и. СЛ гч

| 1972 |

|

SU422002A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-30—Публикация

1985-02-05—Подача