Изобретение относится к области запоминающих устройств.

Известно магазинное запоминающее устройство (МЗУ) матричного типа, выполненное на криотронах, содержащее запоминающие ячейки с управляющими элементами.

Недостатком известного МЗУ является невозможность оперативного исключения неисправных запоминающих ячеек, что снижает надежность работы устройства.

Описываемое устройство отличается от известного тем, что в него введены детекторы неисправности, каждый из которых подключен через схему совпадения к двум соседним запоминающим ячейкам, за исключением двух крайних запоминающих ячеек сверху и снизу матрицы. Вентили выходных криотронов управляющего элемента четной /-ой запоминающей ячейки защунтированы сетками входных криотронов / + (2k + 1)-й и (/± 1)-й запоминающих ячеек (где 2k - количество неисправных запоминающих ячеек); вентили выходных криотронов управляющего элемента нечетной /-Й запоминающей ячейки зашунтированы сетками входных криотронов /-()-и и (/±1)-й запоминающих ячеек, а сетки выходных криотронов управляющих элементов соединены в последовательные цепи подготовки записи и чтения.

Эти отличия позволяют повысить наделсность работы устройства.

Кроме того, описываемое устройствоо отличается от известного тем, что каждая матрица по каждому направлению передачи сигналов содержит входной и выходной персисторные контуры с постоянной времени, меньщей постоянной времени числового контура запоминающей ячейки, подключенные к управляющим элементам соответствующих запоминающих ячеек, а шина питания на краях матриц и в месте их соединения состоит из двух ветвей, одна из которых содерл ит криотрон с сеткой, включенной в выходной контур t-й

матрицы, а другая - криотрон сброса н сетку управляющего криотрона входного контура (с±1)-й матрицы.

Такое выполнение устройства позволяет увеличить скорость передачи сигналов от матрицы к матрице.

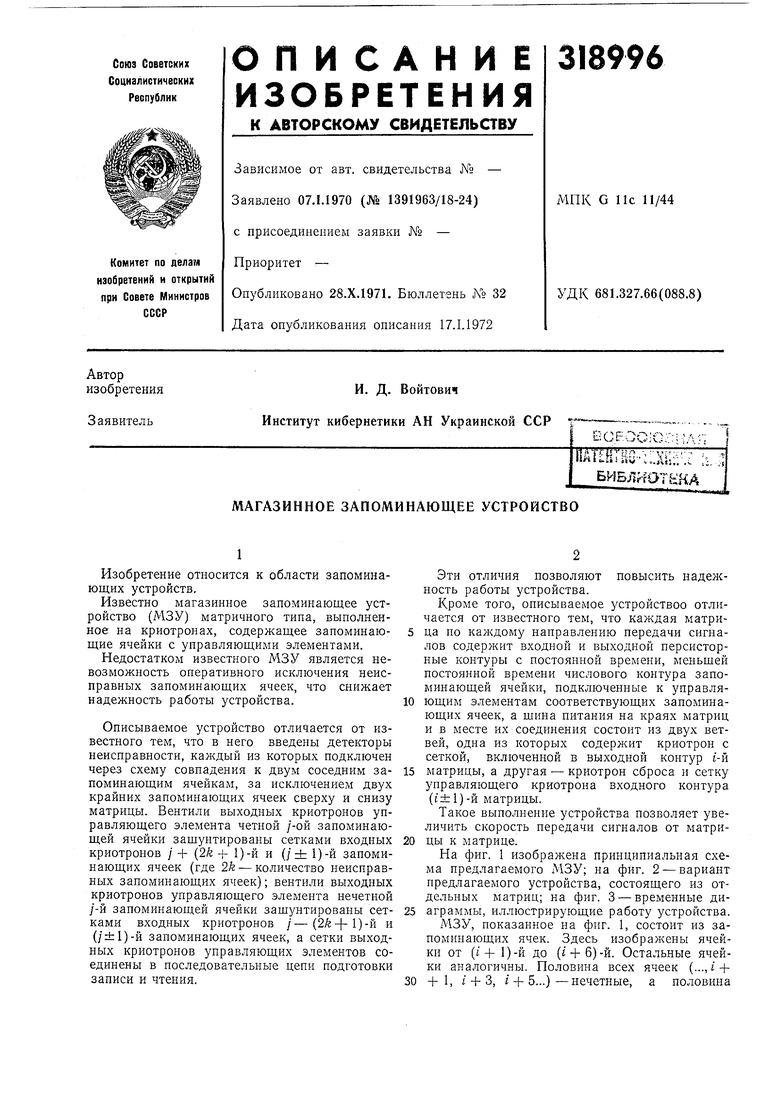

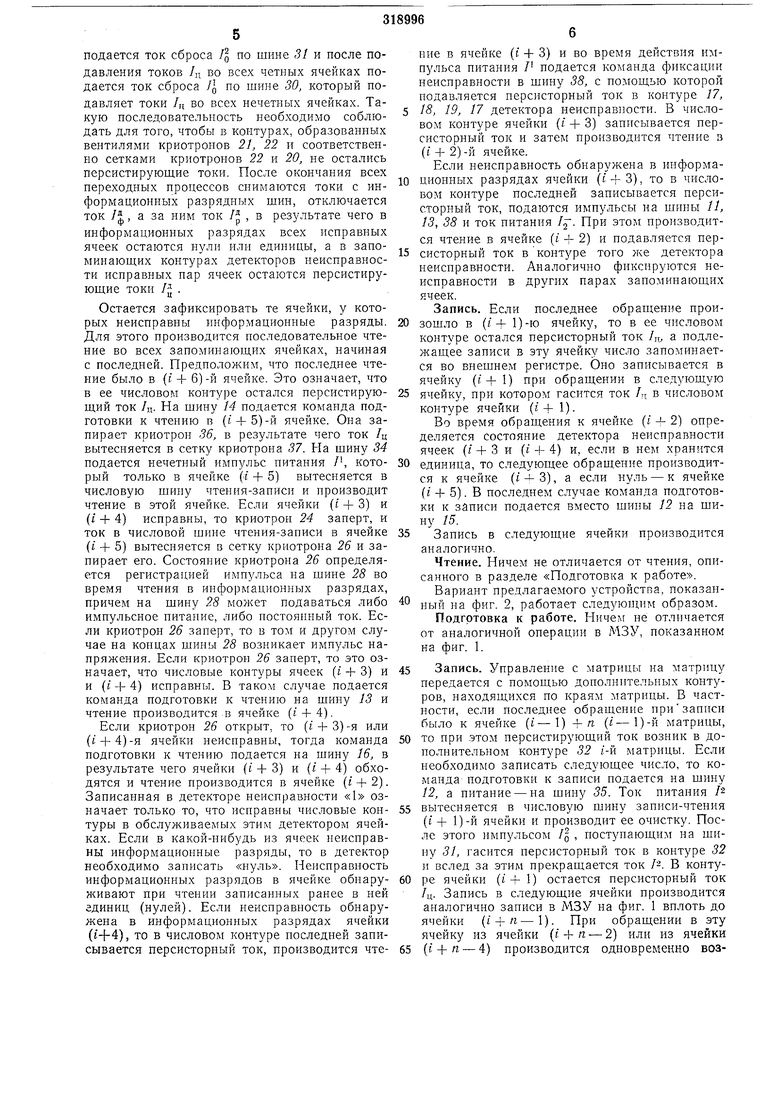

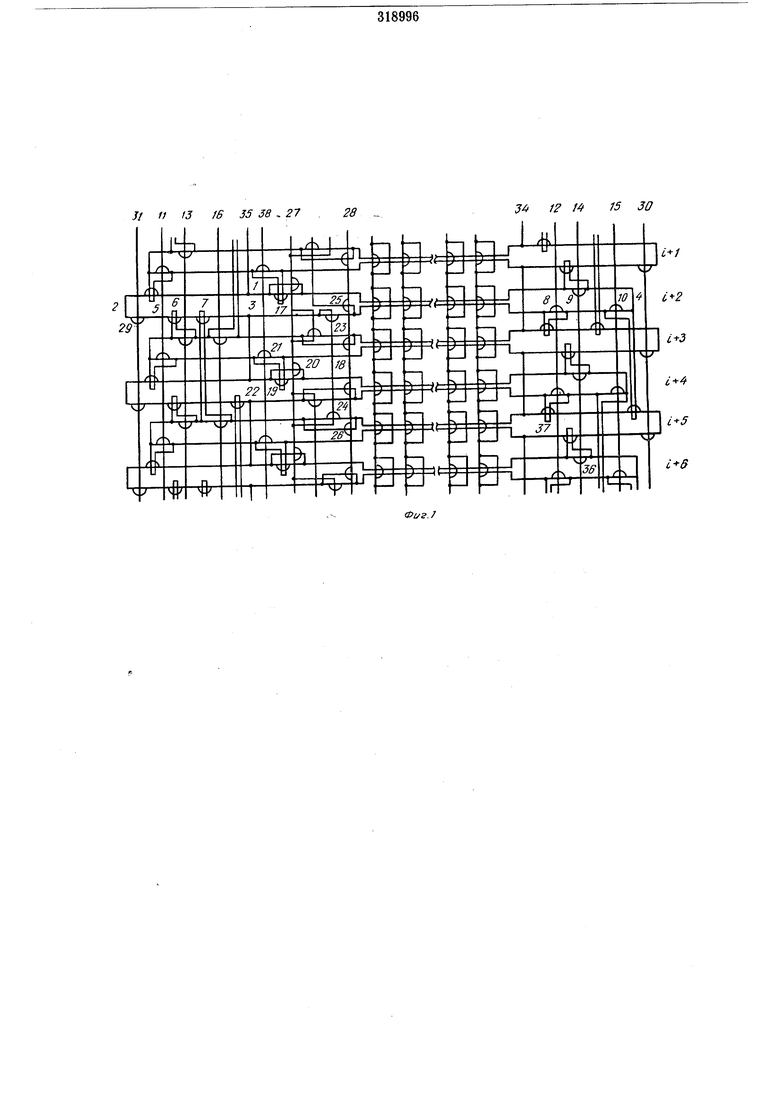

На фиг. 1 изобрал ена принципиальная схема предлагаемого МЗУ; на фиг. 2 - вариант предлагаемого устройства, состоящего из отдельных матриц; на фиг. 3 - временные диаграммы, иллюстрирующие работу устройства. МЗУ, показанное на фиг. 1, состоит из запоминающих ячек. Здесь изобрал ены ячейки от (/+ 1)-й до (г-1-6)-й. Остальные ячейки аналогичны. Половина всех ячеек (..., i +

(...,1 +2, i + 4, i + 6...) -четные. Здесь i-номер матрицы устройства (, 2,..,п).

В каждой ячейке запоминается т-разрядное число. Для запоминания, хранения и считывания одного бита информации служит известный однокриотронный запоминающий элемент. Однако вместо него можно использовать любой другой криогенный запоминающий элемент.

В каждой запоминающей ячейке имеется числовой персисторный контур. В ячейке (t+2), нанример, это контур 1, 2, 3, 4, 1. Запоминающая ячейка состоит из информационной части, управляющего элемента и детектора неисправности, охватывающего две ячейки. Информационная часть - это т запоминающих элементов и относящаяся к ним часть числового персисторного контура. В качестве управляющего элемента служат входные 5, 6 7 и выходные 8, 9, 10 управляющие криотроны, объединенные тем же числовым персисторным контуром.

Сетки входных управляющих криотронов подключены параллельно вентилям выходных управляющих криотронов соответствующих соседних ячеек. Сетки же выходных управляющих криотронов объединены в шины записи и чтения 11 -16. В качестве детектора неисправности служит запоминающий элемент с неразрушающим считыванием. Он состоит из персисторного контура 17, 18, 19, 17, входного криотрона записи 20, схемы совпадения на двух криотронах 21, 22, криотронов считывания 23, 24 и двух выходных криотронов 25, 26. Сетки криотронов схем совпадения соединены последовательно, образуя шину 27 фиксации неисправности. Вентили выходных криотронов образуют выходную шину считывания 28.

Каждый детектор неисправности предназначен для определения неисправности двух запоминающих ячеек и исключения их во время работы.

В каждой ячейке имеется криотрон сброса (в ячейке t + 2 криотрон 29), предназначенный для подавления в числовом контуре персисторного тока или вытеснения тока питания в числовую шину записи-чтения (незаконченный контур) 1, 4, 3 из ее шунта (контур) /, 2, 3. Числовая ветвь имеет значительно большую индуктивность, чем ее шунт, так как в ней последовательно соединены т сеток запоминающих элементов, а в шунте только несколько вентилей (сетка криотрона имеет в десятки раз большую индуктивность, чем вентиль) .

Сетки криотронов сброса нечетных и четных ячеек объединены в нечетную 30 и четную 31 шины сброса.

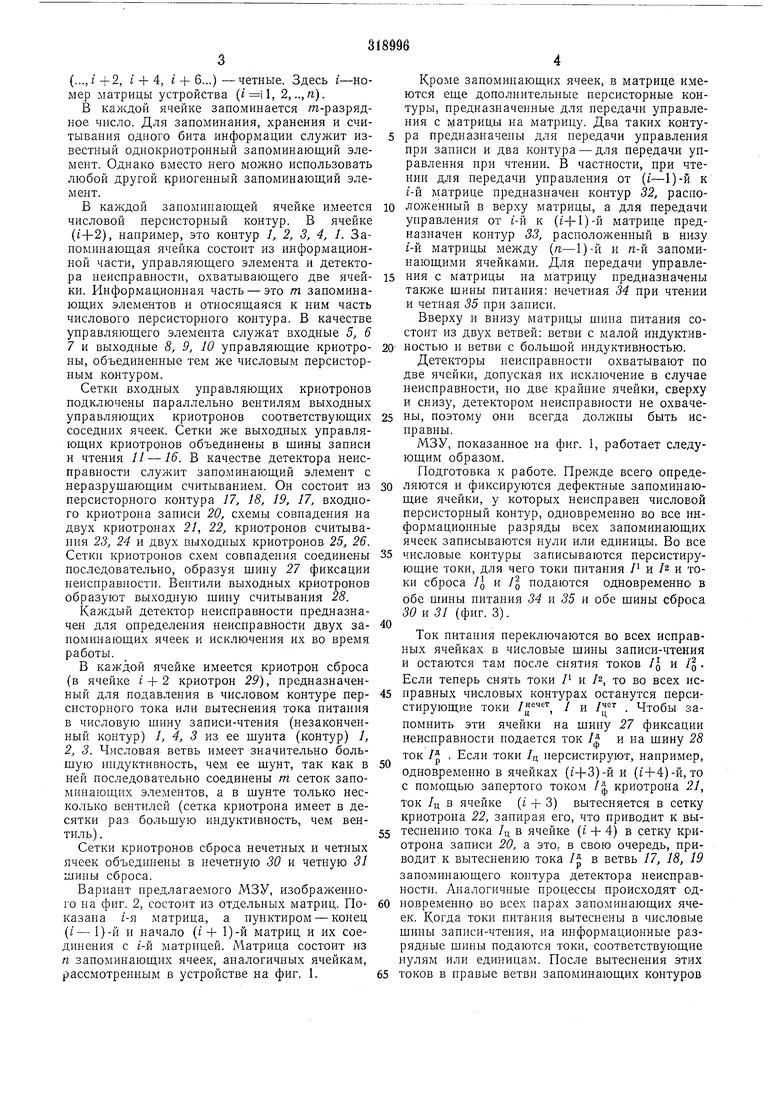

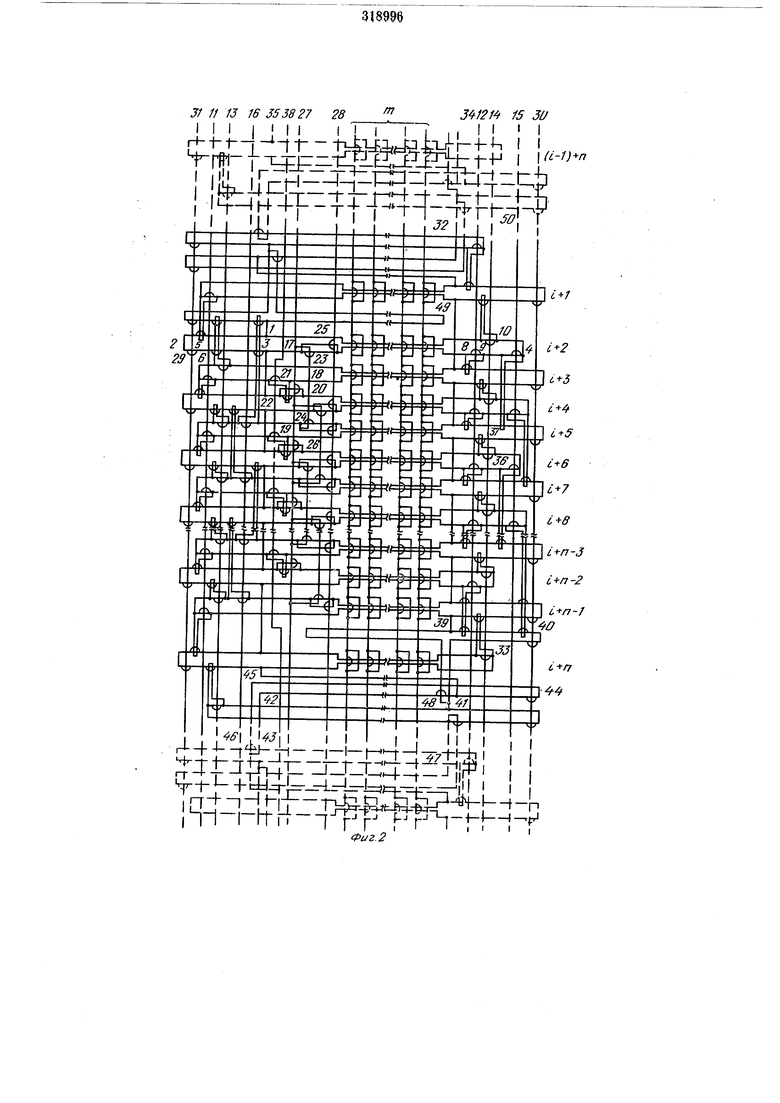

Вариант нредлагаемого МЗУ, изображенного на фиг. 2, состоит из отдельных матриц. Показана г-я матрица, а пунктиром - конец (i- 1)-й и начало (г + 1)-й матриц и их соединения с г-й матрицей. Матрица состоит из л запоминающих ячеек, аналогичных ячейкам, рассмотренным в устройстве на фиг. 1.

Кроме запоминающих ячеек, в матрице имеются еще дополнительные иерсисторные контуры, предназначенные для передачи управления с матрицы на матрицу. Два таких контура предназначены для нередачи управления при записи и два контура - для передачи управления при чтении. В частности, при чтении для передачи управления от (i-1)-й. к t-й матрице предназначен контур 32, расположенный в верху матрицы, а для передачи управления от f-й к (г-|-1)-й матрице предназначен контур 33, расположенный в низу j-й матрицы между (п-1)-й и п-й запоминающими ячейками. Для передачи управления с матрицы на матрицу предназначены также шины питания: нечетная 34 при чтении и четная 35 при записи.

Вверху и внизу матрицы шина питания состоит из двух ветвей: ветви с малой индуктив0- ностью и ветви с большой индуктивностью.

Детекторы неисправности охватывают по две ячейки, допуская их исключение в случае неисправности, но две крайние ячейки, сверху и снизу, детектором неисправности не охвачены, поэтому они всегда должны быть иснравны.

МЗУ, показанное на фиг. 1, работает следующим образом. Подготовка к работе. Прежде всего определяются и фиксируются дефектные запоминающие ячейки, у которых неисправен числовой персисторный контур, одновременно во все информационные разряды всех запоминаюш,их ячеек записываются нули или единицы. Во все

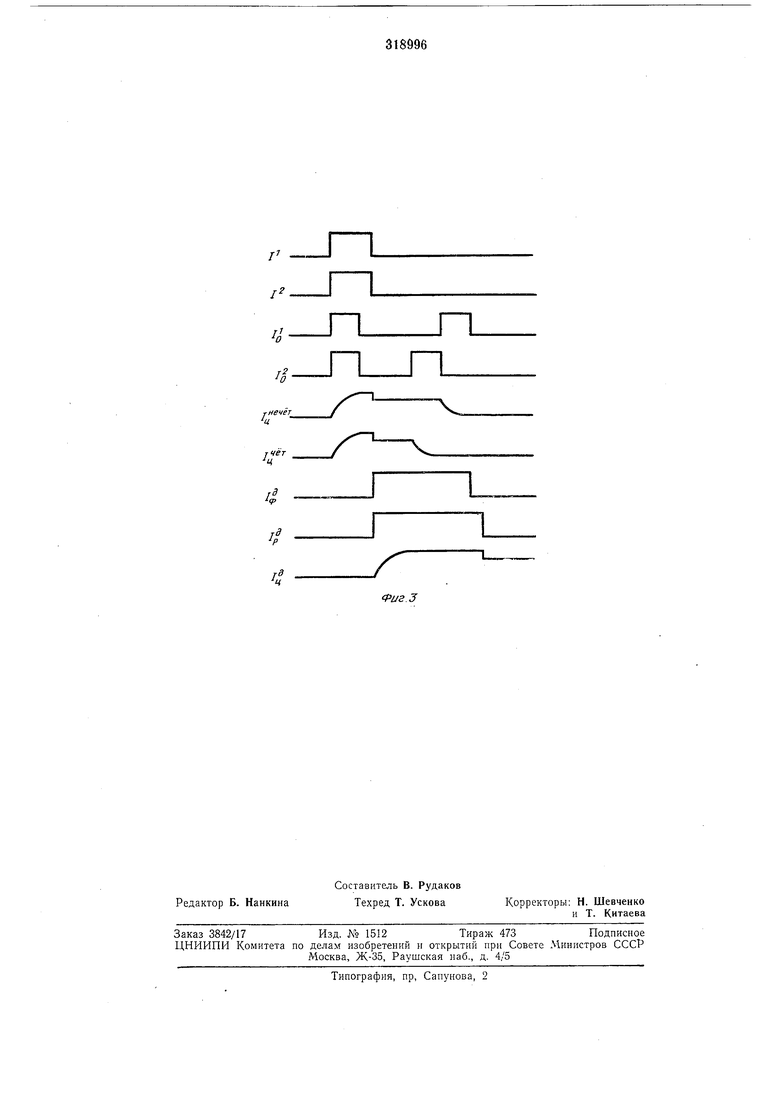

5 числовые контуры записываются персистирующие токи, для чего токи питания / и /2 и токи сброса /о и /о подаются одновременно в обе шины нитания 34 и 35 и обе шины сброса 30 и 31 (фиг. 3).

Ток питания переключаются во всех исправных ячейках в числовые шины записи-чтения и остаются там после снятия токов /д и /д . Если теперь снять токи / и /2, то во всех ис5 нравных числовых контурах останутся персистирующие токи /««чет / JJ /чет Чтобы запомнить эти ячейки на шину 27 фиксации неисправности подается ток /f и на шину 28 ток / . Если токи /ц иерсистируют, например, одновременно в ячейках (г+3)-й и (1+4)-й, то с помощью запертого током /| криотрона 21, ток /ц в ячейке (i + 3) вытесняется в сетку криотрона 22, запирая его, что приводит к вытеснению тока /ц в ячейке (t + 4) в сетку криотрона записи 20, а это. в свою очередь, приводит к вытеснению тока / в ветвь 17, 18, 19 запоминающего контура детектора неисправности. Аналогичные процессы происходят одповременно во всех парах запоминающих ячеек. Когда токи питания вытеснены в числовые шины записи-чтения, на информационные разрядные шины подаются токи, соответствующие нулям или единицам. После вытеснения этих

подается ток сброса /д по шине 31 и после подавления токов /ц во всех четных ячейках подается ток сброса /Q по шине 30, который подавляет токи /ц во всех нечетных ячейках. Такую последовательность необходимо соблюдать для того, чтобы в контурах, образованных вентилями криотропов 21, 22 и соответственно сетками криотронов 22 и 20, не остались персистирующие токи. После окончания всех переходных процессов снимаются токи с ипформациопных разрядных шин, отключается ток /I, а за ним ток / , в результате чего в информационных разрядах всех исправных ячеек остаются нули или единицы, а в запоминаюш;их контурах детекторов неисправности исправных пар ячеек остаются персистируюш:ие токи /jj .

Остается зафиксировать те ячейки, у которых неисправны информационные разряды. Для этого производится последовательное чтение во всех запоминающих ячейках, начиная с последней. Предположим, что последнее чтение было в (t + 6)-и ячейке. Это означает, что в ее числовом контуре остался персистирующий ток /ц. Па шину 14 подается комапда подготовки к чтению в (г + 5)-й ячейке. Она запирает криотрон 36, в результате чего ток /ц вытесняется в сетку крнотрона 37. Па шину 34 подается нечетный импульс питания /, который только в ячейке (i + 5) вытесняется в числовую шину чтения-записи и производит чтение в этой ячейке. Если ячейки (I + 3) и (/ + 4) исправны, то криотрои 24 заперт, и ток в числовой шине чтения-записи в ячейке (1 + 5) вытесняется в сетку криотрона 26 и запирает его. Состояние криотрона 26 определяется регистрацией импульса на шине 28 во время чтения в информационных разрядах, причем на шину 28 может подаваться либо импульсное питание, либо постоянный ток. Если криотрон 26 заиерт, то в том и другом случае на концах шины 28 возникает импульс напряжения. Если криотрон 26 заперт, то это означает, что числовые контуры ячеек (t -Ь 3) и и (i + 4) иснравны. В таком случае подается команда подготовки к чтению на шину 13 и чтение производится в ячейке (i + 4).

Если криотрон 26 открыт, то (i -Ь 3) -я или (t + 4)-H ячейки неисиравны, тогда команда подготовки к чтению подается па шину 16, в результате чего ячейки (i + 3) и (/ + 4) обходятся и чтение производится в ячейке (г+ 2). Записанная в детекторе неисправности «1 означает только то, что исиравны числовые контуры в обслуживаемых этим детектором ячейках. Если в какой-нибудь из ячеек неисправны информационные разряды, то в детектор необходимо записать «нуль. Пеисправность информационных разрядов в ячейке обнаруживают при чтении записанных ранее в пей единиц (нулей). Если неисправность обнаружена в информационных разрядах ячейки («+4), то в числовом контуре последней записывается персисторный ток, производится чтение в ячейке (i Ч- 3) и во время действия импульса питания / подается комапда фиксации неисправности в шину 55, с номощью которой подавляется персисторный ток в контуре 17, 18, 19, 17 детектора неисправности. В числовом контуре ячейки (i + 3) заппсывается персисторпый ток и затем производится чтение в (i + 2) -и ячейке. Если неисправность обнаружена в информационных разрядах ячейки (t + 3), то в числовом контуре последней записывается перспсторный ток, подаются импульсы на шины 11, 13, 38 и ток питання /. При этом производится чтение в ячейке (i -Ь 2) и нодавляется нерсисторный ток в контуре того же детектора неисправности. Аналогично фиксируются неисправности в других парах запоминающих ячеек.

Запись. Если последнее обращение произошло в (/+ 1)-ю ячейку, то в ее числовом контуре остался нерсисторный ток /ц, а подлежащее записи в эту ячейку число запоминается во внешнем регистре. Оно записывается в ячейку (f+1) при обращении в следующую

ячейку, при котором гасится ток /д в числовом контуре ячейки (i + 1).

Во время обращения к ячейке (1 -Ь 2) определяется состояпие детектора неисправности ячеек (/ + 3 и (i + 4) и, если в нем хранится

единица, то следующее обращение производится к ячейке (г 3), а если нуль - к ячейке (г Ч- 5). В последнем случае команда подготовки к записи подается вместо щины 12 на шину 15.

Запись в следующие ячейки производится аналогично.

Чтение. Пичем не отличается от чтения, описанного в разделе «Подготовка к работе. Вариапт предлагаемого устройства, показанный на фиг. 2, работает следующим образом.

Подготовка к работе. Пичелг не отличается от аналогичной операции в МЗУ, показанном на фиг. 1.

Запись. Управление с матрицы на матрицу передается с помощью дополннтельных контуров, находящихся по краям матрицы. В частности, если последнее обращение призаписи было к ячейке (i-1) +п (i-1)-й матрицы,

то при этом персистирующий ток возник в дополнительном контуре 32 j-й матрицы. Если необходимо записать следующее число, то команда подготовки к записи подается на шину 12, а питание - на шину 35. Ток питания /

вытесняется в числовую шину записи-чтения (i + 1)-й ячейки и производит ее очистку. После этого импульсом /о , поступающим на щину 31, гасится перснсторный ток в контуре 32 и вслед за этим прекращается ток /2. В контуре ячейки (i + 1) остается персисторный ток /ц. Запись в следующие ячейки производится аналогично записи в МЗУ на фиг. 1 внлоть до ячейки (i + п-1). При обращении в эту ячейку из ячейки (t-b«--2) или из ячейки

буждение контура 33 с помощью криотронов 39 или 40. При снятии тока питания / в числовом контуре ячейки (/ + «- I) ив контуре 33 остаются персистирующие токи. Если теперь подать ток питания / на шину 35, то он производит очистку ячейки (i + n) и одновременно вытесняется из ветви 41, 42, 43 с малой индуктивностью в ветвь 41, 44, 45, 43 с большой индуктивностью, запирая входной криотрон 6 в первом дополнительном контуре 47 следующей матрицы, аналогичном контуру 32 в рассматриваемой матрице. Ток питания /2 вытесняется в контуре 47 в ветвь с большой индуктивностью. Если теперь подать ток сброса/о на шину 30, то он нодавит персистирующие токи в числовом контуре ячейки (i+n-1) и в контуре 33, а также вернет ток /2 питания из ветви 41, 44, 45, 43 в ветвь 41, 42, 43, открыв криотрон 46. Снимается ток /з, в результате чего остается персистирующий ток в ячейке (г + /г) и в контуре 47 следующей матрицы. Таким образом, осуществляется передача управления с матрицы на матрицу. Она возможна даже при наличии в ветвях 45, 43 и 42, 43 небольшого сонротивления, важно, чтобы оно было в несколько раз меньше сопротивления криотрона 48.

Быстродействие памяти при переходе с матрицы на матрицу также не теряется, так как суммарную постоянную времени контуров 47 и ветвей 41, 44, 45, 43, 42, 41 можно сделать меньше постоянной времени числового контура запоминающей ячейки.

Чтение. Ничем но существу не отличается от чтения, описанного в разделе «Подготовка к работе. Передача управления с t-й матрицы к матрице (i-1) осуществляется так же, как и при записи только уже с помощью тока питания и контуров 49 (в матрице I) и 50 (в матрице I- 1).

В описанных МЗУ предусмотрено исключение только по одной паре ячеек. Но и при этом по всему МЗУ можно исключить почти половину ячеек. Если добавить связи между

более удаленными ячейками, то появится возможность исключения нескольких расположенных подряд пар ячеек.

Предмет изобретения

1.Магазинное запоминающее устройство матричного типа, выполненное на криотронах, содержащее запоминающие ячейки с управляющими элементами, отличающееся тем, что, с целью повыщения надежности работы устройства, в него введены детекторы неисправности, каждый из которых подключен через схему совпадения к двум соседним заноминающим ячейкам, за исключением двух крайних запоминающих ячеек сверху и снизу матрицы, вентили выходных криотронов управляющего элемента четной I-VL запоминающей ячейки зашунтированы сетками входных криотронов / + + (2й+1)-й и (/±1)-й запоминающих ячеек (где 2k количество неисправных запоминающих ячеек), вентили выходных криотронов управляющего элемента нечетной /-и запоминающей ячейки защунтированы сетками входных криотронов /- (2fe + 1)-й и fj ± 1)-й запоминающих ячеек, а сетки выходных криотронов управляющих элементов соединены в последовательные цепи подготовки записи и чтения.

2.Устройство по п. 1, отличающееся тем, что, с целью увеличения скорости передачи сигналов от матрицы к матрице, каждая матрица по каждому направлению передачи сигналов содержит входной и выходной персисторные контуры с постоянной времени, меньшей постоянной времени числового контура запоминающей ячейки, подключенные к управляющим элементам соответствующих запоминающих ячеек, а щина питания на краях матриц и в месте их соединения состоит из двух ветвей, одна из которых содержит криотрои с сеткой, включенной в выходной контур г-й матрицы, а другая - криотрон сброса и сетку управляющего криотрона входного контура (t+l)-и матрицы.

3 12 /- 15 30

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU301741A1 |

| Запоминающая ячейка на криотронах | 1964 |

|

SU443410A1 |

| ПЛЛ I(nATEHTHO-M^ii^E кдя!_БИ5ЛИОТЕНА•• ~^^^^* I 11 ^_ | 1971 |

|

SU299872A1 |

| КРИОГЕННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU265188A1 |

| КРИОТРОКНОЕ АССОЦИ \ТИВНОЕ ЗАПОМИНАЮЩЕЕ | 1973 |

|

SU364028A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЧИСЛОВЫМИ ЛИНЕЙКАМИ КРИОТРОННОГО АССОЦИАТИВНОГО ЗАПОМИНАЮЩЕГОУСТРОЙСТВА | 1972 |

|

SU343298A1 |

| КРИОТРОННЫЙ АССОЦИАТИВНЫЙ ЗАПОМИНАЮЩИЙЭЛЕМЕНТ | 1971 |

|

SU301742A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЧИСЛОВЫМИ ЛИНЕЙКАМИ КРИОТРОННОГО АССОЦИАТИВНОГО ЗАПОМИНАЮЩЕГОУСТРОЙСТВА | 1970 |

|

SU276167A1 |

| ЭЛЕМЕНТ КРИОТРОННОИ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1973 |

|

SU394941A1 |

| МАТРИЦА КРИОТРОННОГО АССОЦИАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1972 |

|

SU354472A1 |

У

/ ч

L

JL

3ff

J7 // 13 16 353827 28 15 3U

I I I I M II I I I III I I

q:lt4 b. t --

/о

//

П.

J

.З

Даты

1971-01-01—Публикация