Изобретение относится к вычислительной технике.

Известны криогенные запоминающие устройства, содержащие блок хранения информации, подключенный к «единичным и «нулевым адресным шинам блока расшифровки адреса. Они недостаточно надежны и технологичны.

Описываемое устройство отличается тем, что, с целью повышения надежности и упрощения технологии его изготовления, оно содержит запоминающие и дешифраторные Платы, собранные в плоские блоки. Выходные шины .дешифраторных плит выведены с двух сторон, а их соединения с запоминающими платами выполнены внутри блока, например, путем напыления в вакууме.

С целью исключения перекрестных соединений между дешифраторными платами внутри блока и между блоками выходы старших разрядов адреса всех дешифраторных плат содержат по две «нулевые адресные шины и по одной «единичной, нанесенной между «нулевыми.

На фиг. 1 показана блок-схема устройства.

Запоминающие блоки 1 соединены между собой по разрядным шинам 2 и 5 и адресным шинам 4. Каждый блок состоит из -плат двух типов - дешифраторных 5 и запоминающих 6.

Дешифраторные платы представляют собой трехтактные дешифраторы для грубой расшифровки адреса по старшим разрядам кода адреса, поступающего по шинам 7-12.

Запоминающие платы представляют собой числовые линейки 13, на которые нагружены криотронные древовидные дешифраторы 14 с малым числом выходов.

В древовидных дешифраторах расшифровываются младшие разряды кода адреса, пост}пающие по шинам 15-18. Питание на нужный древовидный дешифратор подается с помощью трехтактного дешифратора, находящегося на соответствующей плате.

Система двухступенчатой расщифровки адреса (сначала в трехтактном дешифраторе, а затем в древовидном) сокращает число соединений между дешифраторными и запоминающими платами и увеличивает плотность компоновки запоминающих элементов.

В дешифраторной плате 5 выходные цепи 19 имеются с двух сторон. К ним присоединяются запоминающие платы 6 с половинной разрядностью каждая, что увеличивает быстродействие памяти.

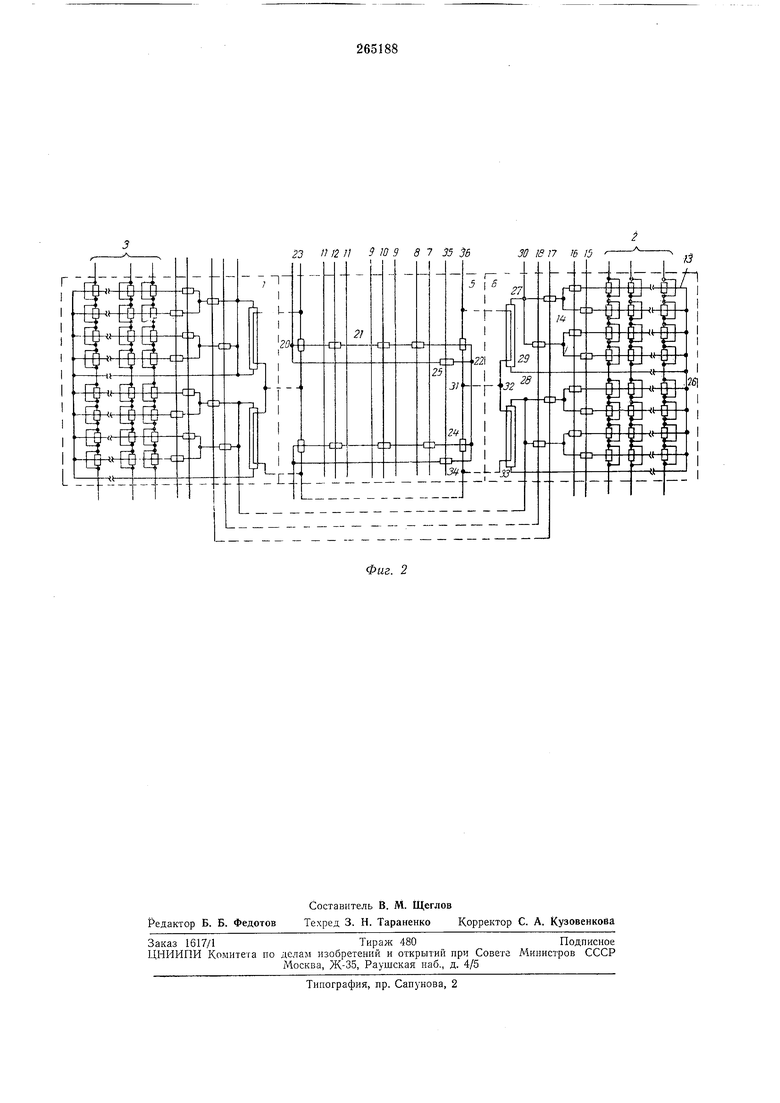

Конструктивно дешифраторные и запоминающие платы изготавливаются методом пленочной технологии на отдельных подложках. Те и другие платы технологически одинаковы. который закрывают изоляционным слоем, затем оловянный рисунок, изоляционный слой и свинцовый рисунок. После индивидуальной проверки и отбраковки дешифраторные ,и запоминающие платы монтируют на общем основании и соединения между ними напыляют в вакууме. Полученные таким образом блоки / также (проходят индивидуальную проверку и отбраковку, после которой происходит сборка запоминающего устройства (ЗУ). При сборке ЗУ, а также самих блоков возникает проблема соединений адресных шин между дешифраторными платами) все остальные соединения просты - однослойные прямые линии). Поскольку все дишифраторные платы одинаковы, соединить их нужно так, чтобы при заданном коде адреса выбиралась только одна соответствующая ему плата. Следовательно, некоторые из соединений должны быть перекрестными. Такие соединения нетехнологичны. Чтобы их избежать, в предлагаемом устройстве в log2A старших разрядах кода адреса (N - общее число дешифраторных плат в памяти) кодовые шины делают не двойными (единичная и нулевая), а тройными (одна единичная и две нулевые или две единичные и одна нулевая). Тогда вместо перекрестных получаются соединения, сдвинутые в одну или другую сторону, как показано на фиг. 1. Изображенное здесь устройство состоит из двух блоков, в каждом из которых имеется по две дешифраторные платы. Следовательно, здесь N 4 и log2A/ 2. Поэтому тройные кодовые шины предусмотрены только в двух старших разрядах (шины 9, 10, 9 и 11, 12, 11). На фиг. 2 показана принципиальная схема одного блока памяти, приведенного на фиг. 1. Он состоит из трех плат - одной дешифраторной и двух запоминающих. Дешифраторная плата, в свою очередь, состоит из соединенных последовательно кодовых контуров 20-21- 22--20. На вход 23 этой цепочки подается постоянный ток питания /д дешифратора. Каждый кодовый контур состоит из кодовой ветви 20-21-22, управляющей выходными криотронами, и шунта 20-22. В кодовую ветвь включены кодовые криотроны, управляемые импульсами в кодовых шинах (15-18, 7-12), и вентили 24 выходных криотронов дешифраторной платы. Шунтом является вентиль 25 криотрона начальной установки. Показанная на фиг. 2 схема трехтактного дещифратора- не единственная. Она может быть построена и по другим принцина.м. Запоминающая плата, как следует на фиг. 2, 55 разбита на группы числовых линеек по числу выходов древовидных дешифраторов. Одни концы адресных проводников числовых линеек подключены к выходам древовидных дешифраторов, а другие соединены вместе в точке 26. Между точкой 26 и основанием древовидного дещифратора (точкой 27) включен шунт 27- 28-26, состоящий из обходной шины 23-26 и вентиля входного криотрона 29. Этот крио60мяти можно -сделать линейным. Так как в данном случае древовидные дешифраторы имеют малое число выходов, то сохраняется периодичность структуры запоминающей платы, что важно для фотолитографической технологии. Запоминающая -плата питается от источника постоянного тока 1, поступающего на вход 50. Выходные криотроны дешифраторной платы и выходные сетки запоминающих плат образуют нередаточные контуры 31-32--33-34-31. Перед началом работы памяти ее очищают. Для этого на вход 35 подают имнульс /i начальной установки в дешифраторной плате и одновременно - импульсы на нулевые и единичные разряды той части кода адреса, которая расшифровывается в древовидных дешифраторах (щины 15-18). Импульс начальной установки переключает ток питания /д дешифраторной платы в ветви 20-21-22, а импульсы в адресных шинах запоминающей платы переключают ток питания /„ в щунты 27- 28-26. После очистки память работает в три такта: I. 3 а и ом и н ан и е а д р е с а в кодовом контуре На входы 15, 17, 7, 9, 11, или 16, 18, 8, 10. 12 подается код адреса в виде токовых импульсов. При этом импульсы в шинах 15, 17 или 16, 18 оставляют открытой только одну ветвь во всех древовидных дешифраторах, а импульсы в шинах 7,9, 11 или 8, 10, 12, закрывая соответствующие вентили кодовых криотронов, переключают ток питания /д в шунты во всех кодовых контурах, кроме выбранного. И. Считывание и стирание. В этом такте Происходят передача состояния кодового контура трехтактного дешифратора в соответствующую группу числовых линеек и считывание. На вход 36 подается импульс /2, который во всех кодовых контурах, кроме выбранного, проходит преимущественно по вентилям 24 выходных криотронов дешифраторной платы или, что то же самое, по вентилям входных криотронов передаточных контуров. Это происходит потому, что индуктивность входной ветви 31-35 передаточного контура меньше индуктивности выходной ветви 31- 32-33-34. В выбранном контуре трехтактного дешифратора входной криотрон передаточного контура запирается, вследствие чего ток /2 в этом передаточном контуре вытесняется в выходную ветвь, запирая таким образом щунт соответствующей группы чисел в запоминающей плате. Так как импульсы кода адреса (во всяком случае той его части, которая расшифровывается в древовидных дешифраторах) еще не сняты, ток питания запоминающей нлаты переключается в одну числовую линейку, соответствующую заданному адресу. ПрИ этом считывается информация, записанная в этой линейке. Информация появляется в виде импульсов напряжения на тех разрядных шинах (2 и ), где были записаны единицы.

III. Запись и регенерация. Считывание происходит с разрушением информации. Поэтому цикл считывания должен завершаться восстановлением считанной информации в выбранной числовой линейке. Если выполняется команда записи, на место считанной информации необходимо записать новую. В том и другом случаях в те разрядные шины, куда необходимо записать единицы, подаются импульсы разрядной записи /р. Чтобы информация записалась, необходимо ток питания /„ выключить из выбранной числовой линейки, причем это следует сделать раньше момента прекращения импульсов /р.

Для этого одновременно во все адресные шины 15-18 подаются импульсы с таким расчетом, чтобы ток /м из числовой линейки зытеснился в шунт раньше момента прекращения импульсов /р . Одновременно с записью осуществляется переключение тока питания /д во всех контурах дешифраторной платы в кодовые ветви. Для этого на вход 35 подается импульс /1.

Предмет изобретения

1.Криогенное запоминающее устройство, содержащее блок хранения информации, подключенный к «единичным и «нулевым адресным шинам блока расшифровки адреса, отличающееся тем, что, с целью увеличения надел ности работы устройства и упрощения технологии его изготовления, оно содержит запоминающие и дешифраторные 1платы, собранные в плоские блоки, при этом выходные шины дешифраторных плат выведены с двух сторон, а их соединения с запоминающими платами выполнены внутри блока, например путем напыления в вакууме.

2.Устройство по п. 1, отличающееся тем, что, с целью исключения перекрестных соединений между дешифраторными платами внутри блока и между блоками, выходы старших раз,рядол адреса всех дешифраторных плат содержат по две «нулевые адресные шины н по одной «единичной, нанесенной мелсду «нулевыми.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХТАКТНЫЙ КРИОТРОННЫЙ ДЕШИФРАТОР | 1970 |

|

SU262953A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU301741A1 |

| БИБЛИОТЕКА j | 1971 |

|

SU296259A1 |

| КРИОТРОННЫЙ ДЕШИФРАТОР | 1971 |

|

SU292596A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| МАТРИЦА КРИОТРОКНОГО АССОЦИАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1972 |

|

SU347798A1 |

| Логическое запоминающее устройство | 1986 |

|

SU1316047A1 |

| МАТРИЦА КРИОТРОННОГО АССОЦИАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1972 |

|

SU354472A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

I I I I

JIM

7/7

-JJ:

Даты

1970-01-01—Публикация