Изобретение предназначено для использования в вычислительной технике и цифровой автоматике.

Известные двоичные потенциальные счетчики, содержащие триггеры, потенциальные схемы совпадения, собирательные схемы и инверторы имеют малую надежность и невысокую помехоустойчивость.

Предложенное устройство отличается от известных тем, что единичный выход триггера предыдущего разряда подключен ко входам схем совнадения последующего разряда, выходы схем совпадения в каждом плече триггера через соответствующую собирательную схему соединены со входом одной из схем совпадения в том же плече триггера и через инвертор - со входом схемы совпадения противоположного нлеча триггера.

Это отличие устраняет указанные недостатки.

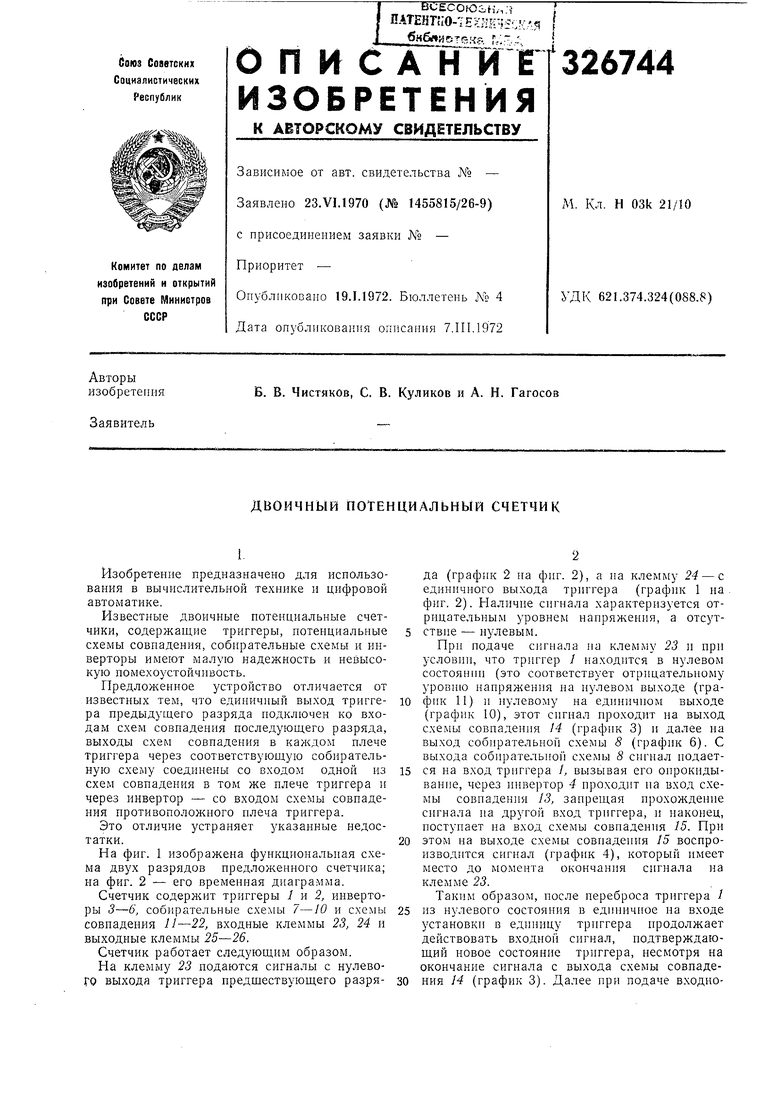

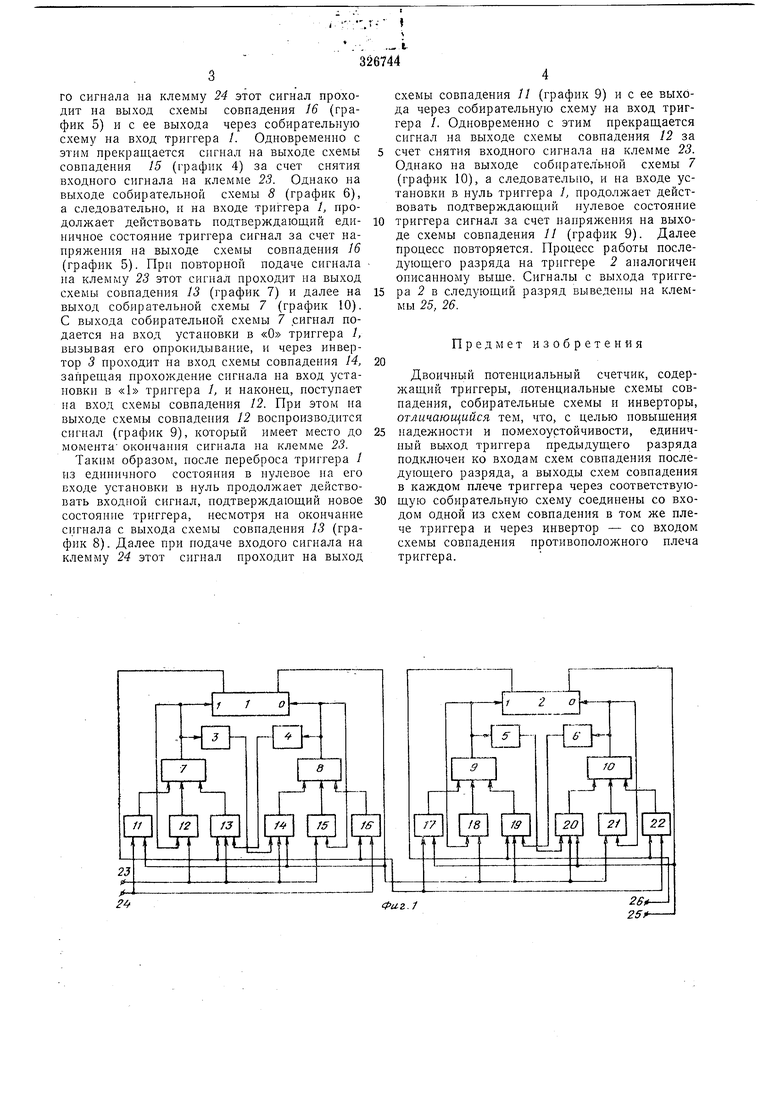

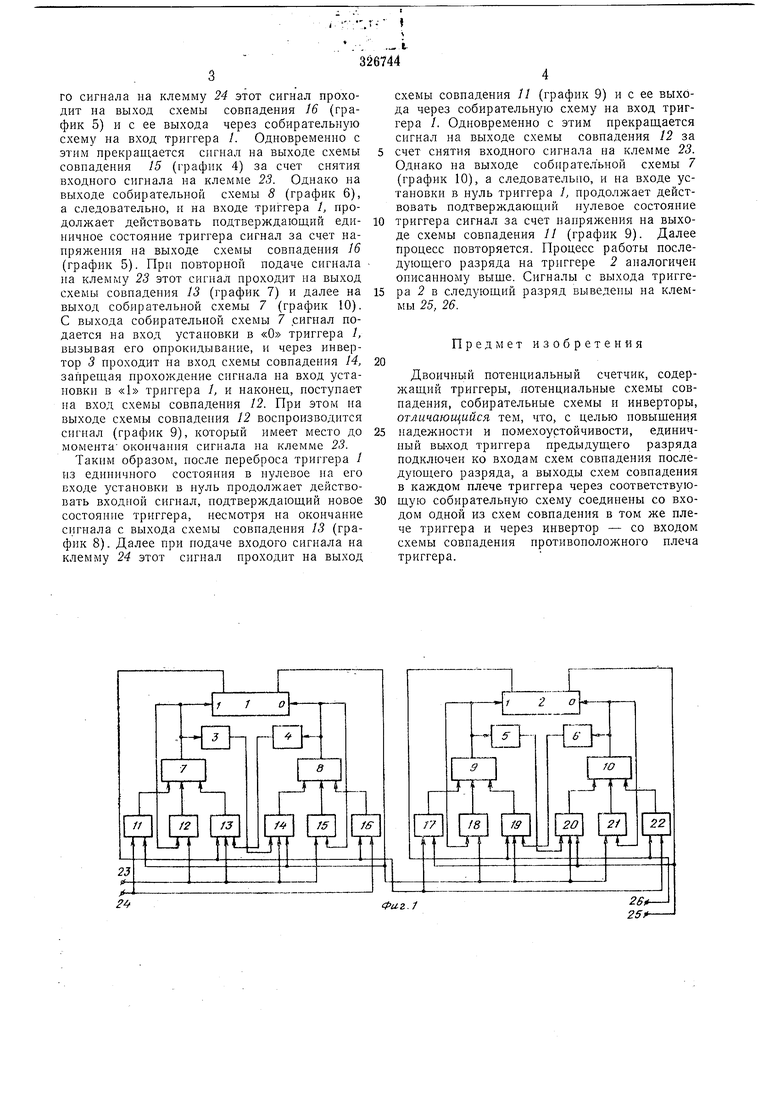

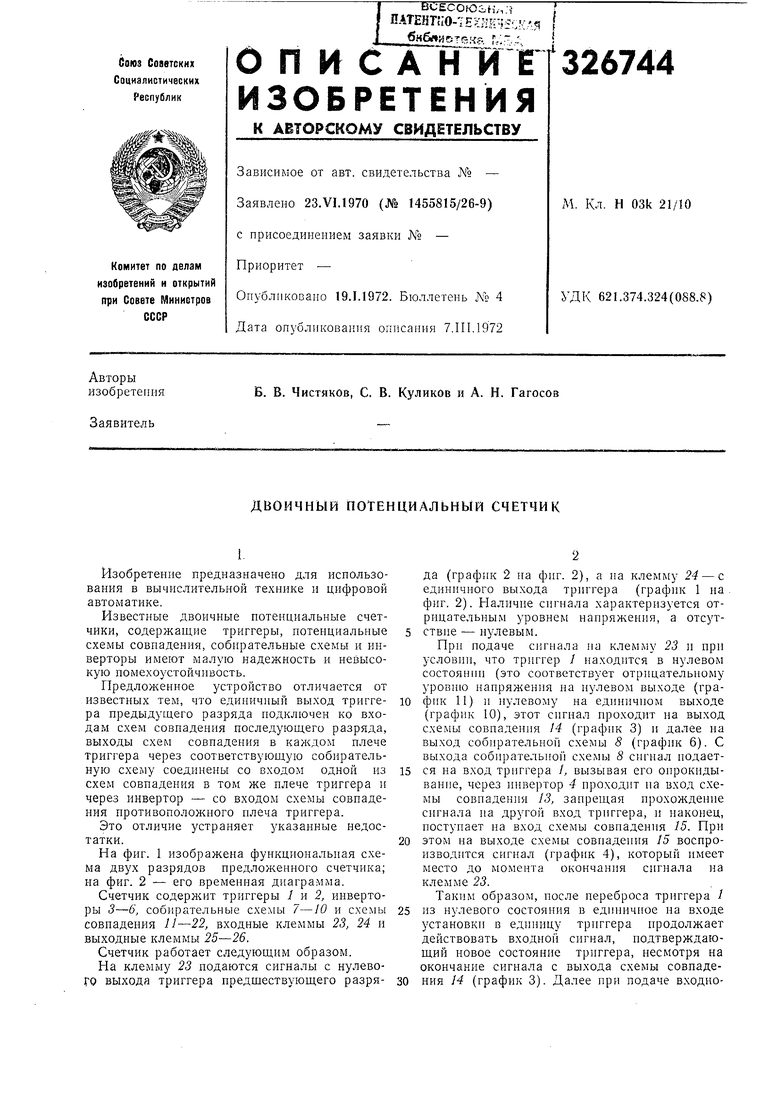

На фиг. 1 изображена функциональная схема двух разрядов предложенного счетчика; на фиг. 2 - его временная диаграмма.

Счетчик содерл ит триггеры 1 и 2, инверторы 3-6, собирательные схел1ы 7-10 и схемы совпадения 11-22, входные клеммы 23, 24 и выходные клеммы 25-26.

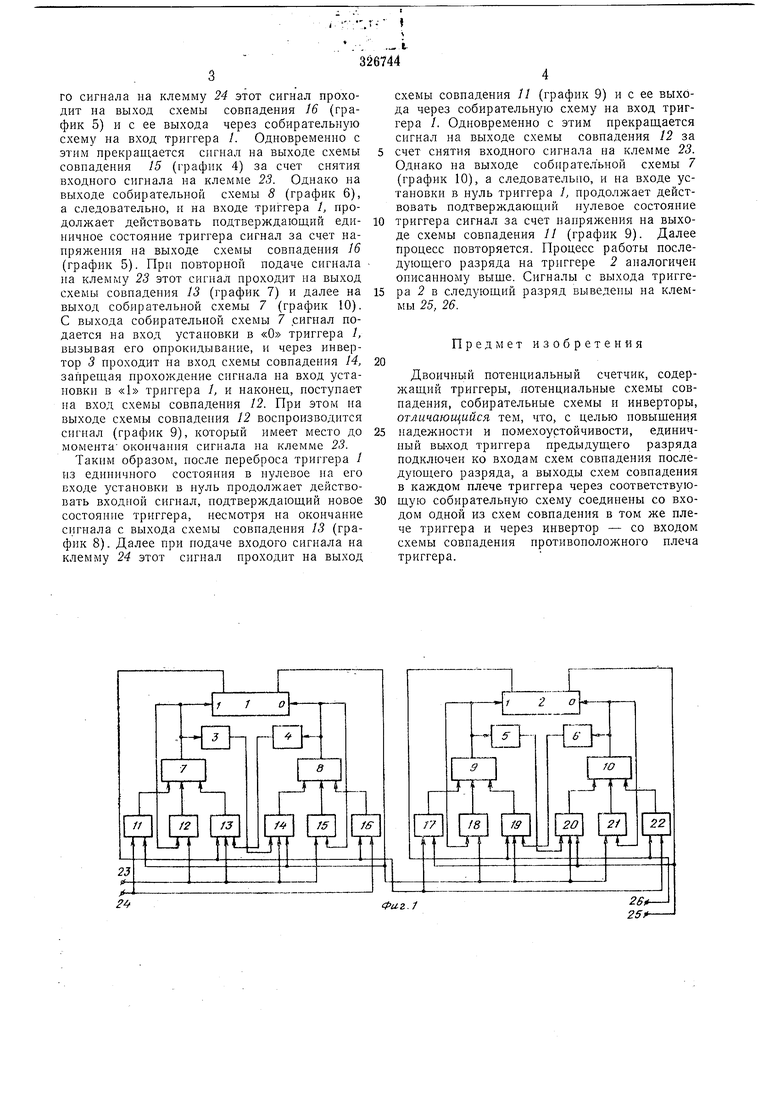

да (график 2 на фнг. 2), а на клемму 24 - с единичного выхода триггера (график 1 на . фиг. 2). Наличие сигнала характеризуется отрицательным уровнем напряжения, а отсут5 ствне - нулевым.

Прн подаче сигнала на клемму 23 и при условии, что триггер / находится в нулевом состоянии (это соответствует отрицательному уровню нанрялгеиия на нулевом выходе (гра0 фпк 11) и нулевому на единичном выходе (график 10), этот сигнал проходит на выход схемы совпадения 14 (график 3) и далее на выход соб 1рательной схемы 8 (график 6). С выхода собирательной схемы 8 сигнал подается на вход триггера /, вызывая его онрокидыванне, через инвертор 4 проходит на вход схемы совиадения 13, запрещая ирохождение сигнала на другой вход триггера, и наконец, ностунает на вход схемы совиадения 15. При

0 этом на выходе схемы совпадения 15 воспроизводится сигнал (график 4), который имеет место до момента окончания сигнала на клемме 23. Таким образом, после переброса триггера 1

5 из нулевого состояния в еднннчпое на входе установкн в единицу триггера продолжает действовать входной сигнал, подтверждающий новое состояние триггера, несмотря на окончание сигнала с выхода схемы совпадего сигнала на клемму 24 этот сигнал проходит на выход схемы совпадения 16 (график 5) и с ее выхода через собирательную схему на вход триггера /. Одновременно с этим прекращается сигнал на выходе схемы совиадения 15 (график 4) за счет снятия входного сигнала на клемме 23. Однако на выходе собирательной схемы 8 (график 6), а следовательно, и на входе триггера 1, продолжает действовать подтверждающий единичное состояние триггера сигнал за счет напряжения на выходе схемы совпадения 16 (график 5). При повторной иодаче сигнала на клемму 23 этот сигнал ироходит на выход схемы совпадения 13 (график 7) и далее на выход собирательной схемы 7 (график 10). С выхода собирательной схемы 7 сигнал подается на вход установки в «О триггера 1, вызывая его опрокидывание, и через инвертор 3 проходит на вход схемы совпадения 14, запрещая прохождение сигнала на вход установки в «1 триггера /, и наконец, поступает на вход схемы совпадения 12. При этом на выходе схемы совпадения 12 воснроизводится сигнал (график 9), который имеет место до момента окончания сигнала на клемме 23.

Таким образом, после переброса триггера / из едииичиого состояиия в иулевое на его входе установки в нуль продолжает действовать входной сигнал, подтверждающий новое состояние триггера, несмотря на окончание сигнала с выхода схемы совиадения 13 (график 8). Далее при подаче входого сигнала на клемму 24 этот сигнал проходит на выход

схемы совпадения 11 (график 9) и с ее выхода через собирательную схему на вход триггера /. Одновременно с этим прекращается сигнал на выходе схемы совпадения 12 за

счет снятия входного сигнала на клемме 23. Однако на выходе собирательной схемы 7 (график 10), а следовательно, и на входе установки в нуль триггера Д продолжает действовать подтверждающий нулевое состояние

триггера сигнал за счет напряжения на выходе схемы совиадения 11 (график 9). Далее процесс повторяется. Процесс работы последующего разряда на триггере 2 аналогичен описанному выше. Сигналы с выхода триггера 2 в следующий разряд выведены на клеммы 25, 26.

Предмет изобретения

Двоичиый потенциальный счетчик, содержащий триггеры, потенциальные схемы совиадения, собирательные схемы и инверторы, отличающийся тем, что, с целью повышения надежности и помехоустойчивости, единичный вы-ход триггера предыдущего разряда подключен ко входам схем совпадения последуюи1,его разряда, а выходы схем совпадения Б каждом плече триггера через соответствующую собирательную схему соединены со входом одной из схем совпадения в том же плече триггера и через инвертор - со входом схемы совпадения противоположного плеча триггера.

fuz 2

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 1971 |

|

SU429538A1 |

| СЧЕТЧЙК ИМПУЛЬСОВ | 1971 |

|

SU294256A1 |

| Адаптивный аналого-цифровой преобразователь частотно-модулированных сигналов | 1972 |

|

SU443479A1 |

| Каскад программируемого делителя частоты | 1980 |

|

SU919091A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1971 |

|

SU293256A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ СУММАТОР | 1972 |

|

SU421007A1 |

| РЕВЕРСИВНЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК | 1971 |

|

SU304707A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР С ЗАПОМИНАЮЩИМ УСТРОЙСТВОМ НА МАГНИТНОМ БАРАБАНЕ | 1966 |

|

SU182414A1 |

| УСТРОЙСТВО для ВОСПРОИЗВЕДЕНИЯ ЗАПАЗДЫВАНИЯ РЕЛЕЙНЫХ ЭЛЕМЕНТОВ | 1971 |

|

SU302719A1 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1987 |

|

SU1462474A1 |

Даты

1972-01-01—Публикация