1

Ивобретввие относится ;к вычислмтельтюй теХНИ ке и может быть иополызоваио IB специализирова-нных вычислительных (машинах, например, IB цифровых системах программного yiHipавления движение м.

И ест н ы 2 дв о и Ч1Н о -д есятичН ы е сумма то р ы «а-ка-плишающего типа, lcoдeipжaш,:иe двоичнодесяти ч1ные декады, соединенные между собой переноса, цепью циклического переноса и имеющие внутри декад цепи 1кор;рекций, обладают о-пращиченньши функ|Циональными

В031МО ЖНОСТЯМИ.

В предлагаемый сумматор, с целью расширения фуекциойальных возможиостей, в каждую декаду дополнительно введены триггер и схемы совпадения, причем выходы линий заде|ржек каждой декады суммато1ра соединены непосредственно с первой группой схем совпадения, управляющие входы которых подключены к шипе сдвига влево, и через инверторы, за исключением выхода .младшего разряда каждой декады, ко второй группе схем сопадеНия, управляющие 1входы которых подключены к шине сдвига вп1раво, выходы первой Г|руппы схем союпадения соединены со входами одноименных двоичных разрядов данной декады сумматора, а выходы второй группы схем совпаде НИя соединены со (входами первых трех младших разрядов данной декады, выходы линий, задержек младших разрядов всех декад.

кроме первой, и з ако13ого разряда соединены со входами одной и через инвертор другой схем совпадения, входы которых подсоединены к шине сдвига вправо, а выходы, подключены соответственно к еди-ничному и нулевому входам триггера данного разряда, единичный выход которого .соединен со входами двух схем совпадения, вторые входы которых подключены к шине коррекции результата, а выходы соединены со входами первого и третьего ра13рядов предыдущей младшей декады, выход линии задержки младшего разряда калсюй декады сум1матора подключен через одну схему совпадения, другой вход которой соединен

с шиной сдвига вправо, инвертор и другую схему совпадения, управляющей вход которой соединен с шиной переноса младшей декады, к шине переноса собственной декады.

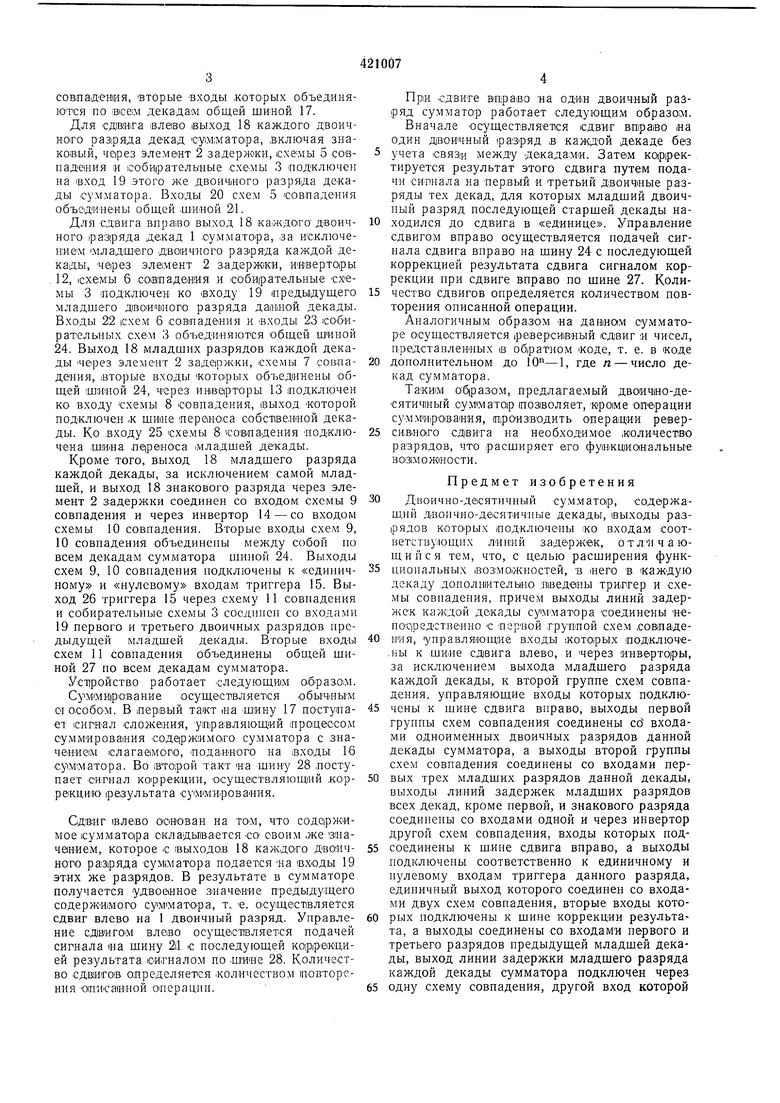

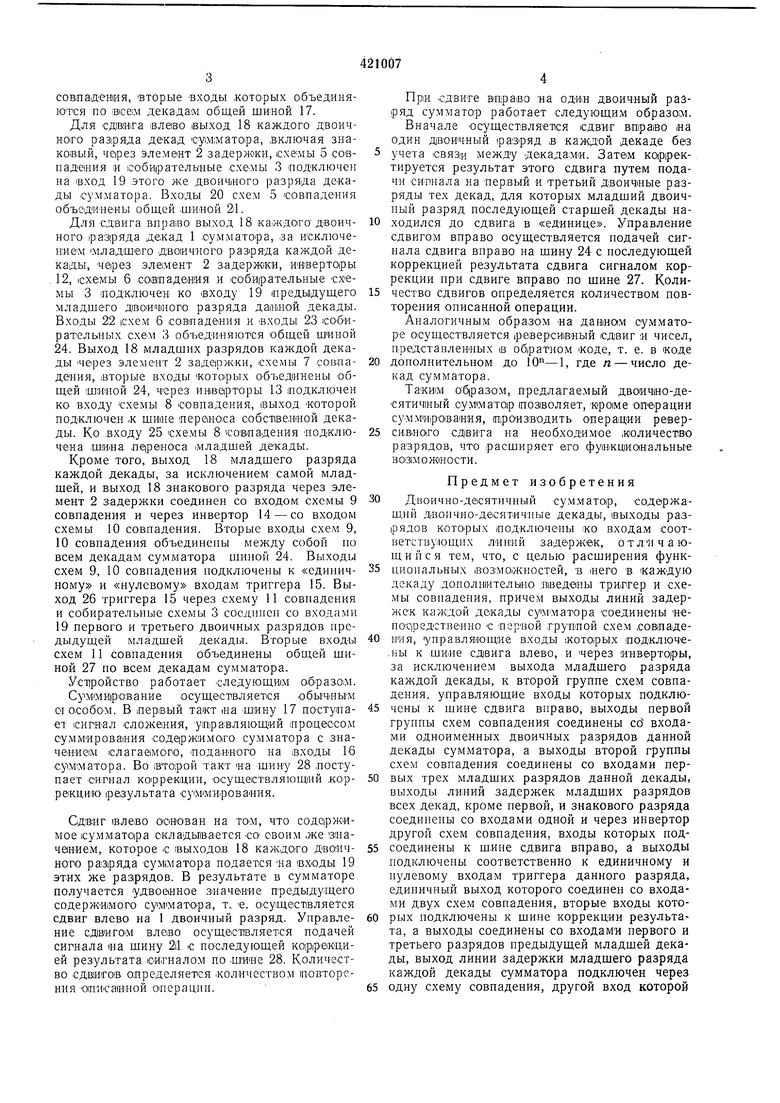

На чертеже представлена функциональная схема предлагаемого двоично-десятичного сумматора накапливающего типа, на котором можно осуществить реверсивный сдвиг.

Функциональная схема включает п двоичнодесятичных декад 1 сумматора с цепямд переноса и цепью циклического переноса, элементы 2 задержки, собирательные схемы 3, схемы 4-11 совпадения, инверторы 12-14 и триггеры 15с раздельными входами. Для осуществления суммирования служат входы 16 схем 4 совпадения, вторые входы .которых объединяются па BceiM декадам общей шиной 17. Для сдвига iB.ieiBo выход 18 каждого двоичного раз1ряда декад cyixiaiaTOipa, включая знаковый, чорез элемент 2 задермски, схемы 5 совпадешия и соби|рательные . 3 подключен на вход 19 этого же двои4|ного разряда декады .сумматора. Входы 20 схем 5 совпадения объединены общей .шииой 21. Для сдвига вправо выход 18 каждого двоичного |ра:з1ряда де:кад 1 ,оуммато|ра, за исключением младшего двоич-ного разряда каждой декады, -через элемент 2 задержки, инверторы , 12, юхемы 6 .еоипа.дения и соби|рательные схемы 3 подключен ко входу 19 предыдущего младшего двоичаю го разряда дайной декады. Входы 22 схем 6 совпадения и входы 23 собирательных схем 3 объеди-няются общей щиной 24. Выход 18 младщих разрядов каждой декады i4epe3 элемент 2 заде|ржки, схемы 7 сов.надеиия, .вторые входы |кото1рых объединены общей шипой 24, через инверторы 13 подключен ко входу схемы 8 совиадения, выход -которой подключен ,к mmie nepemoca собст1ве.Н1Ной декады. Ко входу 25 схемы 8 совпадения подключена .шипа .neipeiHOca младшей декады. Кроме того, выход 18 младшего разряда каждой декады, за исключением самой младшей, и выход 18 знакового разряда через элемент 2 задержки соединен со входом схемы 9 совпадения и через инвертор 14 - со входом схемы 10 совпадения. Вторые входы схем 9, 10 совпадения объединены между собой по всем декадам сумматора шиной 24. Выходы схем 9, 10 совпадения подключены к «единичному и «нулевому входам триггера 15. Выход 26 триггера 15 через схему 11 совпадения и собирательные схемы 3 соединен со входами 19 первого и третьего двоичных разрядов предыдущей младшей декады. Вторые входы схем 11 совпадения объединены общей шиной 27 по всем декадам сумматора. Услройство работает .следую.ши1М образом. Суммирование осущес-пвляется обычным отособОМ. В лервый такт 1на шину 17 поступа€1 сигн-ал сложения, управляющий процессом суммироваиия со.де|рж:имаго сумматора с .значением слагаемОГО, пода.нпого на входы 16 су1м;матора. Во второй та.кт па шину 28 поступает сигнал коррекции, осуществляющиш .коррекцию |результата сумвдировапия. Сдвиг 1влево основан на тОМ, что содаржимое сумматора складывается со своим ,же 31начанием, которое с выходов 18 каждого двоичного разряда сулиматора подается -на входы 19 этих же разрядов. В результате в сумматоре получается удвоенное значение предыдущего содержи1мого сумматора, т., е. осуществляется сдвиг влево на 1 двоичный разряд. Управление сдвигОМ влево осущест1вляется подачей сигнала иа шину 2il с последуюшей коррекцией результата сигналом по шице 28. Количество сдвигов опре.деляется .количеством повторения описаеной операции. 5 10 15 20 25 30 35 40 45 50 55 60 65 При сдвиге вправо :на один двоичный разряд сумматор работает следующим образо1М. Вначале осу.ществля-епся сдвиг вправо на один двоичный разряд в каждой декаде без учета связи между декада:М1И. Затем KOippeKтируется результат этого сдвига путем подачи сигнала на первый и третьий двоичные разряды тех декад, для которых младщий двоичный разряд последующей старшей декады находился до сдвига в «единице. Управление сдвигом вправо осуществляется подачей сигнала сдвига вправо на шину 24 с последующей коррекцией результата сдвига сигналом коррекции при сдвиге вправо по шине 27. Количество сдвигов определяется количеством повторения онисанной операции. Аналогичным обра.зом -на .даняом сумматоре осуществляется реверсивный сдвиг и чисел, представленпых в обратном «оде, т. е. в «оде дополнительном до , где п - число декад су.мматора. ТаКИ1м об|разом, предлагаемый двоичио-деСЯТИЧ1НЫЙ сум1мато|р 1поз воляет, кроме операции суммирования, производить операции реверси.впого сдвига на необходимое количество разрядов, что расширяет его функцисинальные ВОЗ|МОЖ1НОСТИ. Предмет изобретения Двоично-десятичный сумматор, содержаш,ий двоично-десятичные декады, выходы разрядов которых подключены ;ко входам соответствующих линий задержек, отличающийся тем, что, с целью расширения функцнональных воз можностей, в «его в каждую де.каду дополнителыно введены и схемы совиадения, причем выходы линий задержек каждой декады сум-матора соединены непосредственно с пгрвой группой схем .совладения, управляющие входы жоторых оодключ-е-ны к шине сдвига влево, и через инверто(ры, за исключением выхода младшего разряда каждой декады, к второй группе, схем совпадения, управляюшие входы которых нодключены к шине сдвига вправо, выходы первой группы схем совпадения соединены cd входам.и одноименных двоичных разрядов данной декады сумматора, а выходы второй группы схем совпадения соединены со входами первых трех младших разрядов данной декады, выходы линий задержек младших разрядов всех декад, кроме первой, и знакового разряда соединены со входами одной и через инвертор другой схем совпадения, входы которых подсоединены к ш.ине сдвига вправо, а выходы подключены соответственно к единичному и нулевому входам триггера данного разряда, единичный выход которого соединен со входами двух схем совпадения, вторые входы которых подключены к шине коррекции результата, а выходы соединены со входами первого и третьего разрядов предыдущей младшей декады, выход линии задержки младшего разряда каждой декады сумматора подключен через одну схему совпадения, другой вход которой 5 соединен с шиной сдвига вправо, инвертор и другую схему совпадения, управляющий вход 6 которой соединен с шиной переноса младшей декады, к шине переноса собственной декады.

| название | год | авторы | номер документа |

|---|---|---|---|

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| Двоичный сумматор накапливающего типа | 1971 |

|

SU455340A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| ОДНОАДРЕСНАЯ УНИВЕРСАЛЬНАЯ ЭЛЕКТРОННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1964 |

|

SU165595A1 |

| Устройство для сложения | 1973 |

|

SU488206A1 |

| Арифметическое устройство | 1978 |

|

SU711570A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU451078A1 |

| УСТРОЙСТВО для СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ | 1972 |

|

SU332459A1 |

| Арифметическое устройство | 2016 |

|

RU2632411C1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

Авторы

Даты

1974-03-25—Публикация

1972-03-28—Подача