Предлагаемое изобретение относится к преобразователем числа 1импульсов в двоичный КОД для cwcTeiM c6oipa, обработки и передачи информации.

Известны преобразователи числа импульсов в двоичный код на феррит-транзисторных ячейках, состоящие из ряда последовательных блоков преобразования, каждый из которых содержит транзистор, конденсатор связи, включенный между эмиттером транзистора и заземленным полюсом источника питания, основной трансформатор на сердечнике с прямоугольной петлей гистерезиса, в котором обмотка перемагничивания в состоянм:и «О включена между коллектором транзистора и вторым полюсом источника питания, обмотка перемагничивания в состоянии «1 включена в эмиттерную цепь транзистора последовательно с рез1истором нагрузк1и предькдущего блока, а обмотки считывания информации во всех блоках соединены последовательно и подключены к блоку управления, и вспомогательный трансформатор на аналогичном сердечнике, в котором первичная обмотка включена последовательно с обмоткой перемагничивашш основного сердечника в состояние «О, а вторичная - в базовую цепь транзистора последовательно и встречно с обмоткой управления транзистором основного сердечника, не исключают разрушение информации при считывании.

С целью исключения -разрушения информации при считывании в предлагаемый преобразователь числа импульсов в двоичный код на феррит-транзисторных ячейках содержит дополнительно блок управления дву.хпозшционным ключол и диоды, причем в каждом блоке преобразования обмотка иоложительной обратной связи включена эмиттером транзистора и заземленным полюсом источника питания последовательно с обмоткой перемагничмвания сердечника следующего блока в состояние «I, первым диодом и одним из контактов ключа блока управления, а обмотка восстановления информации включена между резистором нагрузки и заземленным полюсом источника питан.ия последовательно со нторым диодом и другими контактами указанного ключа.

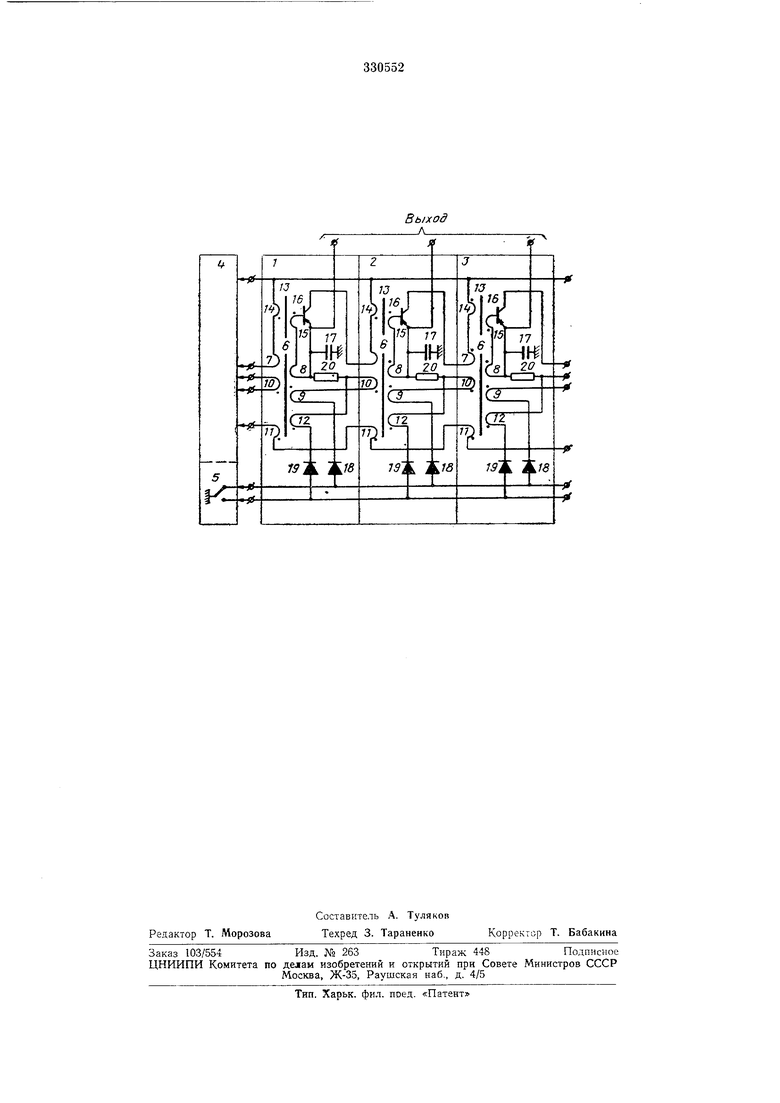

На чертенке показана схема предлагаемого преобразователя числа импульсов в двоичный код на феррит-транзисторны.х ячейка.х.

Предлагаемый преобразователь состоит лз последовательных блоков для преобразования числа г мпульсов в двоичный код /, 2, .3, блока управления 4. ключа 5 с переключающимися контактами, трансформатора 6 с обмотками 7-12. трансформатора 13 с обмотками 14 и }5, транзистора 16, конденсатора

связи 17, диодов 18 и 19 и резистора нагрузки 20.

Предлагаемое устройство работает следующим образом.

Преобразование числа входиых импульсов в двоичный код производится при исходном положении ключа 5. При отпирании транзистора 16 блока 1 конденсатор 17 заряжается, причем ток зарядки проходит по обмотке 7 трансформатора 6 и обмотке 14 трансформатора 13 блока 2. Сердечник трансформатора 6 перемагничивается в состояние «О, а трансформатора 13 - в состоянне «1. Ориентация обмоток 7 и у трансформатора 6 и обмоток 14 и .15 у трансформатора J3 обеспечивает вычитание наводимых в них сигналов. При равенстве числа внтков об моток 7 и 5 у трансформатора 6 и обмоток 14 и 15 у трансформатора J3 достигается полное подавление сигнала помехи в базовой цепи транзистора.

По мере зарядки конденсатора начинает протекать ток по обмотке 10 трансформатора 6 блока 2, а по мере зарядки конденсатора направление намагниченности трансформатора 6 блока 2 .изменяется. Транзистор блока остается запертым, выходной сигнал блоком 2 не формируется. После завершения перемагничивания сердечника трансформатора 6 блока У конденсатор /7 разряжается через резистор 20 и обмотку 10, обеспечива1Я плавное уменьшение тока перемагничивания сердечника трансформатора 6 блока 2 в состояние «1.

При поступлении следующего имнульса от блока / ток зарядки конденсатора в обмотке

7трансформатора 6 блока 2 вызывает перемагничивание сердечника в состояние «О.

8обмотке § трансформатора 6 наводится э. д. с., отпирающая транзистор 16 блока 2. Конденсатор 17 блока 2, заря1жаясь, подготавливает к работе блок 3. По мере зарядки конденсатора начинает протекать ток в обАготке 9 блока 2, создавая положительную обратную связь и обеспечивая энергию для полного неремагничивания сердечника трансфор матора 6 в состояние «О. После завершения перемагничивания сердечника трансформатора 6 блока 2 ток разрядки конденсатора блока 2 проходит по обмотке 9, блокируя воздействие тока в обмотке 10 при разрядке конденсатора блока /. В рассматриваемом режиме цепи обмоток 12 разомкнуты.

Таким образом, на каждые два сигнала от блока 1 на вьгходе блока 2 формируется один сигнал. Аналогично работают и остальные блоки преобразователя.

Для считывания записанного када без разрушения информации ключ 5 нереводится во второе положение. В обмотку // подается

сигнал считывания-перемагничивания сердечников трансформатора 6 в состояние «О, длительность которого меньше выходного сигнала любого блока. Выходные сигналы

формируются блоками, сердечники которых к моменту поступления сигналов считывания перемагничены в состояние «1. После исчезиовения сигнала считывания конденсаторы /7 в блоках, на выходе которых формировался импульс, разрявжаются через замкнувшийся контакт ключа 5, диад 19, обмотку 12 и резистор 20. Ток в обмотке 12 обеспечивает восстановление считанной информации, т. е. перемагиичивает сердечник трансфор.матора 6

в состояние «1. Для продолжения счета входных сигналов ключ 5 возвращается в исходное полоукение.

Предмет и з о б р

теп и я

20

Преобразователь числа и.мпульсов в двоичный код на феррит-транзисторных ячейках, состоящий из ряда последрвательнь х блоков преобразования, каждый из которых содер1жит транзистор, конденсатор связи, включенный между эмиттером транзистора и заземленным полюсом источника питания, основной трансформатор на сердечннке с прямоугольной петлей гистерезиса, в котором

0 обмотка перемагничивания в состоянии «О включена между коллектором транзистора и вторым полюсом источника питания, обмотка перемагничивания в состояние «1 включена в эмиттерную цепь транзистора гюследова5тельно с резистором нагрузки предыдун1,его блока, а обмотки считывания информации во всех блоках соединены носледовательно л по(дключены к блоку управлепия, и вспомогательный трансформатор на аналогичном

0 сердечннке, в котором первичная обмотка включена последовательно с обмоткой неремагничивания основного сердечника в состояние «О, а вторичная - в базовую цепь транзистора последовательно и встречно с обмот5кой управления транзистором основного сердечника, отличающийся тем, что, с целью исключения разрушения информации при считывании, он содерл ит донолнительно блок управления двухпозиционным ключом и дио0ды, причем в каждом блоке преобразования обмотка положительной обратной связи включена между эмиттером транзистора и заземленным полюсом источника питания последовательно с обмоткой перемагничивания сер5дечника следующего блока в состояние «1, первьгм диодом и одним из контактов ключа блока управления, а обмотка восстановления информации включена- между резистором нагрузки и заземленным полюсам источника

0 питания последовательно со вторым диодом и другим контактом указанного ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИМПУЛЬСНО-ФАЗОВОГО УПРАВЛЕНИЯ т-ФАЗНЫМ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1969 |

|

SU436429A1 |

| Счетчик ватт-часов | 1971 |

|

SU437018A1 |

| ФЕРРИТ-ТРАНЗИСТОРНЫЙ ТРИГГЕР СО СЧЕТНЫМ ВХОДОМ | 1973 |

|

SU409355A1 |

| Устройство для выбора адресов | 1976 |

|

SU577563A1 |

| ТРИГГЕР С НЕРАЗРУШАЕМОЙ ПРИ ОТКЛЮЧЕНИИ ИНФОРМАЦИЕЙ | 1990 |

|

RU2017328C1 |

| ТРИГГЕР С ВОССТАНОВЛЕНИЕМ УТРАЧЕННОГО ПРИ ОТКЛЮЧЕНИИ СОСТОЯНИЯ | 1995 |

|

RU2099861C1 |

| РЕГИСТР СДВИГА | 1973 |

|

SU364029A1 |

| БЛОКИНГ-ГЕНЕРАТОР | 1990 |

|

RU2028720C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1992 |

|

RU2030094C1 |

| ДВУХТАКТНЫЙ РАСПРЕДЕЛИТЕЛЬ | 1971 |

|

SU312372A1 |

Даты

1972-01-01—Публикация