Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известен триггер [1] , содержащий статический триггер, выполненный на логических элементах, два магнитных сердечника с прямоугольной петлей гистерезиса, управляющие обмотки которых включены в соответствующие плечи триггера. Подмагничивающая обмотка каждого сердечника включена последовательно с управляющей обмоткой другого сердечника. Входы логических элементов, соединенные с управляющими обмотками, через резистор подключены к источнику питания, а выходы логических элементов соединены с источником питания через соответствующие диоды.

Недостатком данного триггера является отсутствие возможности работы в счетном режиме, что затрудняет построение на его основе счетных устройств. Другим недостатком триггера является его низкая информационная емкость, так как он может хранить только один бит информации. Третьим недостатком триггера является большое потребление мощности в режиме хранения информации, так как намагничивающий ток через обмотки сердечников в этом режиме не прекращается.

Известна энергонезависимая ячейка памяти [2], содержащая сердечник с прямоугольной петлей гистерезиса и обмоткой, средняя точка которой подключена через резистор к источнику питания, конец обмотки подключен к выходу первого элемента И-НЕ, начало - к выходу второго элемента И-НЕ и к одному из входов третьего элемента И-НЕ, второй вход которого подключен к шине разрешения, а выход - к единичному входу триггера, нулевой вход которого подключен к шине сброса, счетный вход - к информационной шине, а прямой и инверсный выходы - к первым входам соответственно первого и второго элементов И-НЕ, вторые входы которых подключены к шине перемагничивания.

Недостатком данной энергонезависимой ячейки памяти является низкая информационная емкость, так как данная ячейка памяти может хранить только один бит информации. Это затрудняет построение на ее основе многоканальных счетных устройств. Другим недостатком данной ячейки памяти является низкая помехоустойчивость, так как счетный триггер, входящий в ее состав, чувствителен к помехам на информационной шине, а инерционность сердечника для подавления указанных помех не используется. Третьим недостатком данной ячейки памяти является большой ток перемагничивания сердечника, так как в перемагничивании участвует лишь половина витков обмотки.

Достигаемым техническим результатом является расширение функциональных возможностей энергонезависимой ячейки памяти путем увеличения ее информационной емкости, а также повышение ее помехоустойчивости и экономичности.

Указанный технический результат достигается тем, что в энергонезависимую ячейку памяти, содержащую магнитный сердечник с прямоугольной петлей гистерезиса, первый вывод обмотки которого подключен к выходу первого логического элемента, триггер, нулевой вход которого подключен к шине сброса, инверсный выход - к одному входу второго логического элемента, выход которого соединен с входом третьего логического элемента, резистор, один из выводов которого подключен к шине питания, информационную шину и шину перемагничивания, введены N магнитных сердечников с прямоугольной петлей гистерезиса и обмоткой каждый, блок коммутации, адресные шины, n-p-n-транзистор и диод, анод которого соединен с эмиттером транзистора и с первыми выводами обмоток сердечников, вторые выводы которых соединены с соответствующими информационными выводами блока коммутации, адресные входы которого соединены с соответствующими адресными шинами, управляющий вход - с шиной перемагничивания, общий информационный вывод - с входом и выходом соответственно первого и третьего логических элементов, а выход - с катодом диода и базой транзистора, коллектор которого соединен с другим выводом резистора и единичным входом триггера, при этом информационная шина соединена с другим входом второго логического элемента, триггер выполнен в виде асинхронного RS-триггера, первый и третий логические элементы - в виде инверторов, а второй логический элемент - в виде элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

Блок коммутации содержит шину ускоренного перемагничивания, двунаправленный ключ, мультиплексор и резистор, один вывод которого является общим информационным выводом блока коммутации, а другой вывод соединен с общим информационным входом мультиплексора и с первым информационным входом двунаправленного ключа, второй информационный вход которого является выходом блока коммутации, а управляющий вход соединен с шиной ускоренного перемагничивания, при этом информационные входы мультиплексора являются соответствующими информационными входами блока коммутации, адресные входы - соответствующими адресными входами блока коммутации, а управляющий вход - управляющим входом блока коммутации.

Указанная совокупность признаков позволяет расширить функциональные возможности энергонезависимой ячейки памяти путем увеличения ее информационной емкости. Запись и неразрушающее считывание информации в любом выбранном сердечнике производятся независимо от информации, хранящейся в других сердечниках. При этом за счет использования инерционности сердечников и шунтирования выбранного сердечника p-n-переходом транзистора или диода повышена помехоустойчивость энергонезависимой ячейки памяти в счетном режиме работы. Двунаправленный ключ блока коммутации позволяет осуществлять ускоренное перемагничивание выбранного сердечника за счет отключения от него шунтирующих элементов.

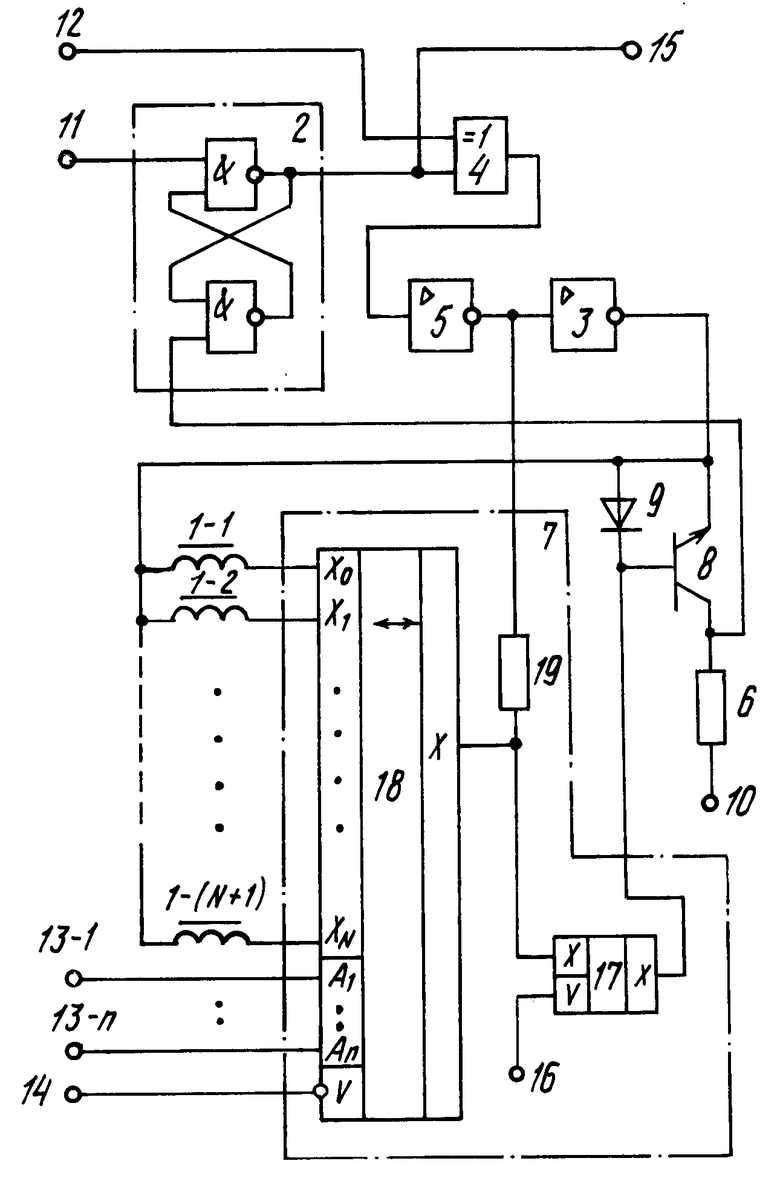

На чертеже приведена схема энергонезависимой ячейки памяти.

Энергонезависимая ячейка памяти содержит основной 1-1 и N дополнительных 1-2, ..., 1-(N+1) сердечников с прямоугольной петлей гистерезиса и обмоткой, триггер 2, первый 3, второй 4 и третий 5 логические элементы, резистор 6, блок 7 коммутации, транзистор 8, диод 9, шину 10 питания, шину 11 сброса, информационную шину 12, n адресных шин 13-1, ..., 14-n, (n связано с N соотношением N ≅ 2n-1), шину 14 перемагничивания и выходную шину 15. Первые входы обмоток сердечников 1-1, 1-2, ..., 1-(N+1) подключены к выходу первого логического элемента 3. Нулевой вход триггера 2 подключен к шине 11 сброса, инверсный выход - к выходной шине 15 и одному входу второго логического элемента 4, выход которого соединен с входом третьего логического элемента 5. Единичный вход триггера 2 соединен с коллектором транзистора 8 и через резистор 6 с шиной 10 питания. Анод диода 9 соединен с эмиттером транзистора 8 и с первыми выводами обмоток сердечников 1-1, 1-2, ..., 1-(N+1), вторые выводы которых соединены с соответствующими информационными выводами блока 7 коммутации. Адресные входы блока 7 коммутации соединены с соответствующими адресными шинами 13-1, ..., 13-n, управляющий вход - с шиной 14 перемагничивания, общий информационный вывод - с входом и выходом соответственно первого 3 и третьего 5 логических элементов, а выход - с катодом диода 9 и базой транзистора 8. Информационная шина 12 соединена с другим входом второго логического элемента 4. Триггер 2 выполнен в виде асинхронного RS-триггера (на элементах И-НЕ), первый 3 и третий 5 логические элементы - в виде инверторов, а второй логический элемент 4 - в виде элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

Блок 7 коммутации содержит шину 16 ускоренного перемагничивания, двунаправленный ключ 17, мультиплексор 18 и резистор 19. Один вывод резистора 19 является общим информационным выводом блока 7 коммутации, а другой вывод соединен с общим информационным входом мультиплексора 19 и с первым информационным входом двунаправленного ключа 17, второй информационный вход которого является выходом блока 7 коммутации, а управляющий вход соединен с шиной 16 ускоренного перемагничивания. Информационные входы мультиплексора 18 являются соответствующими информационными входами блока 7 коммутации, адресные входы - соответствующими адресными входами блока коммутации, а управляющий вход - управляющим входом блока коммутации.

Энергонезависимая ячейка памяти работает следующим образом.

В режиме хранения информации триггер 2 удерживается в нулевом состоянии потенциалом низкого уровня, поступающим по шине 11 сброса, мультиплексор 18 закрыт, так как сигнал на шине 14 перемагничивания отсутствует, обмотки сердечников 1-1, 1-2, ..., 1-(N+1) обесточены.

Обнуление ячейки памяти производится следующим образом. На шину 14 перемагничивания подается сигнал низкого уровня, на шине 11 сброса сохраняется потенциал низкого уровня, на информационной шине 12 - потенциал высокого уровня, а на адресные шины 13-1, ..., 13-n последовательно выставляются коды адресов сердечников 1-1, 1-2, ..., 1-(N+1). При этом сердечники последовательно перемагничиваются в нулевое состояние током, протекающим с выхода инвертора 5 через резистор 19, мультиплексор 18, обмотку соответствующего сердечника 1-i (i = 1, 2, ..., N+1) на выход инвертора 3.

Сигнал ускоренного перемагничивания на шине 16 отсутствует, двунаправленный ключ 17 открыт, и через него обмотка сердечника 1-i шунтируется эмиттерным p-n-переходом транзистора 8, в результате чего процесс перемагничивания протекает медленно.

После обнуления ячейки памяти производится запись информации в сердечники 1-1, 1-2, ..., 1-(N+1). На шинах 11 и 14 удерживаются сигналы низкого уровня, на адресные шины выставляются коды адресов соответствующих сердечников, а на информационную шину 12 - сигнал низкого уровня для записи в сердечник 1-i логической "1" или сигнал высокого уровня для записи в сердечник 1-i логического "0". В первом случае сердечник 1-i перемагничивается током, протекающим с выхода инвертора 3 через обмотку сердечника 1-i, мультиплексор 18, резистор 19 на выход инвертора 5. Сигнал ускоренного перемагничивания на шине 16 отсутствует, двунаправленный ключ 17 открыт, и через него обмотка сердечника 1-i шунтируется p-n-переходом диода 9, в результате чего процесс перемагничивания протекает медленно. Во втором случае сердечник 1-i не перемагничивается, т.е. остается в состоянии логического "0", в которое был намагничен при обнулении.

Процессы обнуления и записи можно ускорить, закрыв двунаправленный ключ 17 потенциалом низкого уровня на шине 16 ускоренного перемагничивания и отключив таким образом шунтирующие элементы (транзистор 8 и диод 9) от обмоток сердечников 1-1, 1-2, ..., 1-(N+1).

Считывание информации из сердечников 1-1, 1-2, ..., 1-(N+1) производится следующим образом.

Энергонезависимая ячейка памяти устанавливается в режим хранения. На адресные шины 13-1, ..., 13-n устанавливается код адреса сердечника 1-i, с которого будет считываться информация. На шину 14 перемагничивания подается потенциал низкого уровня, и сердечник 1-i начинает перемагничиваться в состояние логического "0" так же, как при обнулении. Напряжение, возникающее при этом на обмотке сердечника 1-i, через мультиплексор 18 и двунаправленный ключ 17 прикладывается к эмиттерному p-n-переходу транзистора 8, открывая его. На коллекторе транзистора 8 формируется импульс логического "0". Указанный импульс представляет собой короткую помеху от непрямоугольности петли гистерезиса, если в сердечнике 1-i записан логический "0", или более протяженный сигнал, если в сердечнике 1-i записана логическая "1". С задержкой, превышающей длительность помехи от непрямоугольности петли гистерезиса, но меньшей, чем время перемагничивания сердечника, на шину 11 сброса подается потенциал высокого уровня. Если в сердечнике 1-i записан логический "0", то импульс логического "0" на коллекторе транзистора 8 к этому моменту времени заканчивается и триггер 2 остается в нулевом состоянии. Если в сердечнике 1-i записана логическая "1", то импульсом логического "0" с коллектора транзистора 8 триггер 2 переключается в единичное состояние.

Таким образом, информация из сердечника 1-i переписывается в триггер 2. Если необходимо изменить информацию, записанную в сердечник 1-i, на противоположную, то можно после считывания указанной инфоpмации в триггер 2 подать импульс логического "0" на информационную шину 12. При этом сердечник 1-i перемагничивается в состояние, противоположное состоянию триггера 2, т. е. реализуется счетный режим работы ячейки памяти. Высокая помехоустойчивость ячейки памяти при ее работе в счетном режиме обеспечивается за счет увеличения длительности процесса перемагничивания сердечника 1-i путем шунтирования его обмотки p-n-переходом диода 9 или транзистора 8, а экономичность обеспечивается за счет использования для перемагничивания сердечника 1-i, всех витков его обмотки.

Изготовлен лабораторный макет энергонезависимой ячейки памяти. Испытания макета подтвердили работоспособность заявляемой ячейки и ее практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2036547C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 2002 |

|

RU2230427C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2034397C1 |

| СЧЕТЧИК ИМПУЛЬСОВ, СОХРАНЯЮЩИЙ ИНФОРМАЦИЮ ПРИ ПЕРЕРЫВАХ ПИТАНИЯ | 1991 |

|

RU2047271C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1780487A1 |

| СЧЕТНОЕ УСТРОЙСТВО | 1992 |

|

RU2040113C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207718C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207717C2 |

| ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2038692C1 |

Изобретение относится к импульсной технике. Сущность изобретения: энергонезависимая ячейка памяти содержит основной 1-1 и N дополнительных сердечников с прямоугольной петлей гистерезиса 1 = 2 ,..., 1 = (N+1) и обмоткой, триггер 2, логические элементы 3 - 5, резистор 6, блок 7 коммутации, транзистор 8, диод 9, шину 10 питания, шину 11 сброса, информационную шину 12, n адресных шин 13-1, ..., 13-n (n связано с N соотношением N ≅ 2n-1 ), шину 14 перемагничивания и выходную шину 15. 1 з.п. ф-лы, 1 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Энергонезависимая ячейка памяти | 1979 |

|

SU845287A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-02-27—Публикация

1992-12-07—Подача