Изобретение относится к области автоматики и вычислительной техники, а именно к устройствам кольцевых транзисторно-тиристорных счетчиков импульсов.

Известен ряд схем кольцевых транзисторнотиристорных счетчиков, в которых отсутствуют конденсаторы.

Однако такие схемы критичны к разнице времени включения (твкл-) и выключения (твыкл.) тиристоров. Это обусловлено управлением включением и выключением тиристоров через схему совпадения, управляемую выключаемым тиристором.

Вследствие того, что серийно выпускаемые тиристоры имеют твкл. твыкл-, включившийся тиристор блокирует выключение следующего прежде, чем тот выключится (например, для тиристоров 2У101 твкл- 1-;-3 мксек, Твыкл.25-г-70 мксек).

Кроме того, известные счетчики критичны к длительности входного имлульса tsx. При вх Твыкл- возможно продвижение «единицы (выключенного состояния тиристора) на несколько разрядов под действием одного входного импульса.

Известные счетчики не обеспечивают устойчивой работы при высоких температурах (отсюда больших токах утечки транзисторов), больших остаточных напряжениях и малых токах выключения тиристоров.

Цель изобретения - обеспечить устойчивую работу счетчика при разбросе параметров тиристоров и длительности входных импульсов, а также исключение тока в нагрузке и снижение

потенциала выключенного тиристора.

Для этого в каждом разряде счетчика управляющий электрод тиристора предыдущего разряда гальванически связан с анодом тиристора последующего разряда, а шунтирующий транзистор последующего разряда через схему совпадений соединен с анодом тиристора предыдущего разряда. Кроме того, управляющие электроды тиристоров предыдущих разрядов развязаны диодами от анодов тиристоров последующих разрядов.

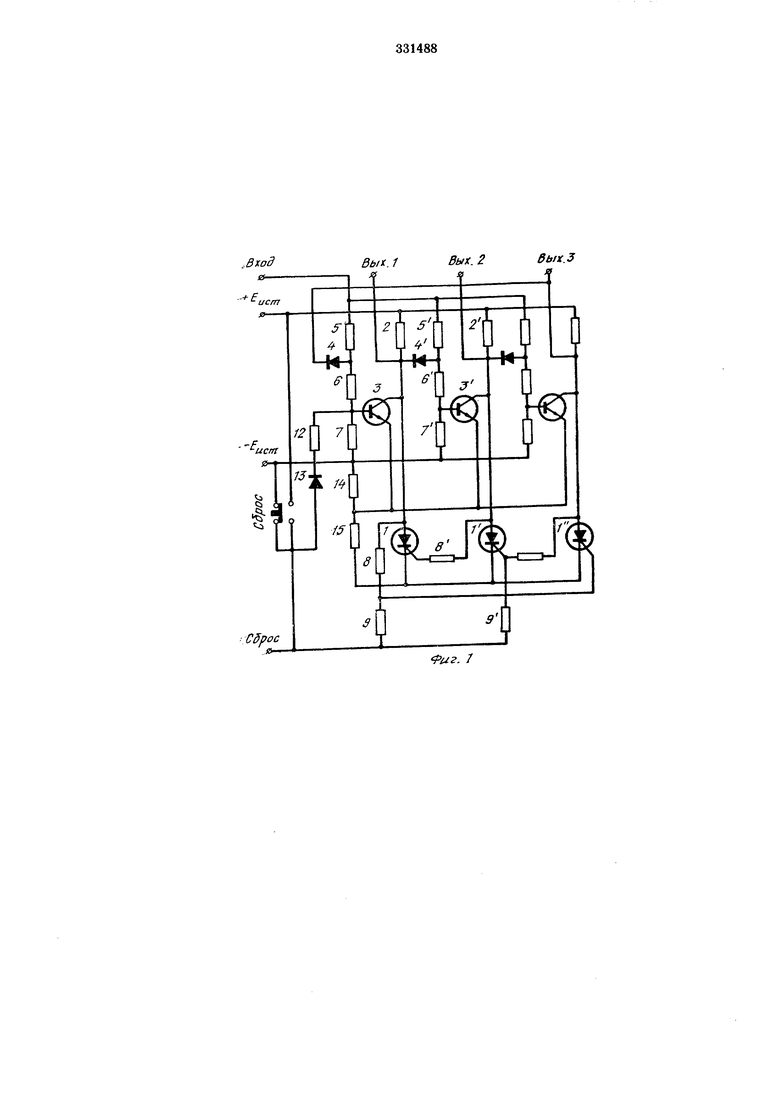

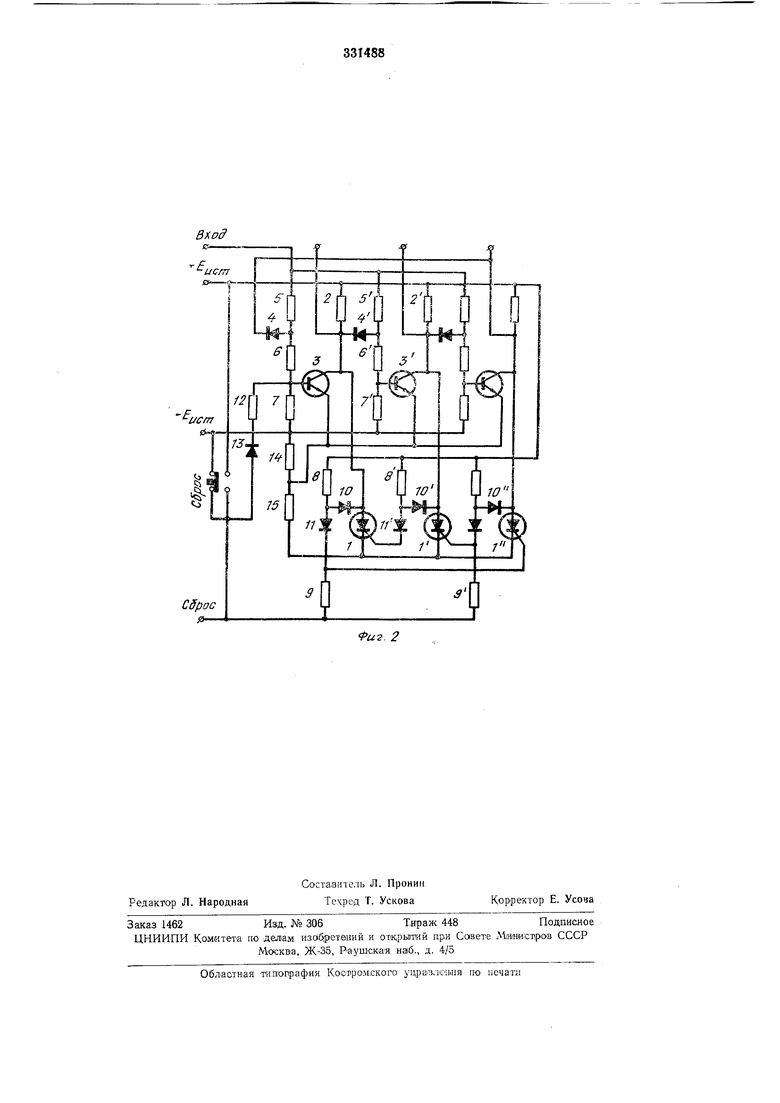

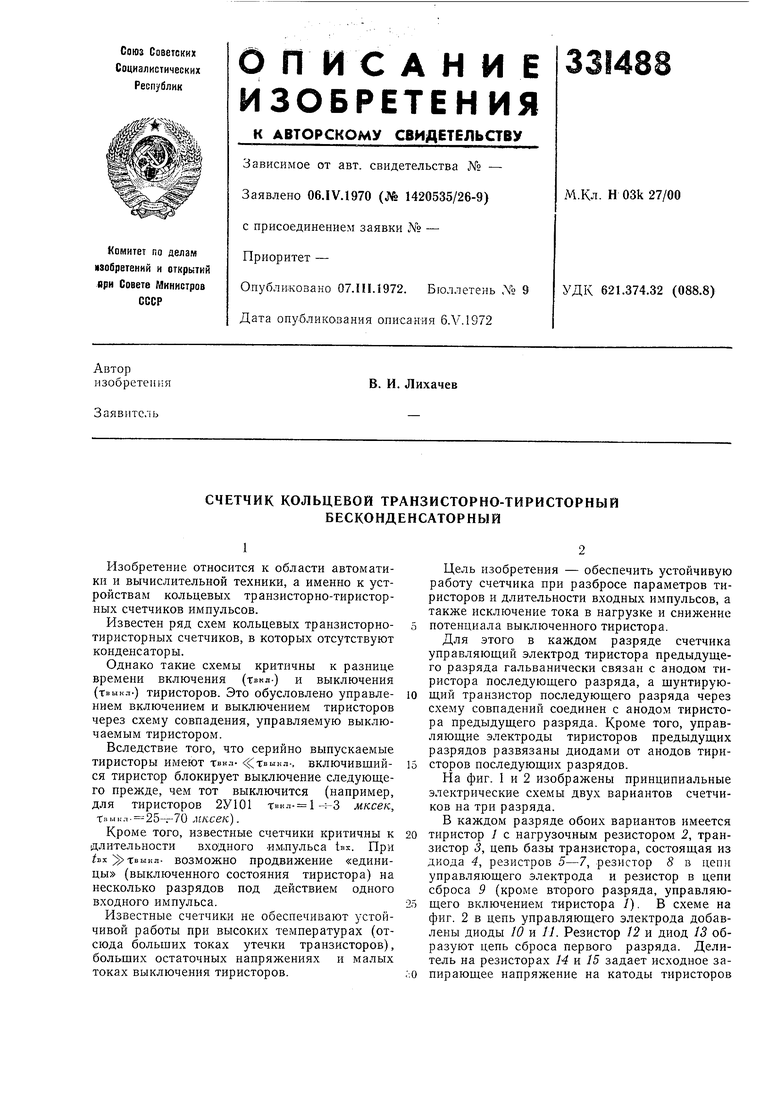

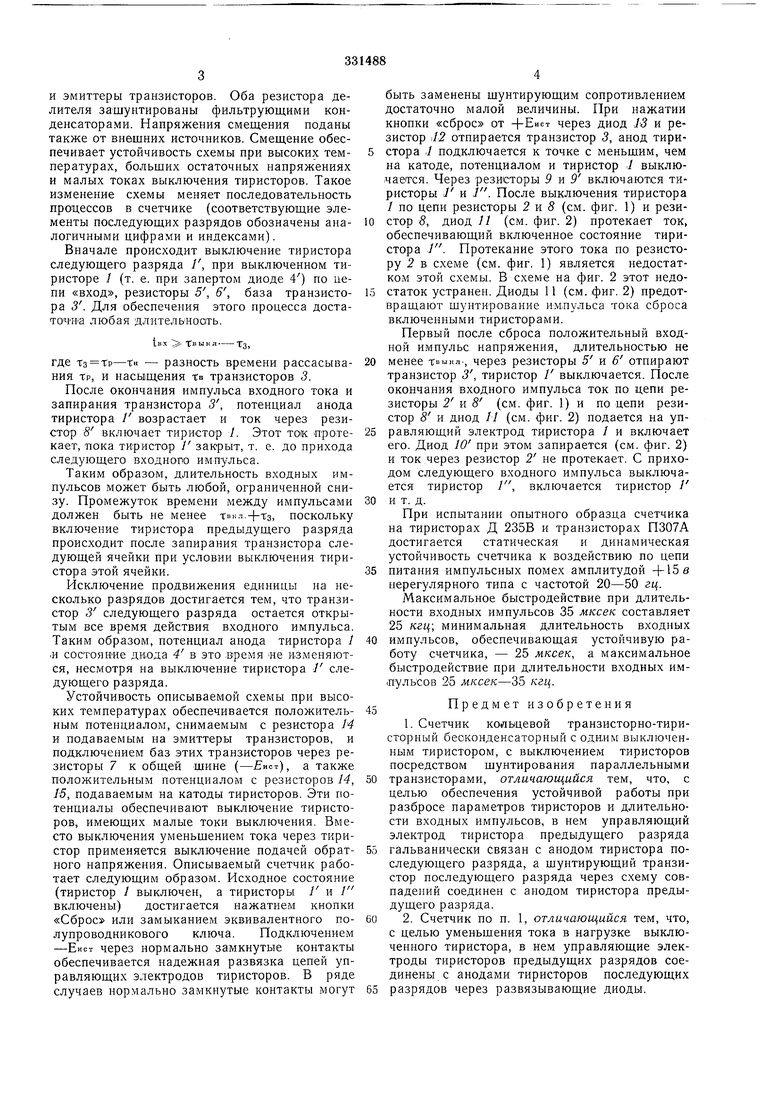

На фиг. I и 2 изображены принципиальные электрические схемы двух вариантов счетчиков на три разряда. В каждом разряде обоих вариантов имеется

тиристор } с нагрузочным резистором 2, транзистор 3, цепь базы транзистора, состоящая из диода 4, резистров 5-7, резистор 8 в цепи управляющего электрода и резистор в цепи сброса 9 (кроме второго разряда, управляющего включением тиристора )). В схеме на фиг. 2 в цепь управляющего электрода добавлены диоды 10 и 11. Резистор 12 и диод 13 образуют цепь сброса первого разряда. Делитель на резисторах 14 и 15 задает исходное заи эмиттеры транзисторов. Оба резистора делителя зашунтированы фильтрующими конденсаторами. Напряжения смещения ноданы также от внешних источников. Смещение обеспечивает устойчивость схемы при высоких температурах, больших остаточных напряжениях и малых токах выключения тиристоров. Такое изменение схемы меняет последовательность процессов в счетчике (соответствующие элементы последующих разрядов обозначены аналогичными цифрами и индексами).

Вначале происходит выключение тиристора следующего разряда Г, при выключенном тиристоре / (т. е. при запертом диоде 4) по иепи «вход, резисторы 5, 6, база транзистора 3. Для обеспечения этого процесса достаточна любая длительность.

LBX Твь1клТГ,

где ТЗ ТР-Гы - разность времени рассасывания ТР, и насыщения тгн транзисторов 3.

После окончания импульса входного тока и запирания транзистора 3, потенциал анода тиристора / возрастает и ток через резистор 8 включает тиристор I. Этот ток протекает, тюка тиристор / закрыт, т. е. до прихода следующего входного импульса.

Таким образом, длительность входных импульсов может быть любой, ограниченной снизу. Промежуток времени между импульсами должен быть не менее .+тз, поскольку включение тиристора предыдущего разряда происходит после запирания транзистора следующей ячейки при условии выключения тиристора этой ячейки.

Исключение продвижения единицы на несколько разрядов достигается тем, что транзистор 3 следующего разряда остается открытым все время действия входного импульса. Таким образом, потенциал анода тиристора I .и состоянне 4 в это время «е изменяются, несмотря на выключение тиристора 1 следующего разряда.

Устойчивость описываемой схемы при высоких температурах обеспечивается положительным потенциалом, снимаемым с резистора 14 и подаваемым на эмиттеры транзисторов, и подключением баз этих транзисторов через резисторы 7 к общей шине (-Яист), а также положительным потенциалом с резисторов 14, 16, подаваемым на катоды тиристоров. Эти потенциалы обеспечивают выключение тиристоров, имеющих малые токи выключения. Вместо выключения уменьшением тока через тиристор применяется выключение подачей обратного напряжения. Описываемый счетчик работает следующим образом. Исходное состояние (тиристор / выключен, а тиристоры 1 и / включены) достигается нажатием кнопки «Сброс или замыканием эквивалентного полупроводникового ключа. Подключением -ЕИСТ через нормально замкнутые контакты обеспечивается надежная развязка цепей управляющих электродов тиристоров. В ряде случаев нормально замкнутые контакты могут

быть заменены шунтирующим сопротивлением достаточно малой величины. При нажатии кнопки «сброс от +ЕИСТ через диод 13 и резистор ,12 отпирается транзистор 3, анод тиристора .1 подключается к точке с меньшим, чем на катоде, потенциалом и тиристор I выключается. Через резисторы 9 и 9 включаются тиристоры 1 и .1. После выключения тиристора / по цепи резисторы 2 и 8 (см. фиг. 1) и резистор 8, диод 11 (см. фиг. 2) протекает ток, обеспечивающий включенное состояние тиристора 1. Протекание этого тока по резистору .2 в схеме (см. фиг. 1) является недостатко.м этой схемы. В схеме на фиг. 2 этот недостаток устранен. Диоды 11 (см. фиг. 2) предотвращают шунтирование имлульса тока сброса включенными тиристорами.

Первый после сброса положительный входной импульс напряжения, длительностью не

менее -гвыкл-, через резисторы 5 и 6 отпирают транзистор 3, тиристор / выключается. После окончания входного импульса ток по цепи резисторы 2 и 8 (см. фиг. 1) и по цепи резистор 8 и диод 11 (см. фиг. 2) подается на управляющий электрод тиристора / и включает его. Диод W при этом запирается (см. фиг. 2) и ток через резистор 2 не протекает. С приходом следующего входного импульса выключается тиристор /, включается тиристор /

и т. д.

При испытании опытного образца счетчика на тиристорах Д 235В и транзисторах П307А достигается статическая и динамическая устойчивость счетчика к воздействию по цепи

питания импульсных помех амплитудой в нерегулярного типа с частотой 20-50 гц.

Максимальное быстродействие при длительности входных импульсов 35 мксек составляет 25 кгц; минимальная длительность входных

импульсов, обеспечивающая устойчивую работу счетчика, - 25 мксек, а максимальное быстродействие при длительности входных имлульсов 26 мксек-35 кгц.

Пред мет изобретения

1. Счетчик кольцевой транзисторно-тиристорный беоконденсаторный с одним выключенным тиристором, с выключением тиристоров посредством шунтирования параллельными

транзисторами, отличающийся тем, что, с целью обеспечения устойчивой работы при разбросе параметров тиристоров и длительности входных импульсов, в нем управляющий электрод тиристора предыдущего разряда

гальванически связан с анодом тиристора последующего разряда, а шунтирующий транзистор последующего разряда через с.хему совпадений соединен с анодом тиристора предыдущего разряда.

2. Счетчик по п. 1, отличающийся тем, что, с целью уменьшения тока в нагрузке выключенного тиристора, в нем управляющие электроды тиристоров предыдущих разрядов соединены с анодами тиристоров последующих

.Вход

С5рос

Вы к. 2

бых.З

Bb/f. 1

fuz. /

-Е,

fuz. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| КОЛЬЦЕВОЙ СЧЕТЧИК ИМПУЛЬСОВ | 1972 |

|

SU331489A1 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО РЕЗЕРВИРОВАНИЯ СИГНАЛЬНЫХ ЛАМП | 1991 |

|

RU2047907C1 |

| ЭНЕРГОСБЕРЕГАЮЩЕЕ УСТРОЙСТВО ЭЛЕКТРОСНАБЖЕНИЯ (КВАРТИРЫ, ДОМА, ПОМЕСТЬЯ) С ДИСТАНЦИОННЫМ УПРАВЛЕНИЕМ | 2008 |

|

RU2409825C2 |

| Счетчик импульсов | 1990 |

|

SU1786658A1 |

| РАСПРЕДЕЛИТЕЛЬ НА ТИРИСТОРАХ | 1970 |

|

SU275122A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1970 |

|

SU268494A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1973 |

|

SU453806A1 |

| Токоограничивающее устройство для защиты контакта в цепи постоянного тока | 1991 |

|

SU1817148A1 |

| Пересчетное устройство | 1980 |

|

SU869064A1 |

Даты

1972-01-01—Публикация