Изобретение относится к области вычислительной техники и может быть применено в комплексе с плоской антенной .решеткой в различных радиолокационных станциях в случаях, когда от вычислителя не требуется запоминания вычисленной фазы излучения, а элемент памяти имеется или в фазовращателях (ферриты с прямоугольной петлей гистерезиса, pin-диоды с S-образной характеристикой) или в управляющих или ключевых схемах (тиристоры, туннельные диоды и др.).

Известно устройство для управления лучом плоской антенной решетки, состоящее из двух координатных множительных устройств, выполненных на пересчетных схемах, выходы которых через логические схемы «ИЛИ подсоединены ко входам дещифраторов, а входы координатных устройств подсоединены к выходам преобразователя или вычитающего счетчика.

Недостатком этого устройства является наличие дещифраторов (по одному на каждый излучатель), а так как в каждый дещиф.ратор входит в зависимости от требуемой точности 3, 4 триггера, то при 900 излучателях в антенной рещетке (30 строк и 30 столбцов) это составит от 2700 до 3600 триггеров.

При наличии в фазовращателях или ключевых схемах элемента памяти можно исключить дешифраторы из состава устройства, а суммирование информации, приходящей по строкам и столбцам с координатных множительных устройств, производить с помощью известной схемы матричного суммирования.

Предлагаемое устройство для управления лучом плоской антенной решетки состоит из

узла управления вычислителем, узла вычитающих счетчиков двух координатных множительных устройств и схемы матричного суммирования. В схеме матричного суммирования для каждой строки и каждого столбца имеется счетчик, состоящий в зависимости от точности, из трех или четырех триггеров. Общее число триггеров при этом (для 30 строк и 30 столбцов) равно 180-240. При этом число логических схем «И остается таким как в схеме с дешифраторами, т. е. по одной на каждую ключевую схему. Следовательно, предлагаемый вычислитель имеет меньшее число элементов (180-240 триггеров вместо 2700- 3600).

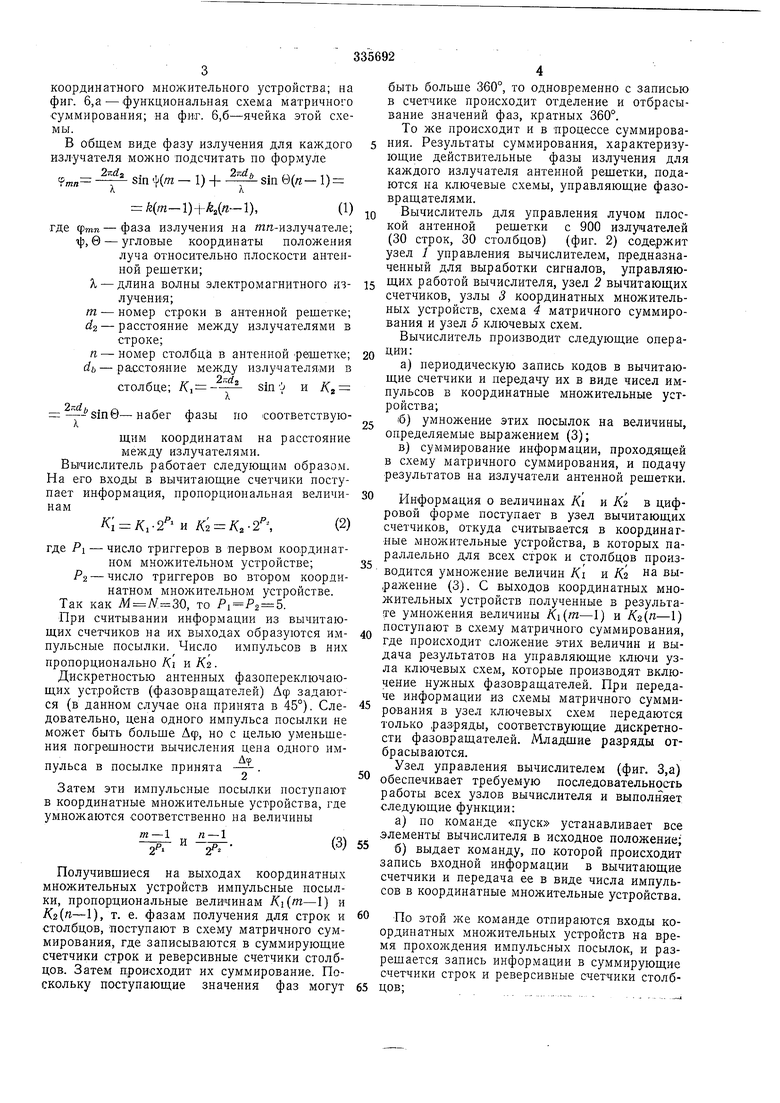

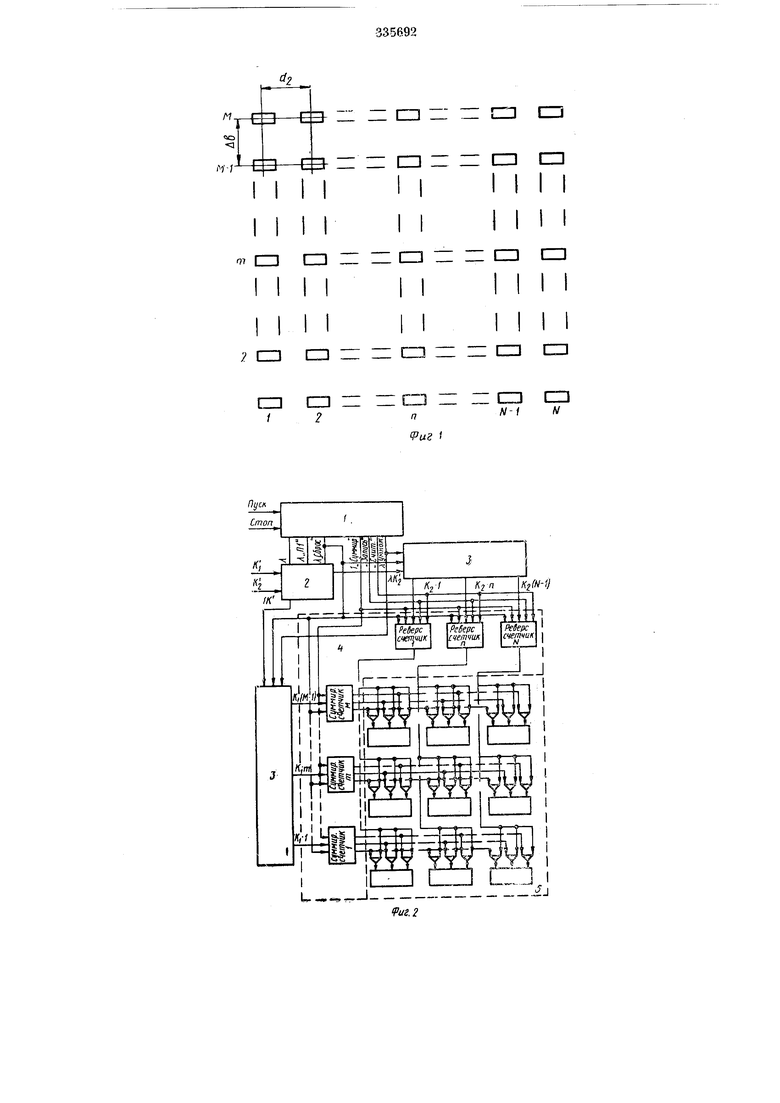

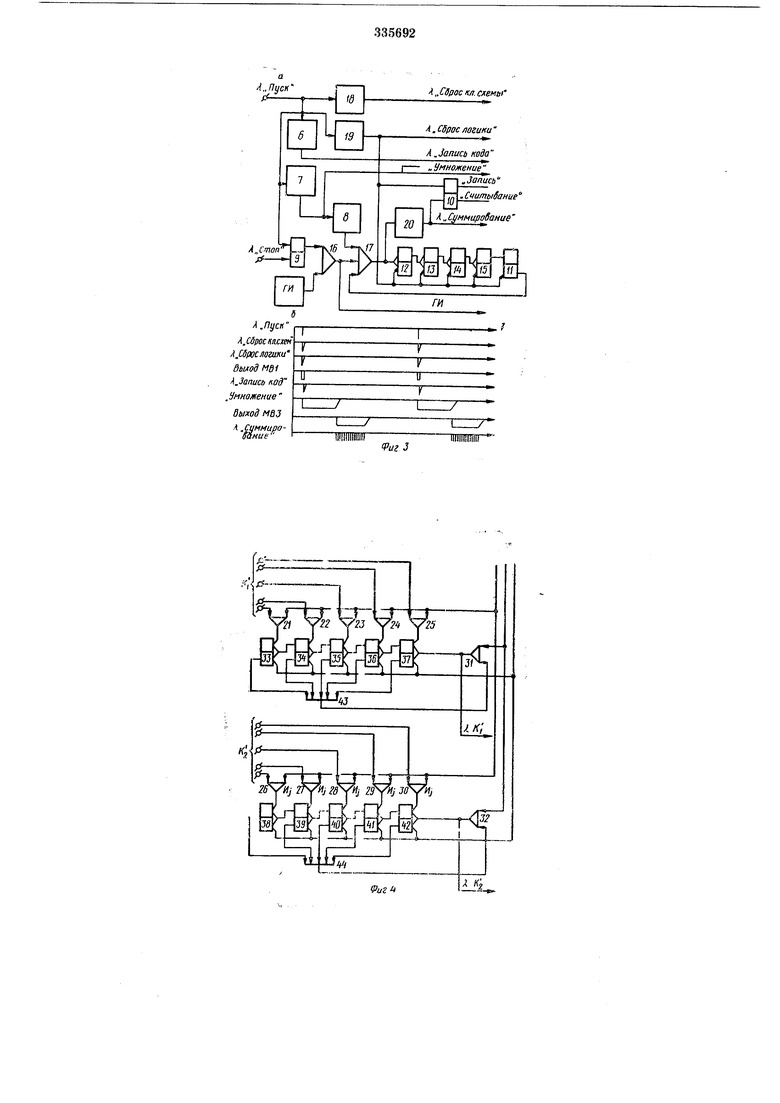

На фиг. 1 представлена схема размещения излучателей на плоской антенной рещетке; на фиг. 2 - блок-схема вычислителя; на фиг. 3- узел управления вычислителем; на фиг. 4 - функциональная схема узла вычитающих счеткоординатного множительного устройства; на фиг. б,а -функциональная схема матричного суммирования; на фиг. 6,6-ячейка этой с.хемы. В общем виде фазу излучения для каждого излучателя можно подсчитать но формуле - sin ..Km - 1) + sin е(«- 1): k(,,(n-T), где фттг-фаза излучения на «ш-излучателе; ф, в - угловые координаты положения луча относительно плоскости антенной решетки; А -длина волны электромагнитного излучения;т - номер строки в антенной решетке; 2 - расстояние между излучателями в строке; п - номер столбца в антенной -рещетке; db - расстояние между излучателями в столбце; sin ; -л К - -sine-набег фазы по соответствуюXщим координатам на расстояние между излучателями. Вычислитель работает следующим образом. На его входы в вычитающие счетчики поступает информация, пропорциональная величинам,. (2) где PI - число триггеров в первом координатном множительном устройстве; PZ - число триггеров во втором координатном множительном устройстве. Так как , то 5. При считывании информации из вычитающих счетчиков на их выходах образуются импульсные посылки. Число импульсов в них пропорционально/Ci и/(2. Дискретностью антенных фазопереключающих устройств (фазовращателей) Аф задаются (в данном случае она принята в 45°). Следовательно, цена одного импульса посылки не может быть больше Аф, но с целью уменьшения погрешности вычисления цена одного нмпульса в посылке принята --. Затем эти импульсные посылки поступают в координатные множительные устройства, где умножаются соответственно на величины ,„, -1 и -- й} 2Р. -f. Получивщиеся на выходах координатных множительных устройств импульсные посылки, пропорциональные величинам K {tn-1) и Kz(n-1), т. е. фазам получения для строк и столбцов, поступают в схему матричного суммирования, где записываются в суммирующие счетчики строк и реверсивные счетчики столбцов. Затем происходит их суммирование. Побыть больше 360°, то одновременно с записью в счетчике происходит отделение и отбрасывание значений фаз, кратных 360°. То же происходит и в процессе суммирования. Результаты суммирования, характеризующие действительные фазы излучения для каждого излучателя антенной решетки, подаются на ключевые схемы, управляющие фазовращателями. Вычислитель для управления лучом плоской антенной рещетки с 900 излучателей (30 строк, 30 столбцов) (фиг. 2) содержит узел / управления вычислителем, предназначенный для выработки сигналов, управляю, „„ Щ«х работой вычислителя, узел 2 вычитающих счетчиков, узлы 3 координатных множительных устройств, схема 4 матричного суммирования и узел 5 ключевых схем. Вычислитель производит следующие операции;а) периодическую запись кодов в вычитающие счетчики и передачу их в виде чисел импульсов в координатные множительные устройства; (б) умножение этих посылок на величины, определяемые выражением (3); в) суммирование информации, проходящей в схему матричного суммирования, и подачу результатов на излучатели антенной решетки. Информация о величинах /Ci и /(2 в цифровой форме поступает в узел вычитающих счетчиков, откуда считывается в координатные множительные устройства, в которых параллельно для всех строк и столбцов производится умножение величин /С: и /Сз на выражение (3). С выходов координатных множительных устройств полученные в результате умножения величины К(т-1) и K.z(n-1) поступают в схему матричного суммирования, где происходит сложение этих величин и выдача результатов на управляющие ключи узла ключевых схем, которые производят включение нужных фазовращателей. При передаче информации из схемы матричного суммирования в узел ключевых схем передаются только разряды, соответствующие дискретности фазовращателей. Младшие разряды отбрасываются. Узел управления вычислителем (фит. 3,а) обеспечивает требуемую последовательность работы всех узлов вычислителя и выполняет следующие функции: а) по команде «пуск устанавливает все элементы вычислителя в исходное положение; б) выдает команду, по которой происходит запись входной информации в вычитающие счетчики и передача ее в виде числа импульсов в координатные множительные устройства. По этой же команде отпираются входы координатных мнол ительных устройств на время прохол ;дения импульсных посылок, и разрешается запись информации в суммирующие счетчики строк и реверсивные счетчики столбв) вырабатывает импульсы суммировании, подаваемые в суммируюгпне счетчики строк и реверсивные счетчики столбцов и выдает команду «считывание в реверсивные счо-- ики столбцов одновременно с исступлением импульсов суммирования.

Узел управления вычислителем содержит генератор импульсов ГИ, три ждущих мультивибратора 6-8, три статических триггера 9- 11 с раздельными входами, четырехразрядный счетчик импульсов суммирования, выполненный на статических триггерах 12-15, две схемы совпадения 16, 17 и три усилителя 18-20.

Команда «пуск, поступающая на вход узла управления вычислителем, запускает усилители сброса 18, 19 и триггер 9 отпирающий при этом схему совпадения 16. В результате импульсы ГИ поступают на вход схемы совпадения 17 и на вход узла вычитающих счетчиков, а также триггер 10, являющийся триггером знака для реверсивных счетчиков столбцов. При этом на выходе триггера 10 формируется команда «запись.

Одновременно запускаются мультивибратор 6, формирующий задним фронтом своего выходного импульса команду записи кода в узел вычитающих счетчиков, мультивибратор 7, па выходе которого формируется команда «умножение, отпирающая входы координатных множительных устройств на время прохождения импульсных посылок.

Возвращаясь в исходное положение, мультивибратор 7 запускает мультивибратор 8, отпирающий своим выходом схему совпадения 17 на время, необходимое для формирования импульсов суммирования, поступаюихих на входы суммирующих счетчиков строк и реверсивных счетчиков столбцов. Одновременно эти импульсы запускают триггер 10, формируя команду «считывание, поступающую в реверсивные счетчики столбцов.

Разрядность счетчика импульсов, определяющая число импульсов суММИроваиия, зависит от выбранной точности вычисления фазы

Д-Р излучения, т. е. от величины -- .

Для данного случая - 22,5°, а число импульсов суммирования равно «16.

Импульсы суммирования, поступая в суммирующие счетчики строк и реверсивные счетчики столбцов осуществляют сложение величин /Ci(/n-1) и К.1:(п-1) и выдачу результата в ключевые схемы, обеспечивает треблемую фазу излучения на излучателях антенной рещетки.

Импульс «стоп, поступая на вход узла управления вычислителем, запускает триггер 9, запирающий схему совпадения 16. В результате прекращается поступление импульсов ГИ, и прерывается работа вычислителя.

На фиг. 3,6 представлена последовательность команд, вырабатываемых узлом управления вычислителем.

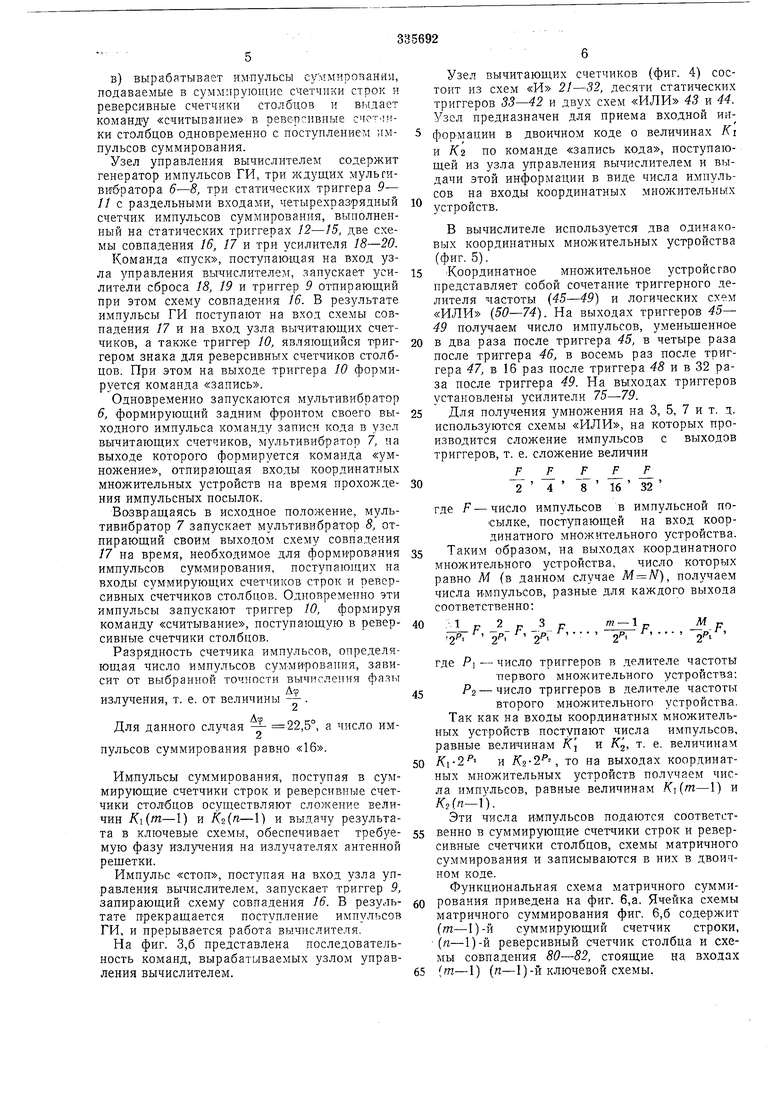

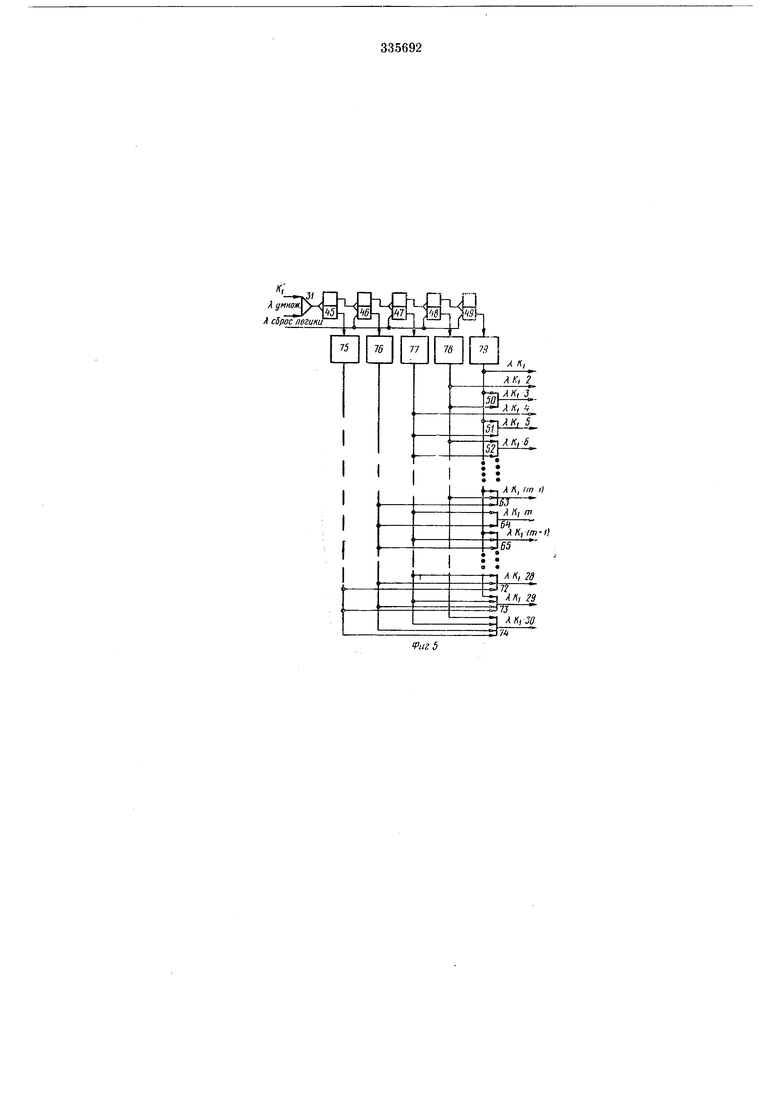

Узел вычитающих счетчиков (фиг. 4) состоит из схем «И 21-32, десяти статических триггеров 33-42 и двух схем «ИЛИ 43 и 44. Узел предназначен для приема входной информации Б двоичном коде о величинах Кг и Kz по команде «запись кода, поступающей из узла управления вычислителем и выдачи этой информации в виде числа импульсов на входы координатных множительных устройств.

В вычислителе используется два одинаковых координатных множительных устройства (фиг. 5).

Координатное множительное устройство представляет собой сочетание триггерного делителя частоты (45-49 и логических схем «ИЛИ (50-74). На выходах триггеров 45- 49 получаем число импульсов, уменьшенное в два раза после триггера 45, в четыре раза после триггера 46, в восемь раз после триггера 47, в 16 раз после триггера и в 32 раза после триггера 49. На выходах триггеров установлены усилители 75-79.

Для получения умножения на 3, 5, 7 и т. д. используются схемы «ИЛИ, на которых производится сложение импульсов с выходов триггеров, т. е. сложение величин

JL Z- I- I- 1Т Т Т 1б 32

где F - число импульсов в импульсной посылке, поступающей на вход координатного множительного устройства. Таким образом, на выходах координатного множительного устройства, число которых равно М (в данном случае М Щ, получаем числа импульсов, разные для каждого выхода соответственно:

-Л г- 2 ,-, 3 р/и -1 р

где Р - число триггеров в делителе частоты первого множительного устройства: 2 - число триггеров в делителе частоты

второго множительного устройства. Так как на входы координатных множительных устройств поступают числа импульсов, равные величинам К и /Cj, т. е. величинам /Ci-2 и Kz-l, то на выходах координатных множительных устройств получаем числа импульсов, равные величинам Ki(m-1) и («-).

Эти числа импульсов подаются соответственно в суммирующие счетчики строк и реверсивные счетчики столбцов, схемы матричного суммирования и записываются в них в двои1ном коде.

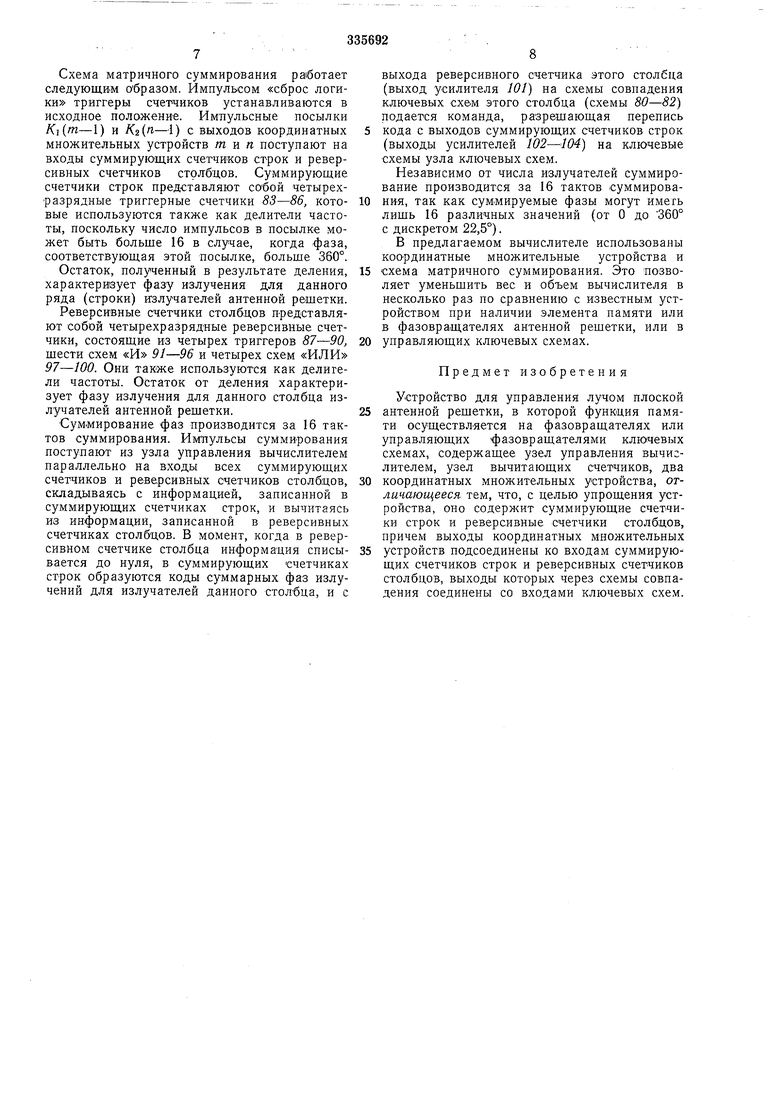

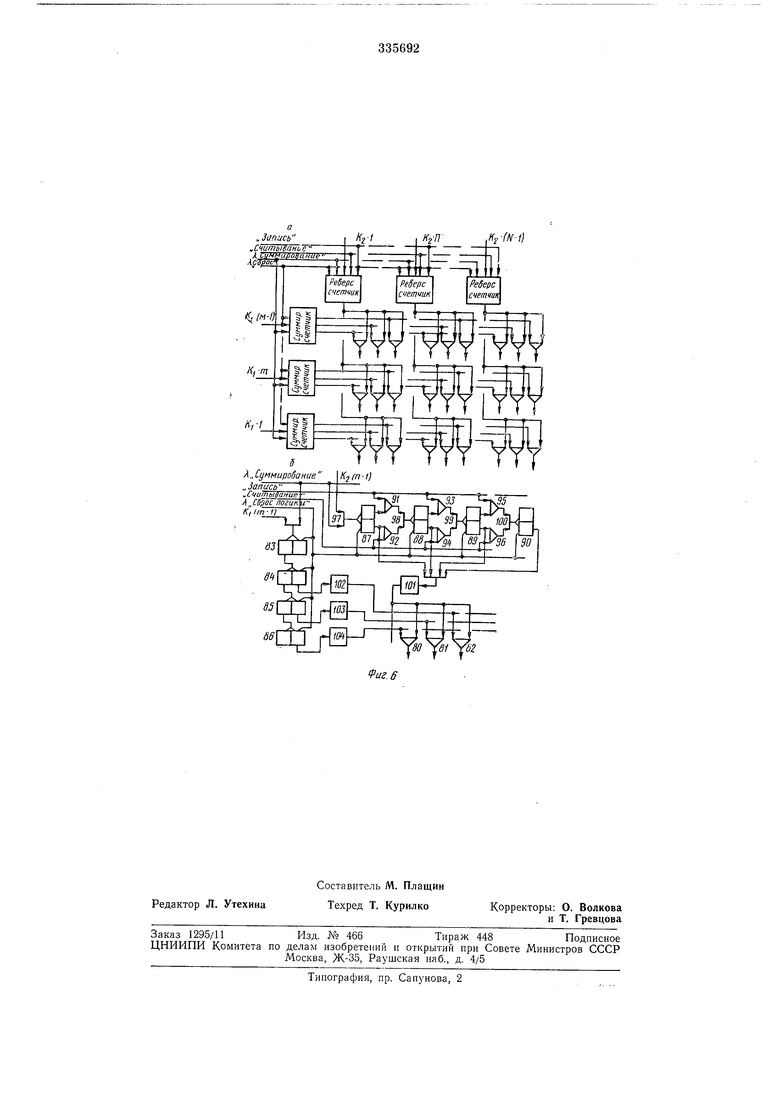

Функциональная схема матричного суммирования приведена на фиг. 6,а. Ячейка схемы матричного суммирования фиг. 6,6 содержит (т-1)-й суммирующий счетчик строки, (п-1)-й реверсивный счетчик столбца и схемы совпадения 80-82, стоящие на входах {т-1) (п-1)-и ключевой схемы.

Схема матричного суммирования работает следующим образом. Импульсом «сброс логики триггеры счетчиков устанавливаются в исходное положение. Импульсные посылки Ki{m-1) и Kzin-1) с выходов координатных множительных устройств тип поступают на входы суммирующих счетчиков строк и реверсивных счетчиков столбцов. Суммирующие счетчики строк представляют собой четырехразрядные триггерные счетчики 83-86, котовые используются также как делители частоты, поскольку число импульсов в посылке может быть больще 16 в случае, когда фаза, соответствующая этой посылке, больще 360°.

Остато.к, полученный в результате деления, характериеует фазу излучения для данного ряда (строки) излучателей антенной рещетки.

Реверсивные счетчики столбцов представляют собой четырехразрядные реверсивные счетчики, состоящие из четырех триггеров 87-90 щести схем «И 91-96 и четырех схем «ИЛИ 97-100. Они также используются как делигели частоты. Остаток от деления характеризует фазу излучения для данного столбца излучателей антенной рещетки.

Суммирование фаз производится за 16 тактов суммирования. Имлульсы суммирования поступают из узла управления вычислителем параллельно на входы всех суммирующих счетчиков и реверсивных счетчиков столбцов, складываясь с информацией, записанной в суммирующих счетчиках строк, и вычитаясь из информации, записанной в реверсивных счетчиках столбцов. В момент, когда в реверсивном счетчике столбца информация списывается до нуля, в суммирующих счетчиках строк образуются коды суммарных фаз излучений для излучателей данного столбца, и с

выхода реверсивного счетчика этого столбца (выход усилителя 101) на схемы совпадения ключевых схем этого столбца (схемы 80-82) подается команда, разрещающая перепись

кода с выходов суммирующих счетчиков строк (выходы усилителей 102-104) на ключевые схемы узла ключевых схем.

Независимо от числа излучателей суммирование производится за 16 тактов суммирования, так как сум.мируемые фазы могут иметь лищь 16 различных значений (от О до 360° с дискретом 22,5°).

В предлагаемом вычислителе использованы координатные множительные устройства и

схема матричного суммирования. Это позволяет уменьшить вес и объем вычислителя в несколько раз по сравнению с известным устройством при наличии элемента памяти или в фазовращателях антенной рещетки, или в

управляющих ключевых схемах.

Предмет изобретения

Устройство для управления лучом плоской антенной рещетки, в которой функция памяти осуществляется на фазовращателях или управляющих фазовращателями ключевых схемах, содержащее узел управления вычислителем, узел вычитающих счетчиков, два координатных множительных устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит суммирующие счетчики строк и реверсивные счетчики столбцов, причем выходы координатных множительных устройств подсоединены ко входам суммирующих счетчиков строк и реверсивных счетчиков столбцов, выходы которых через схемы совпадения соединены со входами ключевых схем.

Ф I-I iiiiz:iz iiizi iD d}

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для управления лучом плоской антенной решетки | 1981 |

|

SU1013967A1 |

| Устройство для управления лучом плоской антенной решетки | 1983 |

|

SU1167616A1 |

| Вычислительное устройство для управления лучом плоской антенной решетки | 1988 |

|

SU1532944A1 |

| Вычислительное устройство для управления лучом плоской антенной решетки | 1988 |

|

SU1580393A1 |

| Устройство для управления лучом антенной решетки | 1983 |

|

SU1144118A1 |

| Вычислительное устройство для управления решеткой излучателей | 1983 |

|

SU1150630A1 |

| Микропроцессорное устройство управления лучом плоской антенной решетки | 1984 |

|

SU1206797A1 |

| Фазированная антенная решетка | 1983 |

|

SU1190436A1 |

| УСТРОЙСТВО для УПРАВЛЕНИЯ ЛУЧОМ ПЛОСКОЙ АНТЕННОЙ РЕШЕТКИ | 1969 |

|

SU249061A1 |

| Антенная система с фазовым управлением | 1988 |

|

SU1597987A1 |

7 d IZ CZ3

cm cz

/2

ZH CZ

cm CZD

A/-fV

Ki(N-,l

/I ,Пуск А,С6рас111и:хен ,,Сдрос логики дшод Mdi .Запись код Умнйяение Выход MBJ Л,Сумкиfo4 „Сирас кл. схемцГ

illlllilliiHr

Vi/г J

л л, чп }

J6J

т /t я, V7J

:tjr-

т ЛК,/т

ЛК, 2д

cJTT ХЛ, 23

W X/f, Jtf

л./л-/;

Даты

1972-01-01—Публикация