и вторым тактовым входам операционного блока и .блока постоянной памяти, выходы шины данных которого подключены к входам шины данных операционного блока, буферного регистра и блока сопряжения, входы-выходы шины первого и второго каналов которого являются входом шины данных и выходом результата вычислителя, выход шины адреса операционного блока подключен к входам шнны адреса блока постоИННОЙ памяти, первый и второй входы адреса блока сопряжения подключены к выходам первого и второго разрядов шины адреса операционного блока, выход разрешения приема инфор мации с шины данных и выход признака выдачи информации на шину данных операционного блока подключены к перИзобретение относится к вычислительной и импульсной технике и може быть использовано для управления лучом плоских фазированных антенных решеток с электронным сканированием луча.

Целью изобретения является повышение точности управления антенной решеткой за счет увеличения разрядности слоев при вычислениях.

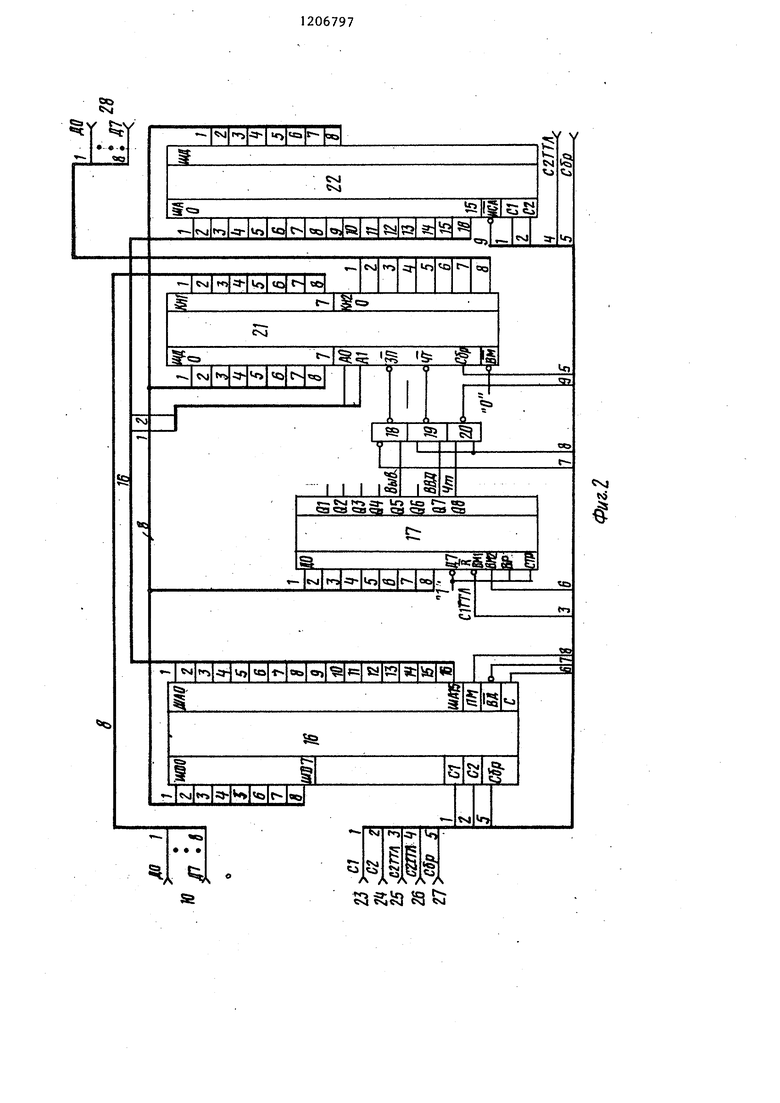

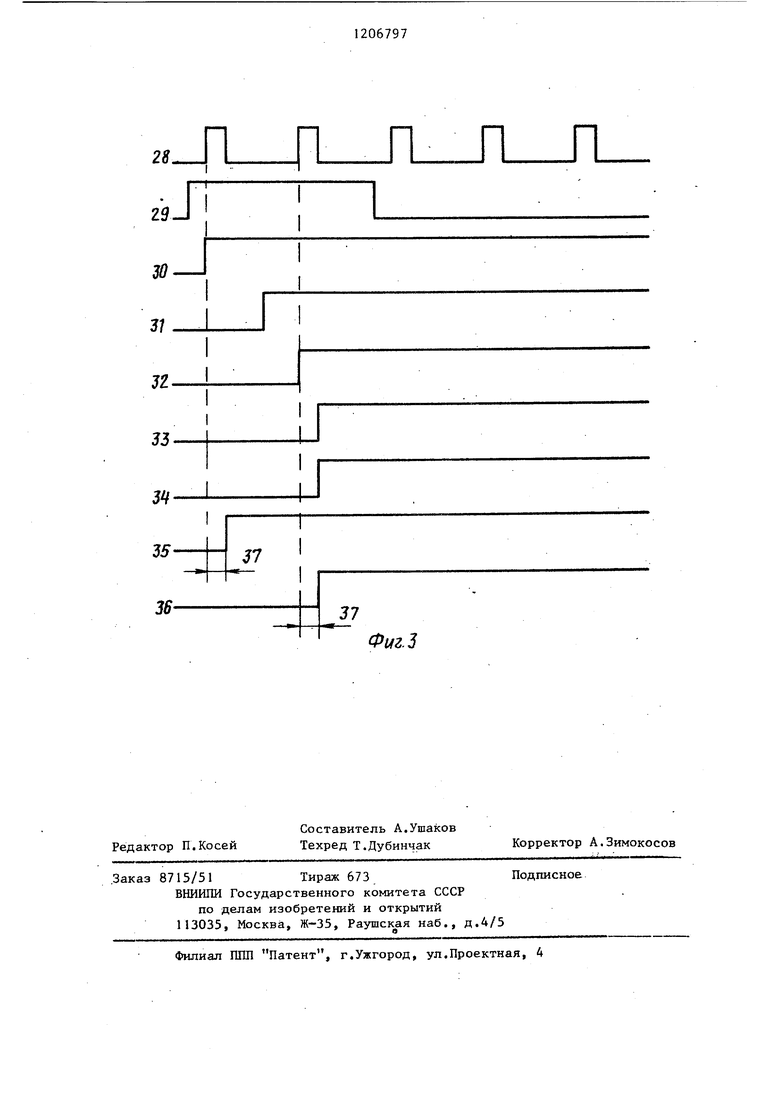

На фиг. 1 приведена функциональная схема микропроцессорного устройства управления; на фиг. 2 - функциональная схема первого и второго вычислителя; на фиг, 3 - временная диаграмма работы устройства.

Устройство (фиг.1) содержит первый вычислитель 1, второй вычислитель 2, первый буферный регистр 3, второй буферный регистр 4, которые образуют блок управления, сумматоры 5 столбцов, сумматоры 6 строк, сумматоры 7 матрицы с выходами 8 устройства, нагруженными на входы управления фазовращателей, первую шину 9 данных, вторую шину 10 данных, первый 11 и второй 12 тактовые входы устройства, прямой и инверсный входы 13 и 14 синхронизации, вход 15 рброса устройства. Вычисвым входам второго и третьего элементов И-НЕ и к инверсному входу первого элемента И-НЕ соответственно, выходы пятого, седьмого и восьмого разрядов буферного регистра подключены к прямому входу первого и к вторым -входам второго и третьего элементов И-НЕ соответственно, выходы которых подключены к входам Запись, Чтение блока сопряжения и к входу импульса синхронизации адреса блока постоянной памяти соответственно, выход синхронизации операционного блока подключен к прямому входу Выбор микросхемы буферного регистра, .инверсный вход синхронизации вычислителя подключен к инверсному входу Выбор микросхемы буферного регистра.

литель СФИГ.2) содержит операционный блок 16, буферный регистр 17, три элемента И-НЕ 18-20, блок 21 сопряжения, блок 22 постоянной памяти,

первый 23 и второй 24 тактовые входы вычислителя, инверсный 25 и прямой 26 входы синхронизации вычислителя, вход 27 сброса. На фиг.З приведены временные диаграммы сигнала 28, подаваемых на инверсный вход синхронизации устройства, сигнала 29 данных на выходе второго канала блока 21 первого вычислителя 1; сигнала 30 данных в первом

буферном регистре 3; сигнала 31 данных на выходе второго канала блока 21 второго вычислителя 2; сигнала 32 данных во втором буферном регистре 4; сигнала 33 суммы на выходе первого сумматора первого

столбца; сигнала 34 суммы на выходе сумматора второго столбца; сигнала 35 суммы на выходе сумматора второй строки; сигнала 36 суммы на выходах второго сумматора первой

строки, первого и второго сумматоров второго столбца 39, Промежуток 37 означает время срабатывания бинационного сумматора (фиг.ЗУ.

Устройство работает следующим ебйдзом,

Фаза колебаний, подаваемых на элементарные излучатели, вычисляется по формуле , H,Hv;H( °/ SiH4 } H, 1

{{СУо/Л)51ив} рИд2 } (1) где

- расстояние между элементарными излучателями по оси Xj

Vo - расстояние между эле- ментарными излучателями по оси У;

Ч, 0 - угловые координаты положения луча относительно плокости антенной решетки;

Д - длина волны электромагнит .ного излуче ния; номер строки излучателей в антенной решетке;

Ну - нЪмер столбца излучателей в антенной решетке;

(...}- операция вьщеления дробно t Jflp

части числа;

{... - операция выделения целой

части числа;

V - целое число, принимакнцее значения 1-3.

I Отдельный ,фа зовра1чатель обеспечивает сдвиг фазы на 21Г/2.. Полученное в результате выполнения форму- пы ( 1) значение YI, - подаваемое на входы управления фазовращателей, будет представлено в виде V -разрядного параллельного двоичного кода, каждый разряд которого управляет соответствующим фазовращателем цепочки фазовращателей, нагруженных на элементарный излучатель антенной решетки. Вьщеление дробной части вычисленного значения фазы позволяет избавиться от целого числа периодов 2.

В первый вычислитель поступает код Хо /Д , а затем код угла Ч , который в первом операционном блоке 16 (микропроцессоре) преобразуется в адрес sinif, хранящегося в блоке 22 первого вычислителя 1. По полученному адресу происходит выбор ,из блока 22 кода sin , после чего I выполняется умножение Хо/л на sinH и результат записывается в первый буферный регистр 3. Одновременно с первым вычислителем .1 второй вычислитель 2 по вводимым значениям ,Уо /Д н вычисляет значение (Уо/Д) sin0 и записываеу его во второй буфер- ный регистры. Далее на сумматорах 5

206797

столбцов производится многократное суммирование/;соответствующее умножению (У,/Д) sin у на hy , одновре- менно с этим на сумматорах 6 строк -с выполняется многократное суммирова-- ние, соответствующее умножению Ц на н . Затем на суммато- pax 7 производится заключительное суммирование, соответствующее форму

10

ле СП и полученные значения У

хпу

выдаются на соответствуницие цепочки фазовращателя. Каждому фазовращателю цепочки соответствует свой разряд кода управления фазовра15 щателями. Единица в разряде означает команду Включить фазовращатель, ноль в разряде кода соотвествует команде Выключить фазовращатель.

20 На вход сброса 15 устройства

подается сигнал сброса, который устанавливает в О счетчики команд микропроцессоро з, блоки 21 и регисры 3 и 4.

25 Машинный цикл работы микропроцессора включает от трех до пяти тактов и соответствует чтению или записи в блок 22 или во внешнее устройство одного байта информации,

30:|соманды микропроцессора выполняются за несколько машинных цикло в зависимости от длины команды и реализуемых операций. При выполнении команды в первом такте содер35 жимое счетчика команд выдается на шину адреса. В этом же такте микропроцессор выдает на шину данных восьмиразрядное управляющее слово и формирует сигнал синхронизации,

40 по которому это слово записьшает- ся в буферный регистр 17. Управляющее слово указывает тип выполняемого машинного цикла. Во втором такте содержимое счетчика команд увели45 чивается на единицу. В третьем такте данные принимаются из блока 21 или внешнего устройства на шину данных и записываются в регистр команд (если выполняется машинный

50 цикл выборки команды) или в один из регистров микропроцессора. В четвертом и пятом такте, если они необхо- димз1, выполняются действия над опе- рандагм. Если команда включает нес-

55 колько циклов, то по завершении текущего машинного цикла микродроцес- сор переходит к первому такту следущего цикла.

Сразу после снятия сигнала сброса с входа 15 сброса устройства начинается выполнение первым и вторым

микропроцессорами 16 команд, запи- , санных соответственно в первом и втором блоках 22. Первая команда рограм ф), выполняемой первым микропроцессором, обеспечивает запись управляющего слова из микропроцессора Q регистр управляющего слова первого блока 21 по шине данных. Управяющее слово определяет работу первого и второго блоков 21 в режиме, при котором информация, поступающая j а первый блб1 21 первой входной шины данных, запоминается в буфером регистре соответствующего канаа и сразу же передается на его выоды без стробирования. Для записи 20 управляющего слова в регистр управяющего слова с пятого выхода первого буферного регистра 17, в котором хранится управляющее слово выполнения команды, на первый эле- 25 мент И-НЕ подается логическая единица. Первый микропроцессор вьщает логический ноль с инверсного выхода выдачи, поступающий на инверс- ньй вход первого злемента И-НЕ, JQ Логический ноль с выхода первого элемента И-НЕ поступает на инверсный вход записи первого блока 21 устройства. Одновременно первый микропроцессор выдает логические единицы на первый и второй адресные входы первого блока 21.Далее на первую входную шину данных подается старший байт шестнадцатиразрядного кода значения, Выпол- ... няется команда ввода с первого канала. В первом цикле вьшолнения этой команды осуществляется посылка адреса команды из счетчика команд первого микропроцессора в первый блок 22 и запись управлякяцего слова в первый буферный регистр 17 по сигналу синхронизации с первого микропроцессора. После увеличения содержимого счетчика команд на единицу первый микропроцессор с выхода приема выдает.логическую единицу, которая стробирует сигнал чтения, выдаваемый с восьмого выхода первого буферного регистра 17 на третий (элемент И-НЕ). Полученный инверсный сигнал чтения с выхода третьего элемента И-НЕ подается на инверсный вход сопровождения адреса первого блока 22,

35

45

55

,

Q j 0 5 Q

..

5

5

где происходит считывание по адресу, выданному первым микропроцессором на адресные входы первого блока 22 и выдача первого байта команды из первого блока 22 в регистр команд первого микропроцессора. Во втором цикле выполнения команды ввода с первого канала в первый блок 22

посьшается увеличенный на единицу адрес из счетчика команд и аналогично осуществляется прием второго байта команды в регистр временного хранения первого микропроцессора. Этот байт представляет собой номер первого ввода, к которому производится обращение. В третьем цикле этот номер в качестве адреса выводится с первого и второго разрядов адресного выхода первого микропроцессора и подается на первый и второй адресные входы первого блока 21.

Одновременно с этим в первый буферный регистр 17 записьтается управляющее слово. После увеличе- содержимого счетчика команд на единицу первый микропроцессор выдает логическую единицу с выхода приема, которая стробирует логическую единицу с седьмого выхода первого буферного регистра 17, поданную на вход второго элемента И-НЕ после записи в первый буферный регистр 17 управляющего слова. Инверсный сигнал с выхода второго элемента И-НЕ подается на инверсный вход чтения первого блока 22, в результате чего слово данных Хо/д записывается с первого канала блока 21. На этом выполнение команды ввода с первого канала первого блока 21 закончено.

Далее выполняется команда пересылки содержащегося в аккумуляторе первого микропроцессора старше- . го байта кода Хо/А в регистр В пер- , вого микропроцессор а. Затем на вход- шину подается мпадпий байт шест надцатиразрядного кода о/д и выпол- няется команда ввода с первЬго jiatia- ла первого блока 21, по которой мпадший байт записывается в аккумулятор первого микропроцессора. Затем выполняется команда пересылки содержимого аккумулятора в регистр С первого микропроцессора. В итоге выполнения описанных команд в регистровую пару Б,С оказывается записанным шестнадцатиразрядный код значения °lj(. , причем старший байт определяет целую часть числа, а младший - дробную.

В первом блоке 22 последовательн записана программа работы первого . вычислителя, а далее значения синусов углов. Синус каждого угла записан в виде восьмиразрядного числа в двоичном коде, причем это число меньше единицы.

Далее выполняется команда загруз ки числа регистр Ь первого микрпроцессора. Число - номер ячейки первого постоянного запоминающего устройства, где записан по.рледний байт последней команды пpoгpa iмы работы первого вычислителя. В ячейке первого блока 22 с адресом ё I хранится код sin 1°, в ячейке с адресом +2 - код . sin 2°и т.д. Со внешнего устройства на первую входную восьмиразрядную шину данных подается код угла Ч . По команде ввода с первого канала код угла Ч записьтается в аккумулятор первого микропроцессора через первый блок 21, по команде передачи содержимое аккумулятора передается в регистр Е первого микропроцессора. Следующая команда обеспечивает суммирование содержимого регистровой пары Н J L с содержимым регистровой пары 1 , Е и запись результата в регистровую пару Н , и .В результате выполнения этой команды происходит суммирование и кода угла, в результате чего в регистровой паре Н , L оказывается записанным адрес синуса угла f в первом блоке 22. По следующей команде происходит обращение к первому блоку 22 по адресу, записанному в регистровой паре И ,L и запись sin в аккумулятор первого микропроцессора.

Затем следующая команда обнуляет содержимое регистровой пары М,и Следуюв1ая команда записывает в регистр Е первого микропроцессора двоичное число 1000.

Далее начинает выполняться подпрограмма умножения Хо/д на sin У со сдвигом sin У влево, начиная со (Старших разрядов. По следующей команде, обозначенной меткой.МЗ, , происходит циклический сдвиг содержащегося 3 аккумуляторе первого

микропроцессора кода sinY на один разряд влево, при этом старший разряд кода записывается в разряд пере- 5 носа регистра признаков, а содержимое регистра признаков записывается в младший разряд аккумулятора. Следующая команда передает содержимое аккумулятора в регистр 3) перво10 го микропроцессора, при этом содер- жи.мое разряда переноса не меняется. Далее выполняется команда условного переноса. Если в разряде переноса О, то происходит переход к выпол5 команды с меткой. Ml, если 8 разряде переноса О, то проис- ходит переход к выполнению следующей команды, по которой содержимое регистровой пары В , С суммир г0 :ется с содержимым регистровой пары .H,L и результат записывается в регистровую пару Н ., L .. По следующей команде, .обозначенной меткой Ml, производится уменьщение содержимо5 I го регистра Е на единицу. Если в результате выполнения этой команды во всех восьми разрядах регистра Б будут нули, то в разряде нуля регистра признаков первого микро-

0 процессора установится единица, иначе там .будут нули. .

Следующая команда является командой :условного перехода. Если в разряде нуля регистра признаков перво5 го микропроцессора единица, то осуществляется переход к команде с меткой М2, если ноль, то выполняется следующая команда, по которой к содержащемуся в регистровой паре

0 Н L числу прибавляется это же чис- ,ло, чем достигается сдвиг этого числа на один разряд влево.

Далее выполняется команда, по которой содержимое регистра 1 пересылается в аккумулятор. Следующая команда осуществляет безусловный переход к команде циклического сдвига влево, обозначенной меткой МЗ. 0 Таким образом, команды, начиная с команды циклического сдвига, выполняются циклически до тех пор, пока в регистре Е не останутся одни нули, т.е. восемь раз. В результате выполнения подпрограммы умножения в регистровой паре Н ,Ь будет записана дробная часть произведения (хо/Л, sinM.

Далее выполняется команда пересылки содержимого регистра И , в котором хранится старший байт дробной части произведения sinЧ () в аккумулятор . Следующая команда осуществл1 ет вывод содерлимого аккумулятора через второй канал первого блока 21 на входы первого буферного регист ра 3. Затем , выполняется команда останова первого микропроцессора.

Одновременно с первым вычислителем аналогичную программу, выполняет второй вычислитель с той разницей, что во втором блоке ,22. после программы записаны коды sind. После выполнения программы во втрром буферном регистре 4 оказывается записанным старший байт дробной части произведения tVo (л, sin©, и второй микропроцессор так же останавливается.

Первый сумматор 6 строк суммирует дробную часть произведения (Хо|я)в1пЧ с этим же числом, что соот ветствует умножению (.jsinvf на два, результат подается на вторую строку сумматоров 7 в Каждый сумматор 6 строк суммирует Хв IА sin Ч/ с результатом предьщущего сумматора 6 и выдает сумму на свою строку сумматоров 7 и на вход следующего сумматора 6 строк. Многократное суммирование дробной части произведения ()(о(д) sin Ч на сумматорах 6 строк соответствует выполнению операции ,

{Uo(A)s;H4 -Hx}gpi

. . UПервый; сумматор 5 столбцов суйг- дробную часть произведения

(.Уб/)) этим же-числом, что соответствует умножению )s; Q на два, результат подается на вто- 5 рой столбец сумматоров 7. , Каждый сумматор 5 столбцов суммирует iVe/lrsihQ результатом предыдущего сумматора и выдает сумму , на свой столбец сумматоров 7 и на 10 вход следующего сумматора 5 столбцов.

Многократное суммирование дробной части произведения (Vo/д) на восьмиразрядных комбинационных 15 сумматорах столбцов соответствует

выполнению операции )5, iv Эр

Суммирование для каждого элементарного излучателя на соответствующем сумматоре (СХо/Л)51иЧ Их}2р

20 и .Уо/Л)51и© Нч)}зр и вьщеление 1 старших разрядов дробной части суммы для управления фазовращателями обеспечивает вычисление фазы согласно формуле (1) с большой: точностью.

25 Для изменения положения луча антенной решетки подается сигнал сброса на вход 15 сброса и описанный процесс вычислений повторяется. для новьпс значений Ч , , а если есть

30 необходимость то и новых значений

°1л , VO/JL . ....

Микропроцессоры выполняются на схеме К580ИК80. Блоки 21 .сопряжения выполняются на схеме К580ИК55, 35 Буферные регистры выполняются на схе ме К589ИР12. Блок 22 постоянной памяти выполняется на схеме К586РЕ1. .Первый координатный, буферные регистры выполняются на интегральной схе- 40 ме К155ИР13.

Й- с:

%

«VJ

е SieO vl

Редактор П.Косей

Составитель А.Ушаков Техред Т.Дубинчак

.Заказ 8715/51 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

О

Филиал ШШ Патент, г.Ужгород, ул.Проектная, 4

Корректор А.Зимокосов

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1617442A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство для буферизации команд | 1991 |

|

SU1789982A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

| Программируемый контроллер | 1986 |

|

SU1328815A1 |

| Авторское свидетельство СССР № 758159, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислитель фаз для антенной решетки | 1979 |

|

SU1048479A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-23—Публикация

1984-07-12—Подача