Изобретение относится к импульсной технике.

Известен аналого-цифровой преобразователь, основанный на двухтактном интегрировании и содержит интегратор, выполненный на операционном усилителе с резистором на входе и конденсатором в цепи обратной связи, ключи для коммутации входного и эталонного напряжений, компаратор, счетчик и устройство управления.

Цель изобретения - повышение помехозащищенности с одновременным исключением влияния на точность преобразования как изменения частоты помехи, так и пестабильпости частоты заполняющих импульсов. Достигается она тем, что предлагаемый преобразователь содержит устройство синхронизации, устройство формирования интервала первого такта интегрирования в виде, например, последовательно соединенных фильтра, усилителя переменного тока, дифференцирующей ценочки, схемы совпадения и пересчетной схемы, устройство коррекции первого такта интегрирования, состоящее из ячейки запоминания аналоговой величины со входным и выходным ключами, причем два выхода устройства синхронизации подключены к двум первым входам устройства управления, третий выход - ко входу схемы совпадения, входы устройства Синхронизации подсоединены первый - к шине сигнала пуска, второй - к выходу дифференцирующей цепочки устройства формирования интервала первого такта интегрирования, входы фильтра которого подключены к земляной и входной клеммам нреобразователя.

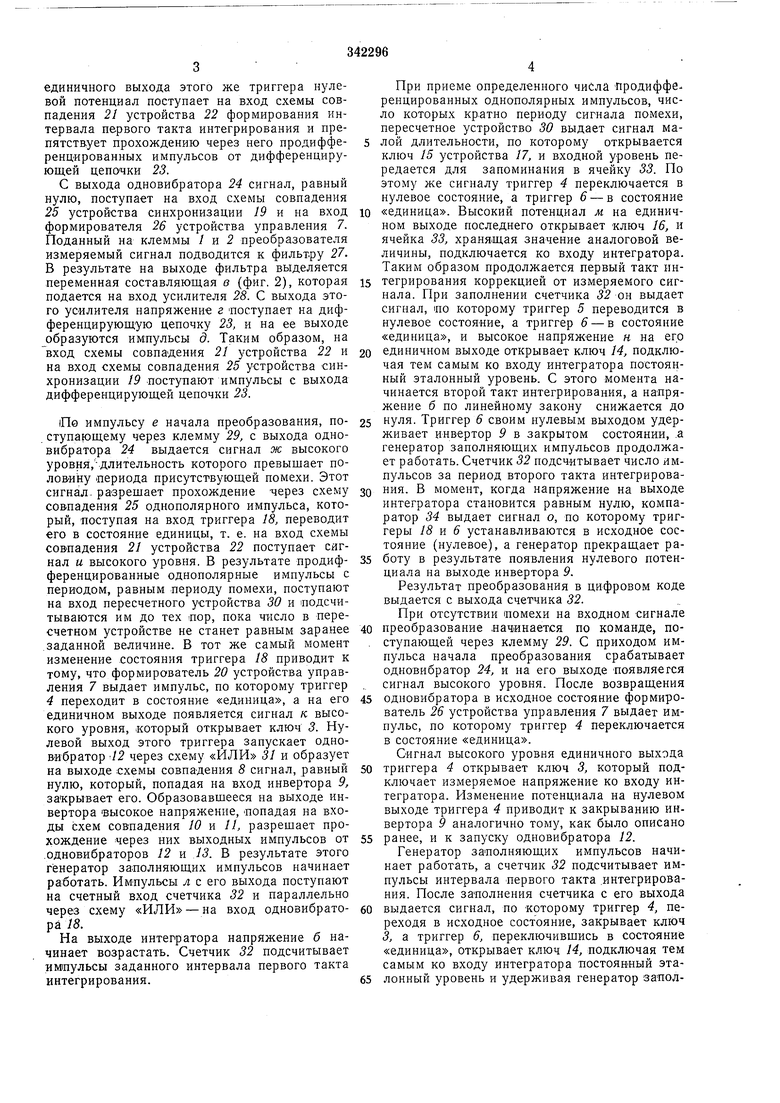

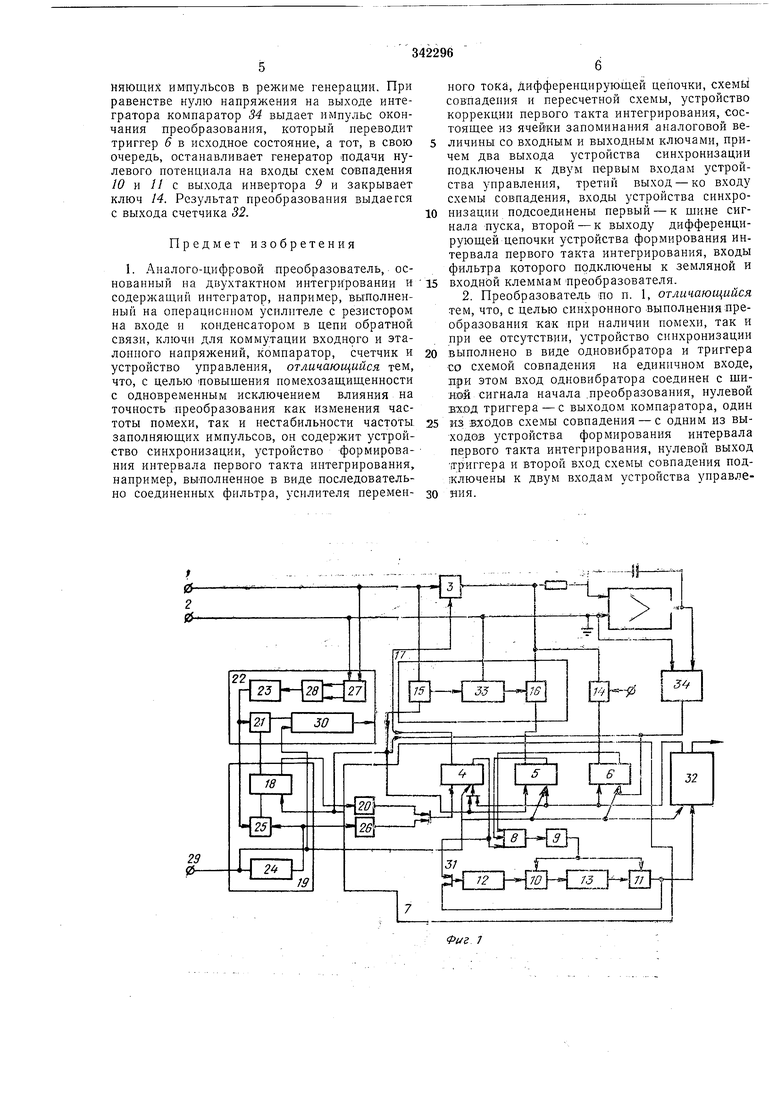

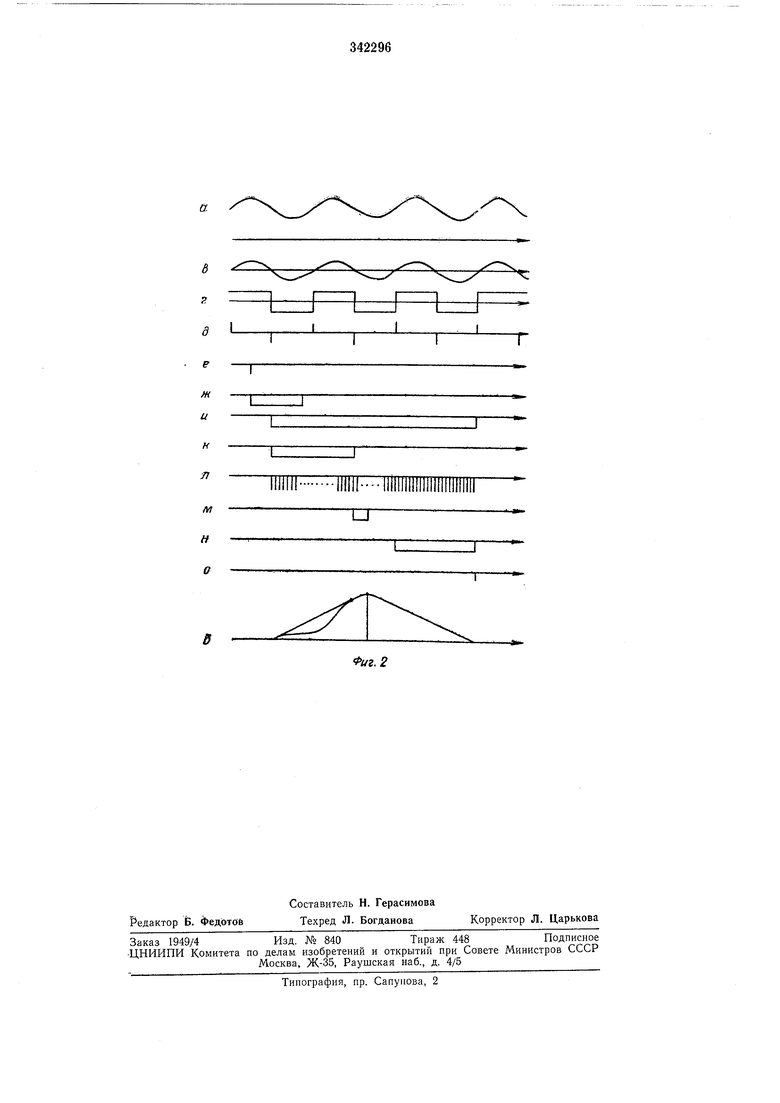

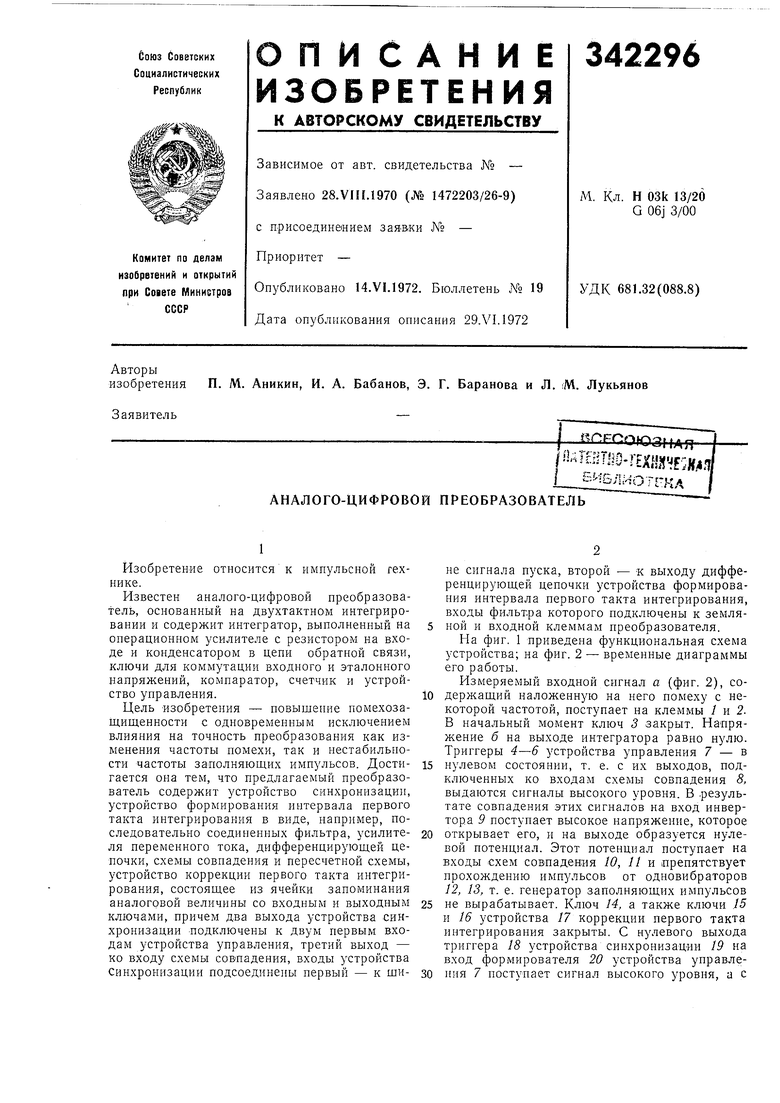

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временные диаграммы его работы.

Измеряемый входной сигнал а (фиг. 2), содержащий наложенную на него помеху с некоторой частотой, поступает на клеммы / и 2. В начальный момент ключ 3 закрыт. Напряжение б на выходе интегратора равно нулю. Триггеры 4-6 устройства управления 7 - в

нулевом состоянии, т. е. с их выходов, подключенных ко входам схемы совпадения 8, выдаются сигналы высокого уровня. В .результате совпадения этих сигналов на вход инвертора 9 поступает высокое напряжение, которое

открывает его, и на выходе образуется нулевой потенциал. Этот потенциал поступает на входы схем совпадения 10, 11 и препятствует прохождению импульсов от одновибраторов J2, 13, т. е. генератор заполняющих импульсов

не вырабатывает. Ключ 14, а также ключи 15 и 16 устройства 17 коррекции первого такта интегрирования закрыты. С нулевого выхода триггера 18 устройства синхронизации 19 на вход формирователя 20 устройства управлеединичного выхода этого же триггера нулевой потенциал поступает на вход схемы совпадения 21 устройства 22 формирования интервала первого такта интегрирования и препятствует прохождению через него продифференцированных импульсов от дифференцирующей цепочки 23. С выхода одновибратора 24 сигнал, равный нулю, поступает на вход схемы совпадения 25 устройства синхронизации 19 и на вход формирователя 26 устройства управления 7. Поданный на клеммы / и 2 преобразователя измеряемый сигнал подводится к фильтру 27. В результате на выходе фильтра выделяется переменная составляющая в (фиг. 2), которая is подается на вход усилителя 28. С выхода этого усилителя напряжение г поступает на дифференцирующую цепочку 23, и на ее выходе образуются импульсы д. Таким образом, на вход схемы совпадения 21 устройства 22 и на вход схемы совпадения 25 устройства синхронизации 19 лостунают импульсы с выхода дифференцирующей цепочки 23. |П0 импульсу е начала преобразования, по- 25 ступающему через клемму 29, с выхода одновибратора 24 выдается сигнал ж высокого уровня,-длительность которого превышает половину периода присутствующей помехи. Этот сигнал- разрешает прохождение -через схему зо совпадения 25 однополярного импульса, который, поступая на вход триггера 18, переводит его в состояние единицы, т. е. на вход схемы совладения 21 устройства 22 поступает снгнал и высокого уровня. В результате продиф- 35 ференцированные однонолярные импульсы с периодом, равным периоду помехи, поступают на вход пересчетного устройства 30 и подсчитываются им до тех пор, пока число в пересчетном устройстве не станет равным заранее 40 .заданной величине. В тот же самый момент . изменение состояния триггера 18 приводит к тому, что формирователь 20 устройства управления 7 выдает импульс, по которому триггер . 4 переходит в состояние «единица, а на его 45 единичном выходе появляется сигнал /с высокого уровня, который открывает ключ 3. Нулевой выход этого триггера запускает одновибратор 12 через схему «ИЛИ 31 и образует на выходе схемы совпадения 8 сигнал, равный 50 нулю, который, попадая на вход инвертора 9, закрывает его. Образовавшееся на выходе инвертора высокое напряжение, попадая на входы схем совпадения 10 и 11, разрешает прохождение через них выходных импульсов от 55 .одновибраторов 12 и 13. В результате этого генератор заполняющих импульсов начинает работать. Импульсы л с его выхода поступают на счетный вход счетчика 32 и параллельно через схему «ИЛИ - на вход одновибратора 18. На выходе интегратора напряжение б начинает возрастать. Счетчик 32 подсчитывает им1пульсы заданного интервала первого такта интегрирования. 5 10 20 60 При приеме определенного числа продифференцированных однополярных импульсов, число которых кр.атно периоду сигнала помехи, пересчетное устройство 30 выдает сигнал малой длительности, по которому открывается ключ 15 устройства 17, и входной уровень передается для запоминания в ячейку 33. По этому же сигналу триггер 4 переключается в нулевое состояние, а триггер 6 - в состояние «единица. Высокий потенциал м на единичном выходе последнего открывает ключ 16, и ячейка 33, хранящая значение аналоговой величины, подключается ко входу интегратора. Таким образом продолжается первый такт интегрирования коррекцией от измеряемого сигнала. При заполнении счетчика 32 он выдает сигнал, IHO которому триггер 5 переводится в нулевое состояние, а триггер б - в состояние «единица, и высокое напряжение н на его единичном выходе открывает ключ 14, подключая тем самым ко входу интегратора постоянный эталонный уровень. С этого момента начинается второй такт интегрирования, а напряжение б по линейному закону снижается до нуля. Триггер 6 своим нулевым выходом удерживает инвертор 9 в закрытом состоянии, .а генератор заполняющих импульсов продолжает работать. Счетчик 32 подсчитывает число импульсов за период второго такта интегрирования. В момент, когда напряжение на выходе интегратора становится равным нулю, компаратор 34 выдает сигнал о, по которому триггеры 18 и 6 устанавливаются в исходное состояние (нулевое), а генератор прекращает работу в результате появления нулевого потенциала на выходе инвертора 9. Результат преобразования в цифровом коде выдается с выхода счетчика 32. При отсутствии помехи на входном сигнале преобразование .начинается по команде, поступающей через клемму 29. С приходом импульса начала преобразования срабатывает одновибратор 24, и на его выходе появляется сигнал высокого уровня. После возвращения одновибратора в исходное состояние формирователь 26 устройства управления 7 выдает импульс, по которому триггер 4 переключается в состояние «единица. Сигнал высокого уровня единичного выхода триггера 4 открывает ключ 3, который подключает измеряемое напряжение ко входу интегратора. Изменение потенциала на нулевом выходе триггера 4 приводит к закрыванию инвертора 9 аналогично тому, как было описано ранее, и к запуску одновибратора 12. Генератор заполняющих импульсов начинает работать, а счетчик 32 подсчитывает импульсы интервала первого такта интегрирования. После заполнения счетчика с его выхода выдается сигнал, по которому триггер 4, переходя в исходное состояние, закрывает ключ 3, а триггер 6, переключившись в состояние «единица, открывает ключ 14, подключая тем самым ко входу интегратора постоянный этаняющих импульсов в режиме генерации. При равенстве нулю напряжения на выходе интегр.атора компаратор 34 выдает импульс окончания преобразования, который переводит триггер 6 в исходное состояние, а тот, в свою очередь, останавливает генератор подачи нулевого потенциала на входы схем совпадения W Е 11 с выхода инвертора 9 и закрывает ключ 14. Результат преобразования выдаегся с выхода счетчика 32.

Предмет изобретения

1. Аналого-цифровой преобразователь, основанный на двухтактном интегрировании и содержащий интегратор, например, выполненный на операцисниом усилителе с резистором на входе и конденсатором в цепи обратной связи, ключи для коммутации входного и эталонного напряжений, компаратор, счетчик и устройство управления, отличающийся тем, что, с целью повышения помехозащищенности с одновременным исключением влияния на точность преобразования как изменения частоты помехи, так и нестабильности частоты заполняющих импульсов, он содержит устройство синхронизации, устройство формирования интервала первого такта интегрирования, например, выполненное в виде последовательно соединенных фильтра, усилителя переменного тока. Дифференцирующей цепочки, схемы совпадения и пересчетной схемы, устройство коррекции первого такта интегрирования, состоящее из ячейки запоминания аналоговой величины со входным и выходным ключами, причем два выхода устройства синхронизации подключены к двум первым входам устройства управления, третий выход -ко входу схемы совпадения, входы устройства синхронизации подсоединены первый - к шине сигнала пуска, второй - к выходу дифференцирующей цепочки устройства формирования интервала первого такта интегрирования, входы фильтра которого подключены к земляной и 15 входной клеммам преобразователя.

2. Преобразователь по п. 1, отличающийся тем, что, с целью синхронного выполнения преобразования как при наличии помехи, так и при ее отсутствии, устройство сиихронизации

0 выполнено в виде одновибратора и триггера со схемой совпадения на единичном входе, при этом вход одновибратора соединен с шиной сигнала начала .преобразования, нулевой вход триггера-с выходом компа-ратора, один

5 из входов схемы совпадения -с одним из выходов устройства формирования интервала первого такта интегрирования, нулевой выход триггера и второй вход схемы совпадения подуключены к двум входам устройства управле0 ни я.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА | 2004 |

|

RU2263300C1 |

| СПОСОБ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2354955C1 |

| ЦИФРОВОЙ ИНТЕГРИРУЮЩИЙ ВОЛЬТАМПЕРМЕТР | 1972 |

|

SU347909A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Дифференциально-трансформаторный преобразователь аналог-код | 1980 |

|

SU1005127A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1124346A1 |

| Устройство для воспроизведенияМАгНиТНОй СигНАлОгРАММы | 1979 |

|

SU801055A1 |

| Устройство для измерения рассогласования между углом и кодом | 1987 |

|

SU1411973A1 |

| Преобразователь толщины в интервал времени | 1986 |

|

SU1392345A2 |

| СЛЕДЯЩИЙ ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU434593A1 |

н о

гт

Даты

1972-01-01—Публикация