элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход инвертора является вторым выходом блока управления, а выход элемента И третьим выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный измеритель энергии одиночных импульсов | 1990 |

|

SU1721520A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU842868A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Устройство управления | 1984 |

|

SU1229721A1 |

| Цифровой измеритель мощности | 1977 |

|

SU661378A1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1037280A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU342296A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

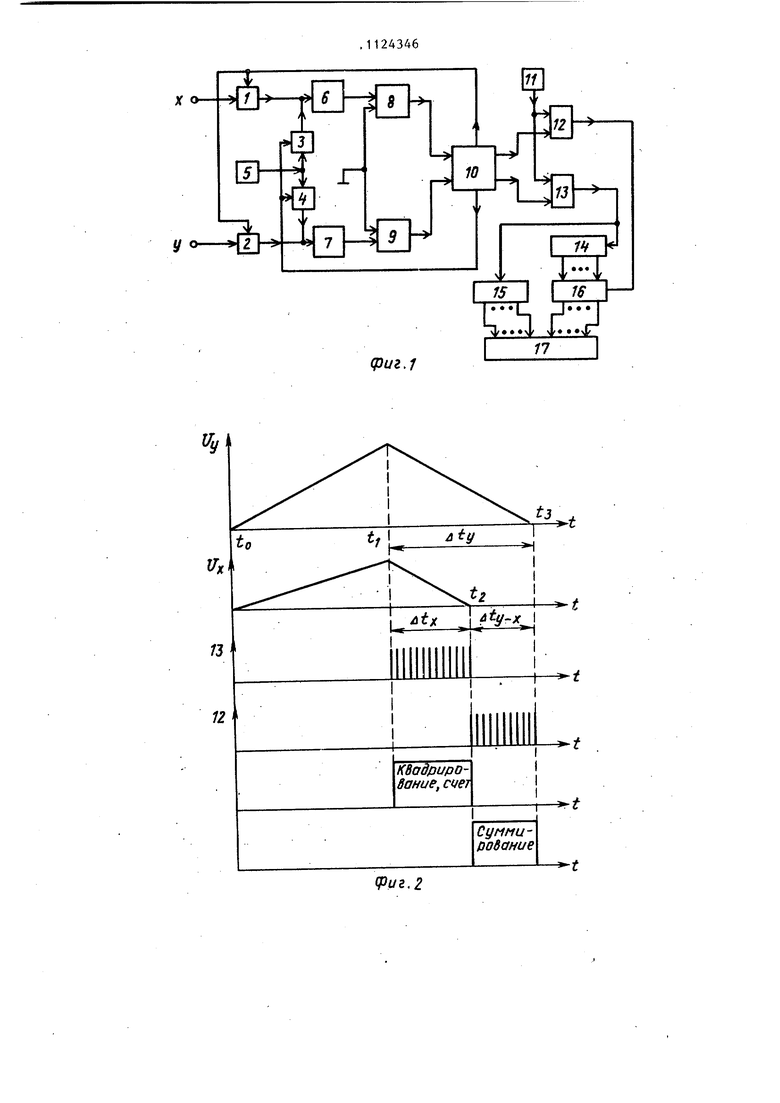

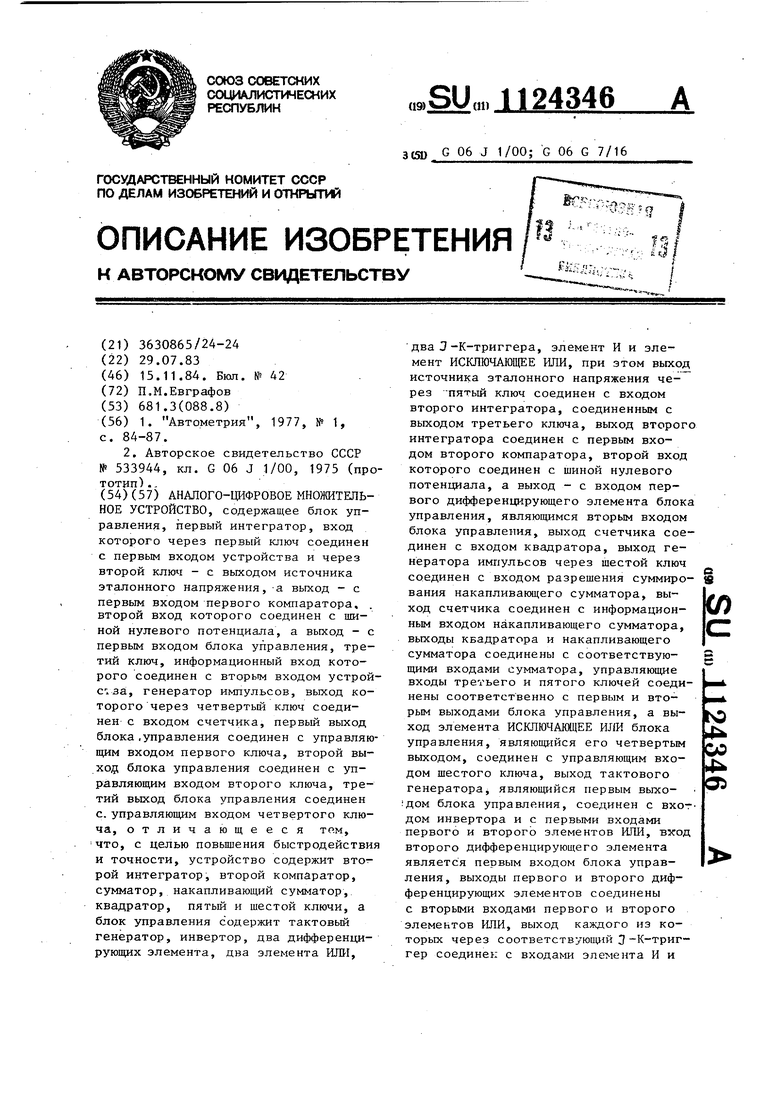

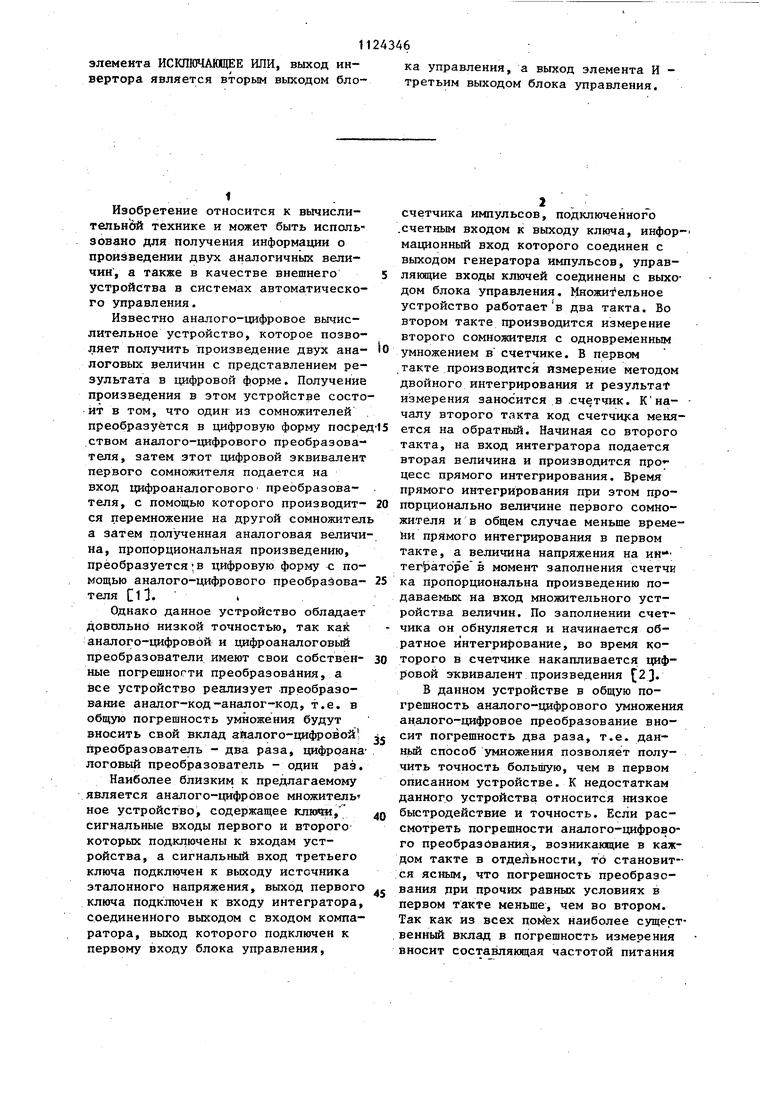

АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее блок управления, первый интегратор, вход которого через первый ключ соединен с первым входом устройства и через второй ключ - с выходом источника эталонного напряжения, -а выход - с первым входом первого компаратора, второй вход которого соединен с шиной нулевого потенциала, a выход - с первым входом блока управления, третий ключ, информационный вход которого соединен с вторьтм входом устройС1за, генератор импульсов, выход которого через четвертый ключ соединен с входом счетчика, первый выход блока.управления соединен с управляющим входом первого ключа, второй выход блока управления с-оединен с управляющим входом второго ключа, третий выход блока управления соединен с. управляющим входом четвертого ключа, отличающееся тем, ЧТО, с целью повышения быстродействия и точности, устройство содержит второй интегратор, второй компаратор, сумматор, накапливающий сумматор, квадратор, пятый и шестой ключи, a блок управления содержит тактовый генератор, инвертор, два дифференцирующих элемента, два элемента ИЛИ, два Л-К-триггера, элемент И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, при этом выход источника эталонного напряжения через ПЯТЫЙ ключ соединен с входом второго интегратора, соединенным с выходом третьего ключа, выход второго интегратора соединен с первым входом второго компаратора, второй вход которого соединен с шиной нулевого потенциала, a выход - с входом первого дифференцирующего элемента блока управления, являющимся вторым входом блока управления, выход счетчика соединен с входом квадратора, выход генератора импульсов через шестой ключ соединен с входом разрешения суммирования накапливающего сумматора, ) ход счетчика соединен с информационным входом накапливающего сумматора, выходы квадратора и накапливающего сумматора соединены с соответствующими входами сумматора, управляющие входы третьего и пятого ключей соединены соответственно с первым и вторым выходами блока управления, а выход элемента ИСКПЮЧАЩЕЕ ИЛИ блока управления, являющийся его четвертым выходом, соединен с управляющим входом шестого ключа, выход тактового генератора, являю1цийся первым выхо:дом блока управления, соединен с вхотдом инвертора и с первыми входами первого и второго элементов ШШ, вход второго дифференцирующего элемента является первым входом блока управления, выходы первого и второго дифференцирующих элементов соединены с вторыми входами первого и второго элементов ИЛИ, выход каждого из которых через соотБетствуюи1 1й 3 -К-триггер соединен с входами элемента И и

1

Изобретение относится к вычислительной технике и может быть использовано для получения информации о произведении двух аналогичных величин, а также в качестве внешнего устройства а системах автоматического управления,

Известно аналого-цифровое вычислительное устройство, которое позволяет получить произведение двух аналоговых величин с представлением результата в дафровой форме. Получение произведения в этом устройстве состоит в том, что один из сомножителей преобразуется в цифровую форму посред ством аналого-цифрового преобразова- теля, затем этот цифровой эквивалент первого Сомножителя подается на вход цифроаналогового преобразователя, с помощью которого производится перемножение на другой сомножител а затем полученная аналоговая величина, пропорциональная произведению, преобразуется;в цифровую форму с помощью аналого-цифрового преобрайователя ClL

Однако данное устройство обладает довольно низкой точностью, так кай аналого-цифровой и цифроаналоговый преобразователи, имеют свои собственные погрешности преобразования, а все устройство реализует преобразование аналог-код-аналог-код, т.е. в общую погрешность умножения будут вносить свой вклад айалого-цифровой преобразователь - два раза, цифроана логовый преобразователь - один раз.

Наиболее близким к предлагаемому является аналого-цифровое множителы нее устройство, содержащее ключи, сигнальные входы первого и второго которых подключены к входам устройства, а сигнальный вход третьего ключа подключен к вьосоду источника эталонного напряжения, выход первого ключа подключен к входу интегратора, соединенного выходом с входом компаратора, выход которого подключен к первому входу блока управления.

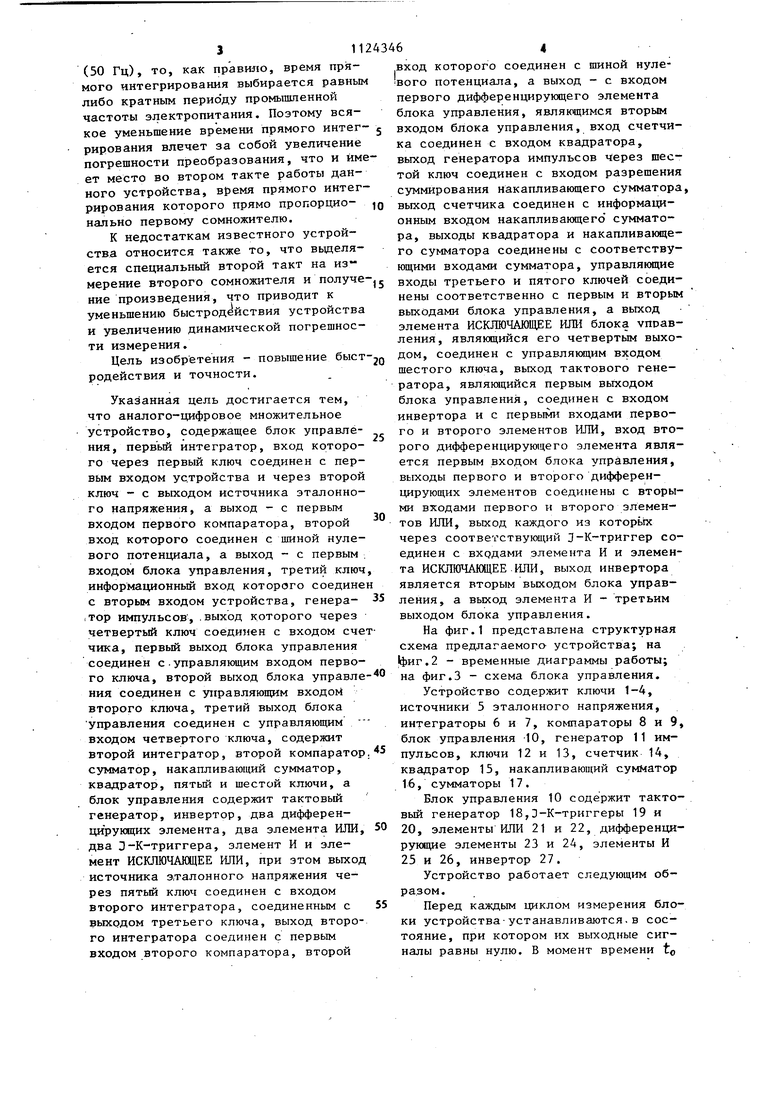

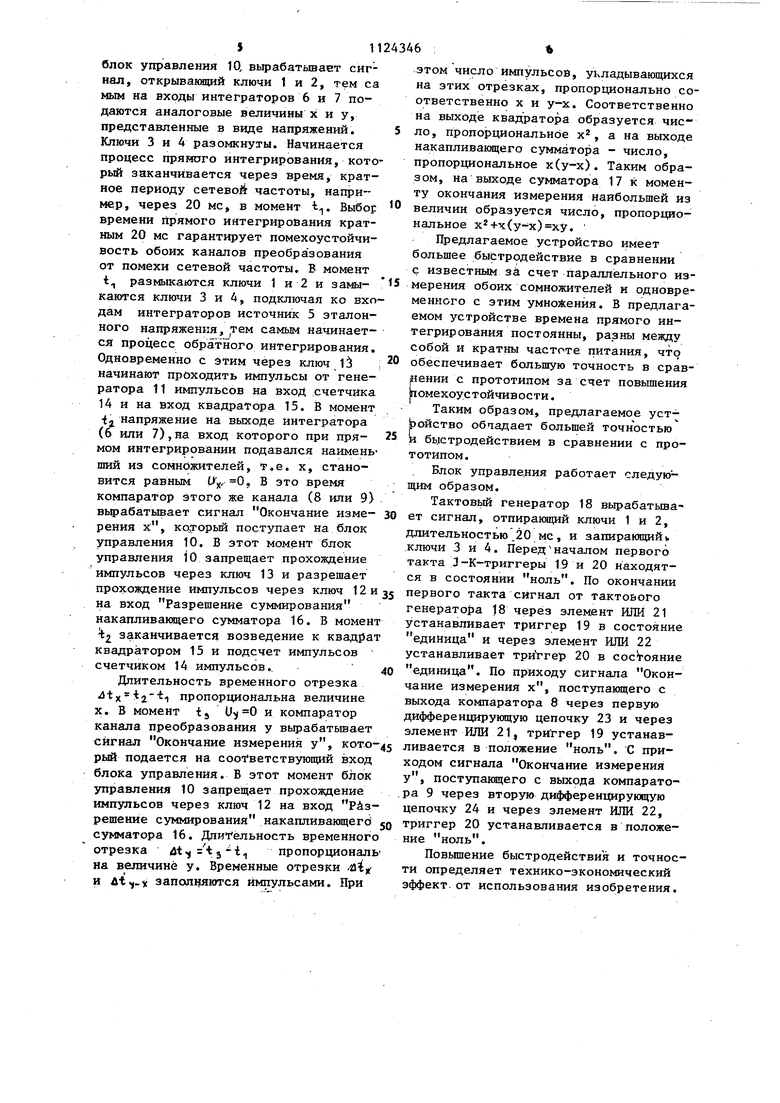

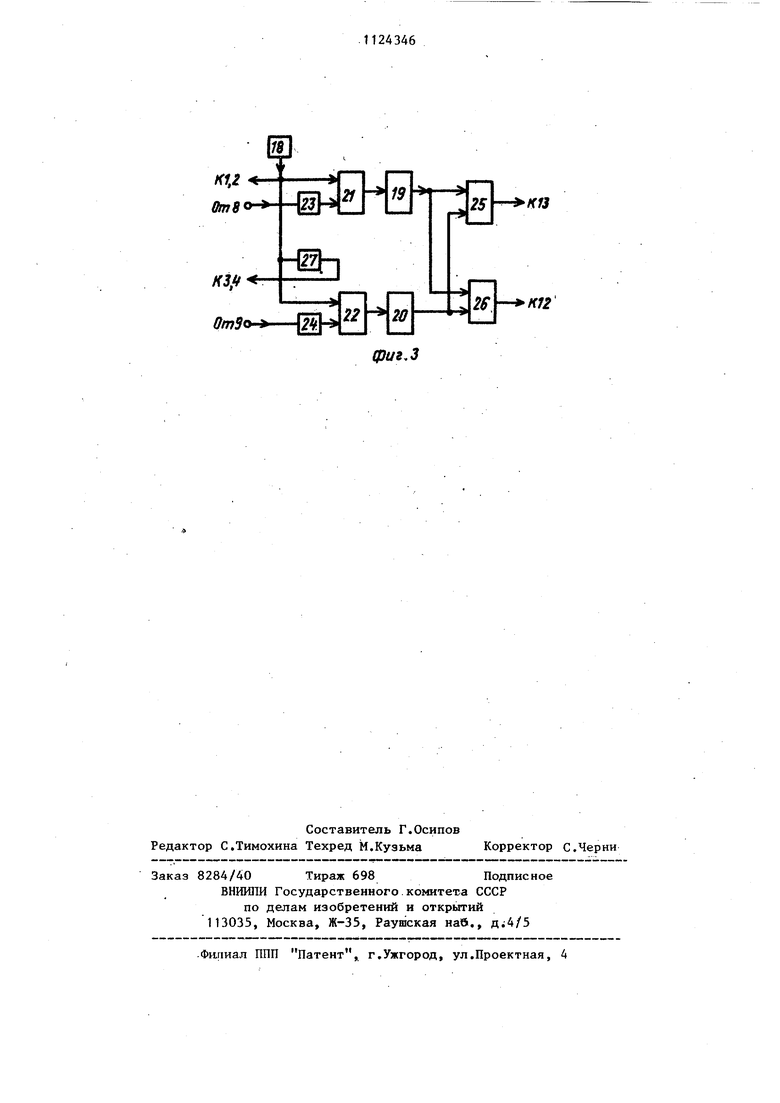

счетчика импульсов, подключенного .счетным входом к выходу клнзча, информационный вход которого соединен с выходом генератора импульсов, управляющие входы ключей соединены с выходом блока управления. Множит ельное устройство работаетв два такта. Во втором такте производится измерение второго сомножителя с одновременным умножением в счетчике. В первом такте .производится измерение методом двойного интегрирования и результат измерения заносится в .счетчик. Кначалу второго такта код счетчира меняется на обратный. Начиная со второго такта, на вход интегратора подается вторая величина и производится про цесс прямого интегрирования. Время прямого интегрирования при зтом пропорционально величине первого сомножителя ив общем случае меньше времейи прямого интегрирования в первом такте, а величина напряжения на тег4)аторе в момент заполнения счетчи ка пропорциональна произведению подаваемых на вход множительного устройства величин. По заполнении счетчика он обнуляется и начинается обратное интегрирование, во время которого в счетчике накапливается: цифровой этсвивалент произведения 2. В данном устройстве в общую погрешность аналого-цифрового умножения аналого-хщфровое преобразование вносит погрешность два раза, т.е. данный способ умножения позволяет получить точность большую, чем в первом описанном устройстве. К недостаткам данного устройства относится низкое быстродействие и точность. Если рассмотреть погрешности аналого-цифрового преобразйвания, возникающие в каждом такте в отдельности, то становится ясным, что погрешность преобразования при прочих равных условиях в первом такте меньше, чем во втором. Так как из всех помоек наиболее существенный вклад в погрешность измерения вносит составляющая частотой питания (50 Гц), то, как правюю, время прямого интегрирования выбирается равны либо кратным периоду промышленной частоты электропитания. Поэтому всякое уменьшение времени прямого интег рирования влечет за собой увеличение погрешности преобразования, что и им ет место во втором такте работы данного устройства, время прямого интег рирования которого прямо пропорционально первому сомножителю. К недостаткам известного устройства относится также то, что вьзделяется специальный второй такт на измерение второго сомножителя и получ ние произведения, что приводит к уменьшению быстродействия устройств и увеличению динамической погрешнос ти измерения. Цель изобретения - повышение быс родействия и точности. Указанная цель достигается тем, что аналого-цифровое множительное устройство, содержащее блок управле„ния, первьш интегратор, вход которого через первый ключ соединен с первым входом устройства и через второй ключ - с выходом источника эталонного напряжения, а выход - с первым входом первого компаратора, второй вход которого соединен с шиной нулевого потенциала, а выход - с первым входом блока управления, третий ключ информационный вход которого соедине с вторым входом устройства, генератор импульсов,.выход которого через четвертый ключ соединен с входом сче чика, первый выход блока управления соединен с.управляющим входом первого ключа, второй выход блока управле ния соединен с управляющим входом второго ключа, третий выход блока управления соединен с управляющим входом четвертого ключа, содержит второй интегратор, второй компаратор сумматор, накапливающий сумматор, квадратор, пятый и шестой ключи, а блок управления содержит тактовый генератор, инвертор, два дифференцирующих элемента, два элемента ИЛИ, два Э-К-триггера, элемент И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, при этом выход источника Э|Талонного напряжения через пятый ключ соединен с входом второго интегратора, соединенным с выходом третьего ключа, выход второго интегратора соединен с первым входом второго компаратора, второй 1 64 вход которого соединен с шиной нулевого потенциала, а выход - с входом первого дифференцирующего элемента блока управления, являющимся вторым входом блока управления, вход счетчика соединен с входом квадратора, выход генератора импульсов через шестой ключ соединен с входом разрешения суммирования накапливающего сумматора, выход счетчика соединен с информационным входом накапливающего сумматора, выходы квадратора и накапливающего сумматора соединены с соответствующими входами сумматора, управляющие входы третьего и пятого ключей соединены соответственно с первым и вторым выходами блока управления, а выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ блока управления, являющийся его четвертым выходом, соединен с управляющим входом шестого ключа, выход тактового генератора, являющийся первым выходом блока управления, соединен с входом инвертора и с первым11 входами первого и второго элементов ИЛИ, вход второго дифференцирующего элемента является первым входом блока управления, выходы первого и второго дифференцирующих элементов соединены с вторыми входами первого и второго элементов ИЛИ, выход каждого из которьЬс через соответствукнций 3-К-триггер соединен с входами элемента И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход инвертора является вторым выходом блока управления, а выход элемента И - третьим выходом блока управления. На фиг.1 представлена структурная схема предлагаемого устройства; на 1ФИГ.2 - временные диаграммы работы; на фиг.З - схема блока управления. Устройство содержит ключи 1-4, источники 5 эталонного напряжения, интеграторы 6 и 7, коьтараторы 8 и 9, блок управления 10, генератор 11 импульсов, ключи 12 и 13, счетчик 14, квадратор 15, накапливающий сумматор 16, сумматоры 17. Блок управления 10 содержит тактовый генератор 18,3-К-триггеры 19 и 20, элементы ИЛИ 21 и 22, дифференцирующие элементы 23 и 24, элементы И 25 и 26, инвертор 27. Устройство работает следующим образом. Перед каждым циклом измерения блоки устройства-устанавливаются.в состояние, при котором их выходные сигналы равны нулю. В момент времени to S11 блок управления 1Q вьфабатьшает сигнал, открываниций ключи 1 и 2, тем са мым на входы интеграторов 6 и 7 подаются аналоговые величины х и у, представленные в виде напряжений. Ключи 3 и 4 разомкнуты. Начинается процесс пряного интегрирования, который заканчивается через время, кратное периоду сетевой частоты, напри мер, через 20 мс, в момент Ц. Выбор времени прямого интегрирования кратным 20 мс гарантирует помехоустойчивость обоих каналов преобразования от помехи сетевой частоты, В момент t размыкаются ключи 1 и 2 и замыкаются ключи 3 и 4, подключая ко входам интеграторов источник 5 эталонного напряжения, тем самьм начинается процесс обратного интегрирования. Одновременно с этим через ключ 13 начинают проходить импульсы от генератора 11 импульсов на вход счетчика 14 и на вход квадратора 15, В момент tJ напряжение на выходе интегратора (6 или 7),на вход которого при прямом интегрировании подавался найменьший из сомножителей, т.е, х, стано вится равным U, 0, В это время компаратор этого же канала (8 или 9) вьфабатывает сигнал Окончание изме- рения х, ко,торый поступает на блок управления 10, В этот момент блок управления 10 запрещает прохождение импульсов через ключ 13 и разрешает прохождение импульсов через ключ 12 и на вход Разрешение суммирования накапливакйдего сумматора 16, В момент % заканчивается возведение к квадрат квадратором 15 и подсчет импульсов счетчиком 14 импульсов,. Длительность временного отрезка пропорциональна величине X. В момент tj и компаратор канала преобразования у вырабатьшает сигнал Окончание измерения у , кото рый подается на соответствующий вход блока управления, В этот момент блок управления 10 запрещает прохождение импульсов через ключ 12 на вход РАз решение суммирования накапливающего сумматора 16, Длительность временног отрезка Jt- з i пропорционал на величине у. Временные отрезки и At.y заполняются импульсами. При 6 этом число импульсов, укладывающихся на этих отрезках, пропорционально соответственно X и у-х. Соответственно на выходе квадратора образуется число , пропорциональное х, а на выходе накапливающего сумматора - число, пропорциональное х(у-х). Таким образом, на выходе сумматора 17 к моменту окончания измерения наибольшей из величин образуется число, пропорциональное ()ху, Предлагаемое устройство имеет большее быстродействие в сравнении с известным за счет параллельного измерения обоих сомножителей и одновременного с этим умножения, В предлагаемом устройстве времена прямого интегрирования постоянны, разны между собой и кратны частоте питания, что обеспечивает большую точность в сравнении с прототипом за счет повышения помехоустойчивости. Таким образом, предлагаемое уст)ройство обаадает большей точностью и быстродействием в сравнении с прототипом. Блок управления работает следующим образом. Тактовый генератор 18 вырабатьшает сигнал, отпиракиций ключи 1 и 2, длительностью .20 мс, и запирающий v ключи 3 и 4, Перед началом первого такта 3-К-триггеры 19 и 20 находятся в состоянии ноль. По окончании первого такта сигнал от тактового генерато1)а 18 через элемент ИЛИ 21 устанавливает триггер 19 в состояние единица и через элемент ИЛИ 22 устанавливает триУгер 20 в сосгояние единица. По приходу сигнала Окончание измерения х, поступающего с выхода компаратора 8 через первую дифференцирукицую цепочку 23 и через элемент ИЛИ 21, триГггер 19 устанавв положение ноль , С приливаетсяходом сигнала Окончание измерения у, поступающего с выхода компаратора 9 через вторую дифференцирующую цепочку 24 и через элемент ИЛИ 22, триггер 20 устанавливается в положение ноль, Повьш1ение быстродействия и точности определяет технико-экономический эффект.от использования изобретения.

/7

(риг.

72

KBaapupoBoHue, CQCi

CyiiMu{зоВание

t

9иг,2

J

/f«

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Автометрия, 1977, № 1, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1921 |

|

SU84A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аналого-цифровое множительное устройство | 1975 |

|

SU533944A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-15—Публикация

1983-07-29—Подача