Предлагаемый магнитный накопитель информации предназначен для использования в запоминающих устройствах (ЗУ) с целью хранения двоичной информации.

Известен накопитель ЗУ, который набирается из отдельных матриц, элементы памяти которых выполнены из коммутирующих и запоминающих сердечников, охваченных резистивным витком связи, причем коммутирующий сердечник пронизан обмотками смещения, опроса и записи и запоминающей-выходной обмоткой.

Недостатком такого накопителя является то, что при обращении к ЗУ происходит динамическое изменение тока в обмотке смещения за счет индуктивной связи между обмоткой смещения и обмотками опроса и записи. Так, например, при считывании и при небольшом объеме накопителя (индуктивность невозбужденных элементов памяти будет при этом мала) и малом активном сопротивлении цепи обмотки смещения происходит уменьшение амплитуды выходного сигнала считанной «единицы и увеличение времени выборки числа из накопителя, а в момент записи числа при малом активном сопротивлении цепи обмотки смещения и при большом объеме накопителя может происходить увеличение тока смещения, так как большое количество коммутирующих сердечников будет полувозбуждено. Это

оказывает сильное влияние на время записи единичной информации, т. к. коммутирующий сердечник переключается в более слабых полях. В этом случае, в зависимости от записываемой информации, время записи будет нестабильным.

Кроме того, ухудшаются условия записи единичной информации, т. к. в момент записи ток смещения увеличивается.

Таким образом, из-за размагничивающего действия обмотки смещения надежность работы накогштеля уменьшается и увеличивается цикл обращения к ЗУ.

Известен также накопитель, в котором, с целью устранения индуктивной связи обмотками смещения и опроса, в одной половине опрашиваемых сердечников обмотки опроса и смещения включены согласно, а в другой-встречно.

Однако такой способ включения увеличивает вдвое объем накопителя по сравнению с необходимым и вдвое возрастает индуктивная нагрузка на элементы адресной части ЗУ. Кроме того, такой способ не дает полной компенсации э. д. с., наведенной на обмотке смещения от обмотки опроса, за счет того, что в одной половине опрашиваемых сердечников происходит намагничивание, а в другой половине-размагничивание.

В предлагаемом накопителе увеличение быстродействия и повышение надежности достигается тем, что первая обмотка смещения первой матрицы соединяется последовательно и согласно со второй обмоткой смещения второй матрицы, вторая обмотка смещения второй матрицы-с первой обмоткой смещения третьей матрицы и т. д.; вторая обмотка смещения первой матрицы соединяется последовательно и согласно с первой обмоткой смещения второй матрицы, первая обмотка смещения второй матрицы-со второй обмоткой смещения третьей матрицы и т. д.; входы обмоток смещения подключены к двум формирователям постоянного тока, выполненным по схеме с общей базой, а выходы обмоток смещения последней матрицы-соответственно согласно и встречно к двум обмоткам трансформатора.

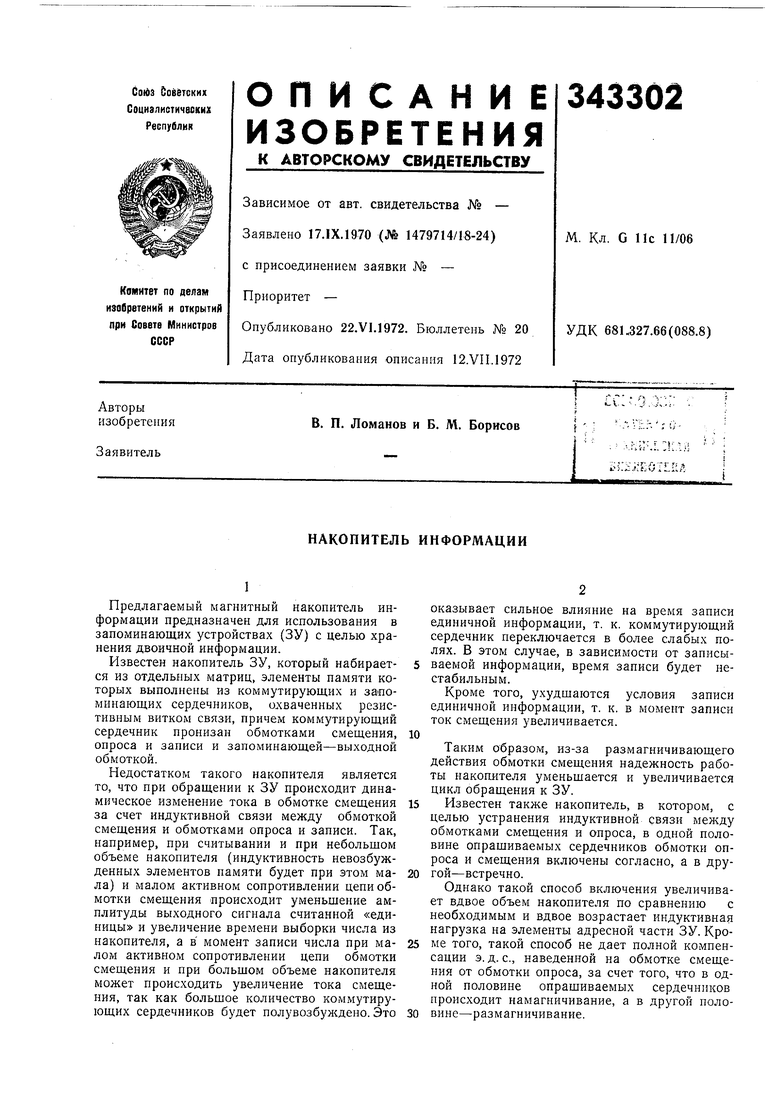

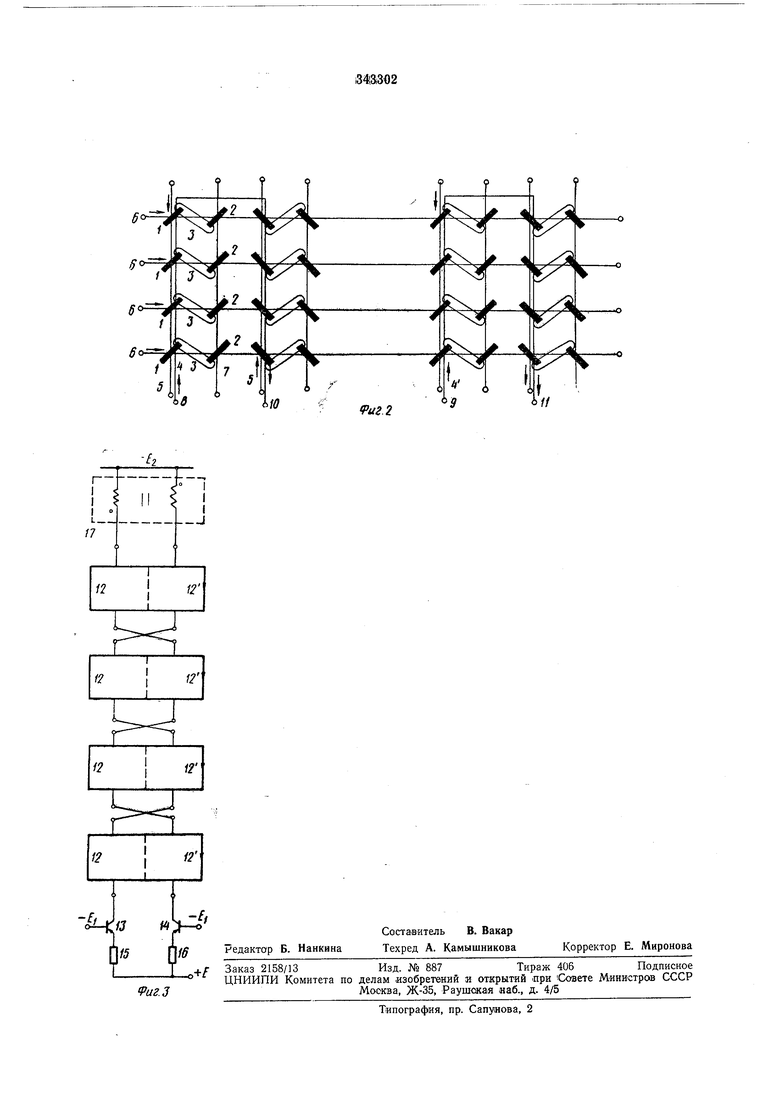

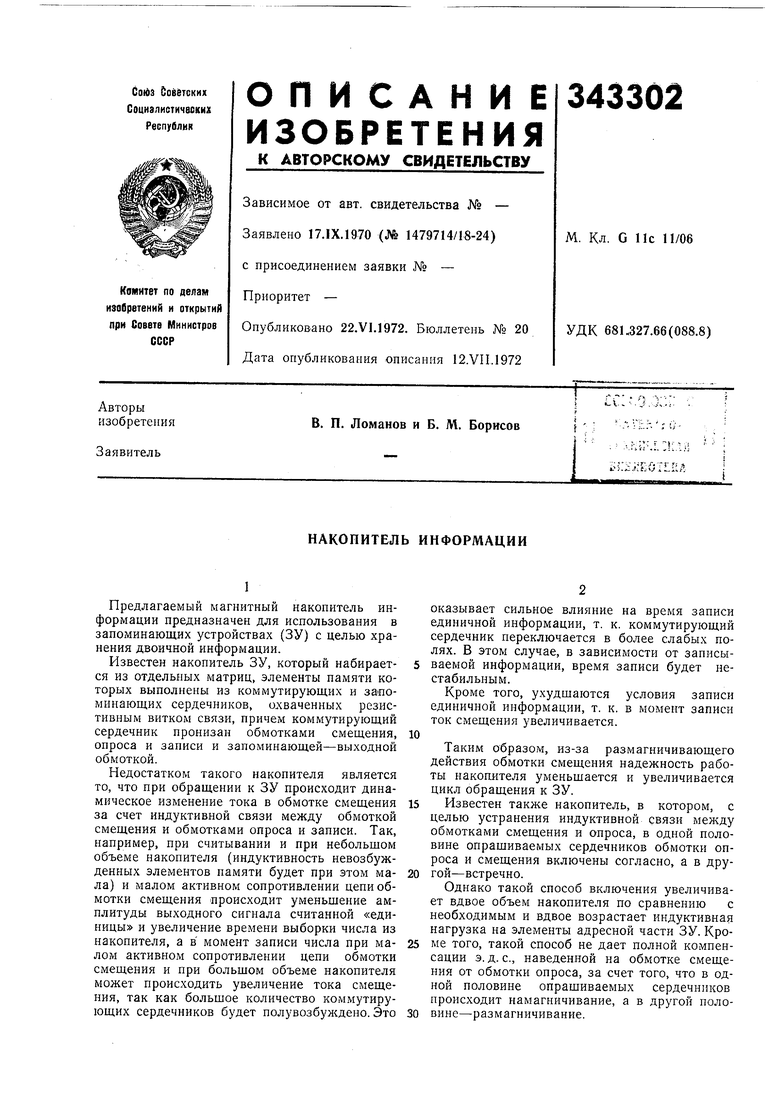

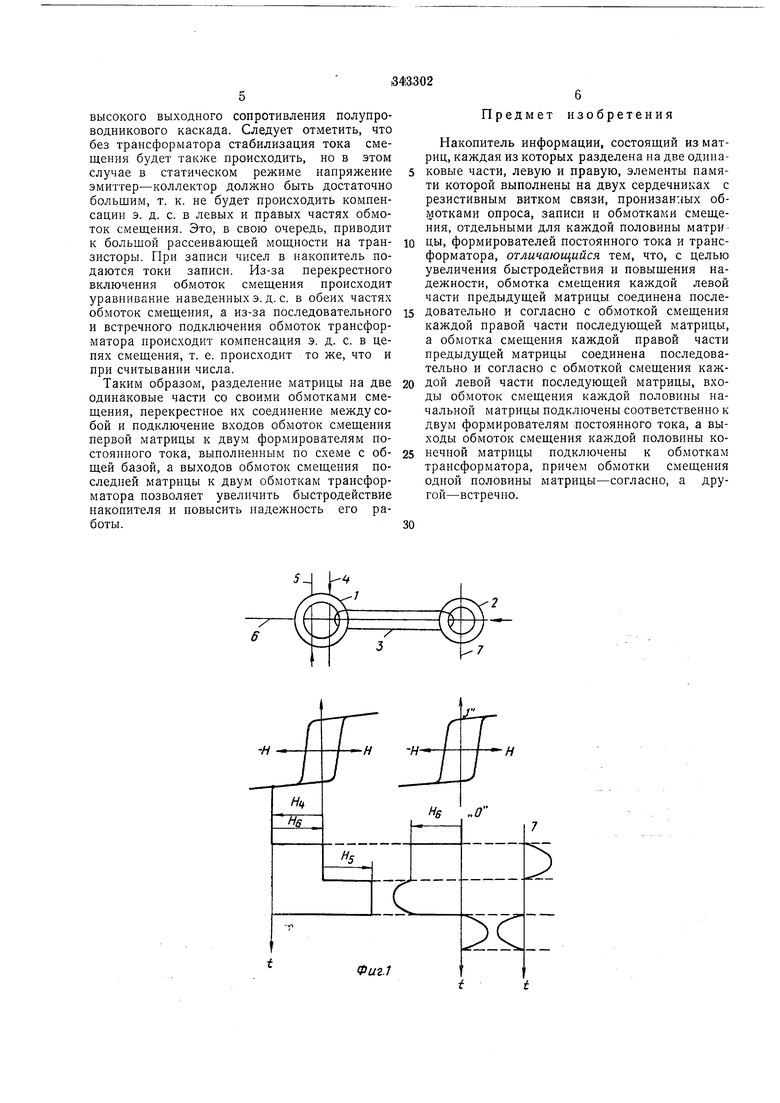

На фиг. 1 изображен элемент памяти и временная диаграмма его работы; на фиг. 2- матрицы накопителя; на фиг. 3- предлагаемый накопитель.

Элемент памяти (фиг. 1) состоит из коммутирующего 1 и запоминающего 2 сердечников, охваченных витком. Через коммутирующий сердечник 1 проходят обмотки смещения 4, записи 5 и опроса 6, а через запоминающий 2-обмотка опроса 6 и выходная обмотка 7.

Элемент памяти работает следующим образом.

В исходном состоянии сердечник 1 намагничен постоянным током обмотки смещения 4. При появлении тока в обмотке опроса происходит переключение запоминающего сердечника из состояния «1, если в нем была запись «1, в состояние «О. При этом на выходной обмотке 7 появляется сигнал считанной «единицы. При записи «единицы в обмотку записи 5 подают ток, и переключается коммутирующий сердечник 1. При этом наведенный в витке связи 3 ток сильнее насыщает запоминающий сердечник в состоянии «нуля.

При спадении токов записи и опроса под действием тока смещения происходит возврат коммутирующего сердечника в исходное состояние. При этом в витке связи 3 появляется ток, который переключает запоминающий сердечник 2 в состояние «единицы. При записи «нуля ток записи не подается.

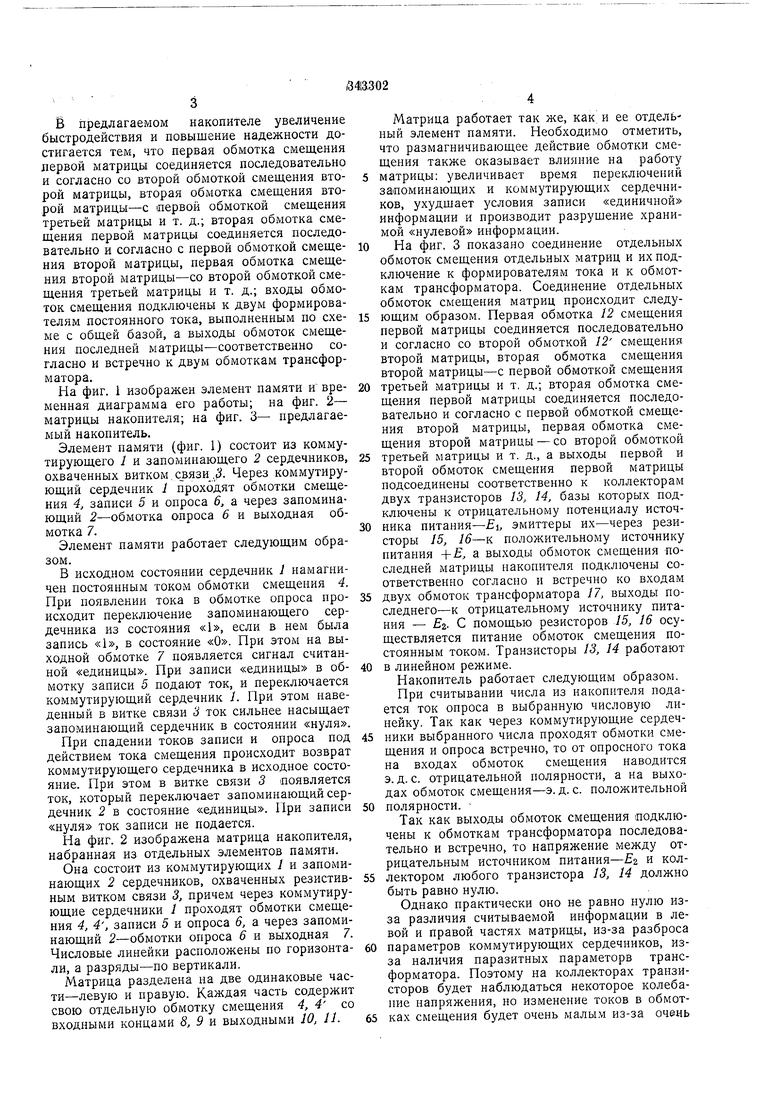

Па фиг. 2 изображена матрица накопителя, набранная из отдельных элементов памяти.

Она состоит из коммутирующих 1 и запоминающих 2 сердечников, охваченных резистивным витком связи 3, причем через коммутирующие сердечники / проходят обмотки смещения 4, 4, записи 5 и опроса 6, а через запоминающий 2-обмотки опроса 6 и выходная 7. Числовые линейки расположены по горизонтали, а разряды-по вертикали.

Матрица работает так же, как и ее отдельный элемент памяти. Необходимо отметить, что размагничивающее действие обмотки смещения также оказывает влияние на работу матрицы: увеличивает время переключений запоминающих и коммутирующих сердечников, ухудшает условия записи «единичной информации и производит разрушение хранимой «нулевой информации.

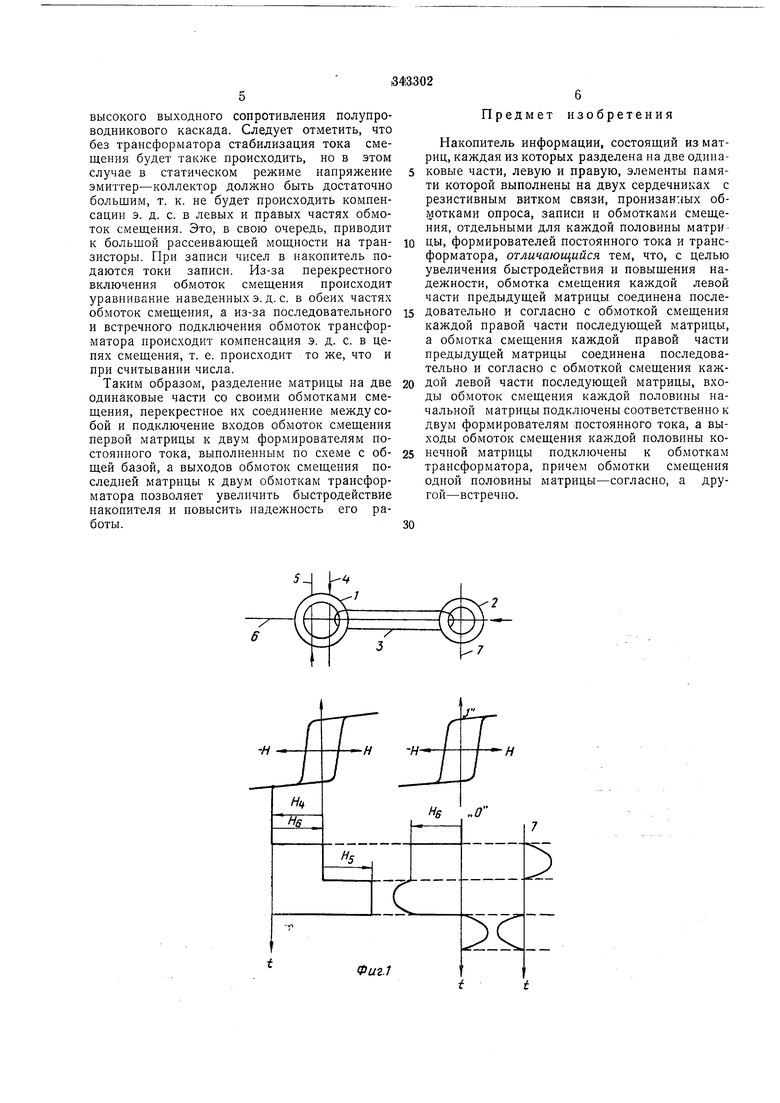

На фиг. 3 показано соединение отдельных обмоток смещения отдельных матриц и их подключение к формирователям тока и к обмоткам трансформатора. Соединение отдельных обмоток смещения матриц происходит следующим образом. Первая обмотка 12 смещения первой матрицы соединяется последовательно и согласно со второй обмоткой 12 смещения второй матрицы, вторая обмотка смещения второй матрицы-с первой обмоткой смещения

третьей матрицы и т. д.; вторая обмотка смещения первой матрицы соединяется последовательно и согласно с первой обмоткой смещения второй матрицы, первая обмотка смещения второй матрицы - со второй обмоткой

третьей матрицы и т. д., а выходы первой и второй обмоток смещения первой матрицы подсоединены соответственно к коллекторам двух транзисторов 13, 14, базы которых подключены к отрицательному потенциалу источника питания--Ei, эмиттеры их-через резисторы 15, 16-к положительному источнику питания , а выходы обмоток смещения последней матрицы накопителя подключены соответственно согласно и встречно ко входам

двух обмоток трансформатора 17, выходы последнего-к отрицательному источнику питания - EZ. С помощью резисторов 15, 16 осуществляется питание обмоток смещения постоянным током. Транзисторы 13, 14 работают

в линейном режиме.

Накопитель работает следующим образом. При считывании числа из накопителя подается ток опроса в выбранную числовую линейку. Так как через коммутирующие сердечНИКИ выбранного числа проходят обмотки смещения и опроса встречно, то от опросного тока на входах обмоток смещения наводится э. д. с. отрицательной полярности, а на выходах обмоток смещения-э. д. с. положительной

полярности. Так как выходы обмоток смещения подключены к обмоткам трансформатора последовательно и встречно, то напряжение между отрицательным источником питания-EZ и коллектором любого транзистора 13, 14 должно быть равно нулю.

Однако практически оно не равно нулю изза различия считываемой информации в левой и правой частях матрицы, из-за разброса

высокого выходного сопротивления полупроводникового каскада. Следует отметить, что без трансформатора стабилизация тока смещения будет также происходить, но в этом случае Б статическом режиме напряжение эмиттер-коллектор должно быть достаточно большим, т. к. не будет происходить компенсации э. д. с. в левых и правых частях обмоток смещения. Это, в свою очередь, приводит к большой рассеивающей мощности на транзисторы. При записи чисел в накопитель подаются токи записи. Из-за перекрестного включения обмоток смещения происходит уравнивание наведенных э. д. с. в обеих частях обмоток смещения, а из-за последовательного и встречного подключения обмоток трансформатора происходит компенсация э. д. с. в цепях смещения, т. е. происходит то же, что и при считывании числа.

Таким образом, разделение матрицы на две одинаковые части со своими обмотками смещения, перекрестное их соединение между собой и подключение входов обмоток смещения первой матрицы к двум формирователям постоянного тока, выполненным по схеме с общей базой, а выходов обмоток смещения последней матрицы к двум обмоткам трансформатора позволяет увеличить быстродействие накопителя и повысить надежность его работы.

Предмет изобретения

Накопитель информации, состоящий из матриц, каждая из которых разделена на две одинаковые части, левую и правую, элементы памяти которой выполнены на двух сердечниках с резистивным витком связи, пронизан:{ых обмотками опроса, записи и обмотками смещения, отдельными для каждой половины матри

цы, формирователей постоянного тока и трансформатора, отличающийся тем, что, с целью увеличения быстродействия и повыщения надежности, обмотка смещения каждой левой части предыдущей матрицы соединена последовательно и согласно с обмоткой смещения каждой правой части последующей матрицы, а обмотка смещения каждой правой части предыдущей матрицы соединена последовательно и согласно с обмоткой смещения каждой левой части последующей матрицы, входы обмоток смещения каждой половины начальной матрицы подключены соответственно к двум формирователям -постоянного тока, а выходы обмоток смещения каждой половины конечной матрицы подключены к обмоткам трансформатора, причем обмотки смещения одной половины матрицы-согласно, а другой-встречно.

30

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОБРАЩЕНИЯ К ЗАПОМИНАЮЩЕМУ УСТРОЙСТВУ | 1973 |

|

SU373762A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| Накопитель | 1979 |

|

SU803008A1 |

| Запоминающее устройство с сохранением информации при аварийном отключении питания | 1977 |

|

SU693441A1 |

| Запоминающее устройство на ферри-ТОВыХ СЕРдЕчНиКАХ C МОдуляциЕй МАг-НиТНОгО СОпРОТиВлЕНия | 1979 |

|

SU841040A1 |

| Накопитель для трансформаторного запоминающего устройства | 1975 |

|

SU628534A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| АССОЦИАТИВНО-АДРЕСНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU336697A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU254205A1 |

| Устройство для отображения информации | 1979 |

|

SU842938A1 |

н

ф

6

Pu22

Даты

1972-01-01—Публикация