iPi/3ioi6pjereH,Hie (ТСя к oiблa cти ВЫЧ,И|СЛ1Ителъиой тех ни1ки и может |быть использовано, |наотрИ1М(ер, IB зайомииающий у€троЙ1СТ1вах (ЗУ).

Иавестиы затйминающие устройства, сюдержащие мно1гопозид1ионну1ю матрицу, управляемую четьирехйоордИНатной системой дешифрации, и разрядные устройства записи.

.Не1достатка.МИ изиествых устройств являются большое колличество требуемого оборудования и невысокая надежиость.

Предлагаемое устройство отлич,ается тем, что каждая 1-я выходная шина первого дешифратора через ключ соединена с обш,ей шиной, объединяющей катоды одной грунты диодов, а1НОДы которых С|оеди1Не;ны с коллекторами транзисторов t-й строки и с первым входо,м первичных обмоток траисфор-матора ехем совпадения, L-Я выгодная шмиа второ ло дешИ|фрато1ра i4jepe3 электрО|Н«ый ключ иодсо,еди1неиа к общей шиие, объедиияю.щей аиоды друпой группы диодов, .катоды которых соединеЩЫ с эмиттер,а1ми тра НЗИСтор|ОВ электронных ключей t-й строки и со входами вторых первич1ны,х обмоток трансфор1матор01В cxjeiM совладения этой строки:, а каждая разРядная шина регистра числа соединена со в,ходам,и двух со.гл а сующих схем «И, выходы которых соединены соответственно со IBTOрыми входами первой и второй обмоток

траиоформаторов схем совладения злектроийых ключей /-Й од1ностол|бцовой матрицы записи.

Это позволяет устранить недостатки прототииа.

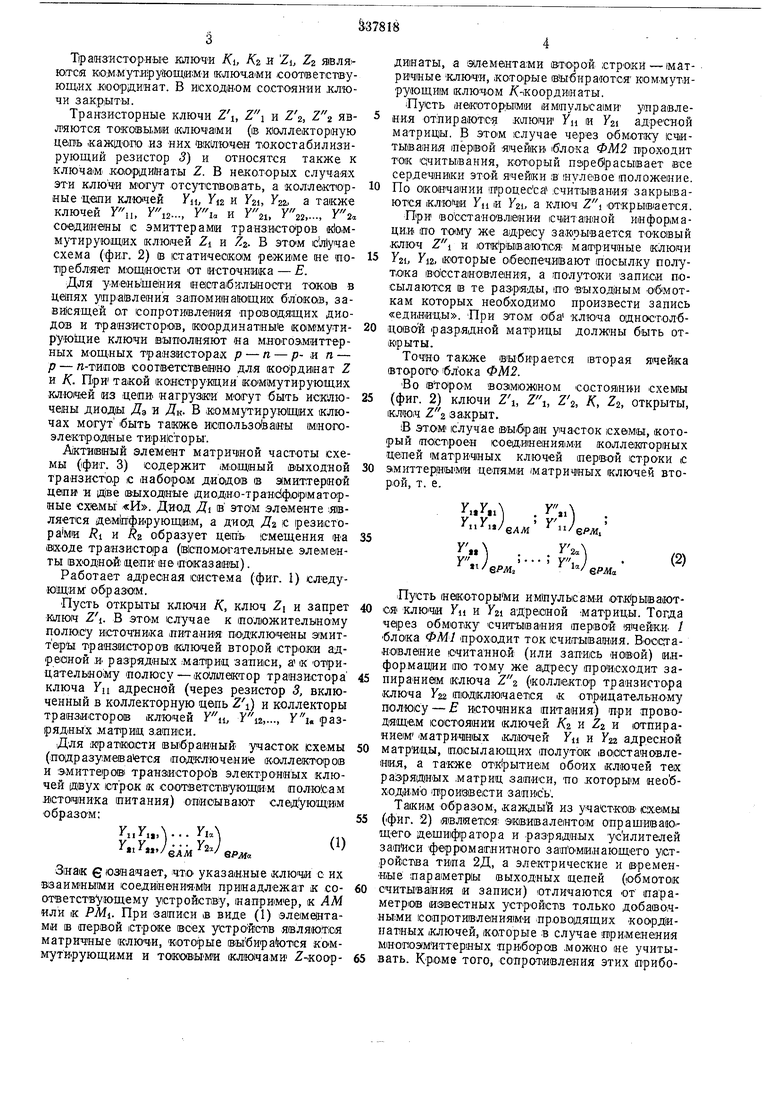

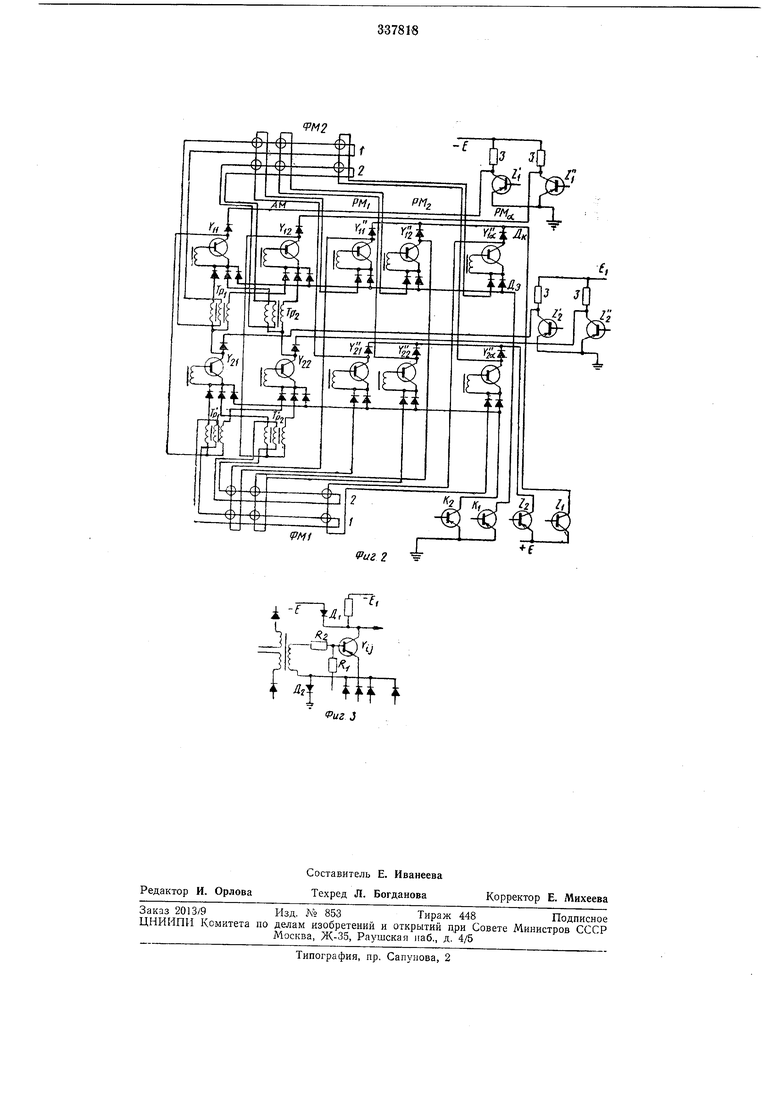

На фиг. 1 приведена функниюналыная схема адресной системы для накопителя с двумя модулями (), 1на фиг. 2 дана принципиальная электрическая схема, Илдюстрирующая принцип работы двухпозиционной диоДно-трансформаторной матрицы, на фиг. 3 приведена прииципиалыиая схе:ма элемента (ключ1а, усилителя мощности) .матрицы - (Матричнопо ключа.

Адресная сиСтема ЗУ содержит миогопозиционную диодно-транофорМлтериую матрицу с Д1вух1поля)р1ным выходным током AM (адресная матрица) и некоторое число одиостолбидовых () разридиых матриц ЯЛ1ь РМз,...,

РМ .

Система содержит N участков, N m (), каждый из которы.х выполняет фуниции опрашивающего устройства и раЗр|яд№Ы|Х усилителей записи для соответствующего блока.

Запоминающие блоки (фиг. 2) адре;сн10Й систе1мы представляют собой две (ферритовые матрицы ФМ1 и ФМ2. ;Каждый блок содержит две ячейки (два адреса) / и 2 ос-разрядТранзисторные ключи Ki, Kz и Zz являЮ;ТСЯ К|0;М.(ЮЩ И;МИ ключами соответствующлх координат. В исходн-ом состоянии ключи закр,ытЫ.

Транзисторные ключи Zl, Z и Zz, 2 являются то1ковы,м(и (Ключами (IB иоллекториую цегрь .кажДОШ из них 1В1КйюЧ|ея токостабнлизирующий резистор 3} и относятся также к ключам, коорьцийаты Z. В некоторых случаях эти ключи могут отсут СТ1В01вать, а коляектюрные Цепи ключей Уи, г и F2i, Угг, а также

ключей У,ь ..., и , ,..., .

со«1ди еяы с эмиттерами транзисторов Коммутирующих ключей Zi и 2. В этоМ сЫучае схема (фиг. 2) в статическом режиме ие пот|ребля:ет мощности от источника - Е.

Для уме1НЬше1ния ее1ста|билыности токов в цейях у1пра1вления заиоминающик блоков, зависящей от сопротишления прово1дящих диодов и транзисторов, координатные ко мзмутируюЁцие ключи выполняют на многозмиттерных мощных транзисторах р - п - р- и п - р - «-типов соответствеино для координат Z и к. При такой конструкция коммутирующих клютей из щеп иагрузки могут быть исключены диоды Дэ и Дк- В коммутирующих ключах могут быть такжв июпользованы многоэлектродные тирн1сторы.

Активный элемент матричной частоты схемы (фиг. 3) содержит мощный выходной транзистор с набором диодов IB эмиттерной деии и 1щве выходные iциoдlнo-тpaнldфl0iplмaтo pные схемы «И. Диод Д1 в этом элементе является дем1п ф.и.рующи1м, а диод иг iC резвсторами 1 и 2 образует цепь |смещения вкоде транзисто1ра (в1спомогатеЛЬ1Ные элементы входнОЙ щепи не Яоказаеы).

Работает адресная система (фиг. 1) слвдующим образом.

Пусть открыты ключи к, ключ Z и запрет ключ Zl. В этом случае к иолюжителыному полюсу источника литания подключены эмиттеры транзисторов ийлючей второй 1стр|0:ки адреюной и разрядных матриц запи си, а к от1рицательно му полюсу - «олиектор транзистора ключа УП адресной (через резистор 5, включенный в коллекторную цепь Zj) и коллекторы транзисторов ключей , ylz,.-, Уь разрядных матриц з.аписи.

Для мраткости выбранный участок схемы (подразуМевается подключение коллекторов и эмиттеров TpaH3HCTOpiOB электронных ключей двух етрок к соответствующим оолюЬам источника питания) описываю следующим образом;

УпУцЛ

-..

Знак g (Означает, что указанные ключи с их взаимными соединениями принадлежат к соответствующему устройству, напрИМер, к AM или к PJAi. При записи ъ виде (1) эламе|нтами в первой строке всех устройств я1ВляюТ С(Я матрич1ные ключи, которые выбирается коммутирующими и токовыми (Ключами Z-координаты, а элементами в.торой строки - матричные КЛЮЧИ, которые вЬгбираготся юоммутирующим ключом С-координаты.

Пусть некоторыми импульсами- управления отпираются клю1чи УЦ и У21 адресной матрицы. В этом случае через обмотку считывания 1пёрвой ячейки, блока Ф1А2 проходит TOIK считьшания, который переб расывает все сердечники этой ячейки в нулевое положение. По окончании йроцесса считывания закрываются КЛЮЧ1И УН и У21, а ключ Z открыв1ается.

При восстановлении считанной информации, по тому же адресу зак1рывается токовый .ключ и ютк рываются маггричные ключи У21, У12, которые обеспечивают посылку полутока восста1но:влани я, а по-лутоки записи посылаются в те разряды, по выходным обмоткам которых необходимо произвести запись «единицы. При этом оба ключа одностолбцовой разрядной матрицы должны быть открыты.

Точно также Выбирается вторая ячейка второГоблока ФМ2.

Во втором во31М10Ж1ном СОСТОЯ1НИ.И схемы (фиг. 2) ключи Zl, , Zs, /С, Zj, открыты, клкич закрыт.

iB ЭТОМ случае участок cxeiMw, который построен соединанияими колле1К1торных цепей матричных ключей первой стро-ки с эмиттерными цепями матрич1ных ключей второй, т. е.

иУц). - ai I

У -«Ч

У V J У j

/елл1 I/ePAi.

.... .

У Y,

вРМ, вРМа.

|Пусть некоторыми импульсами отк1рываютс ключи УИ и Уа адресной матрицы. Тогда через обмотку считывания первой ячейки. / блока ФМ1 проходит ток считывания. Воссгган.овлание 1считанно.й (или запи|СЬ новой) инфор.мацин по тому же адресу происходит запираниам ключа (коллектор транзистора Ключа У22 подключается к отрицательному полюсу - Е источника питания) при проводящем состоянии ключей Kz Zz я ютпиранием матричных ключей УИ и У22 адресной матрицы, посылающих полуток (воастановления, а также открытием, обоих ключей тек разрядных матриц записи, тго которьгм необходимо произвести запись .

Та1ким образом, каждый из участкоВ (с;хемы (фиг. 2) является: Эювивалентом опращиваю.щега дешифратора и разрядных усилителей записи ферромагнитного запоминающего устройства типа 2Д, а электрические и временны е параметры выходных цепей (обмоток считывания и записи) отличаются от параметр1ов изве стных устройств только добавочными сопротивлениями проводящих коо рдйпатных (Ключей, которые в случае применения мнолоэмиттерных приборов .можно не учитывать. Кроме того, сопротивления этих прибоpOiB- частично (вьшолняют функцию токостаби|лизирующих соиротиелееий в цепи нагрузки. В общей схбме адресной системы (фиг. 1) соединения выходных цепей с обмот.ка1ми. запО|МинаЮ|Щих блоков ие показаны. Обмотки (m- 1) запоминающих блочков, незавиоимо ;от объе1ма ячеек каждого из этих блоков, 1Сое|ДИ1Н Я1ЮТ1СЯ )С выходными цепями участков адресиой системы анало лич1но схеме фиг. 2. Положение каждого участка (каждой элементарной схемы управления) ойределяе,Т1Ся дешифраторами ДшК и Дш2 с выходными коммутирующими и токовыми ключами, а положение каждой О|5моТ1ки считывания- дешифраторами ДшХ и ДшУ. Доложение каждой обмотки записи определяется трехкоординатным способом. Третьей координатой служит выходная шина соответствующего разряда регистра числа РгЧ, которая через логические схемы «И соединена с входами .матричных ключей данной разрядной матрицы записи. Процесс (последов ательной дешифрации эле.ме1нтарных cxeiM управления и обслуживаемых ими запоминающих -блоков можно описать нулевой матрицей. При этом можно считать, что таковые ключи Zl и Z, (i 1, 2, 3,..., т со входными схемами «И, а также схемы «НЕ отсутствуют, а фуниции этих устройств выполняют коммутирующие ключи. Подобный вариант рассмотрен ниже. Если работа дешифраторов ДшК и Дш2 описывается собственными системами в виде K,a,... fC, a,,/... «1 Л а, Л .. Л а, 2. 6,Л.Л...Л 1 , 6,Л&«Л...Л&г .AVA...A&; со.ответст(ве1Н1НО, то закон фуикционирования адресной системы яри последовательной дешифр.ации схем управлении и обслуживаемых ими запоминающих «блоков имеет вид; (2ЛЮ где а , Ь -двоич1ные переметные (, 2, 3,...,/), / - разрЯ1ДНО)Сть регистров PeZ и гистр РгХ - шестиразрядный (, т ), а регистр РгУ - пятиразрядный ( ). Согласно формулам (1-3) система содержит (m-l) 8(8-1) 56 блоков с объемом ячеек Q 2 -2- 2«-2s 2048 каждый. Накопитель ЗУ имеет, таким образом, объем ячеек .2048 114688. Пусть первым тактовым и-мпульсом блока у1правле1ни« БУ в регистры PeZ и РгК приняты следующие кодовые наборы: lPzZ QQQ-Z, Рг/Г1 000 /сЛДешифратор MtuZ выбир.ает (отпирает) коммутирующий ключ Zi и через схему «НЕ возбуждает входы схем «И токовых ключей Zl и , а дещифратор ДшК выбирает коммутирующий ключ К. Такое состояние схемы является запрещенным, поскольку .оказываются дещифрированными матрич1ные ключи одной И той же первой строки. Для исключени/я такой неопределенности предусмотрен сумматор Б по модулю 2, с гомощью которого перед обращением к адресной системе производится ирое.ерка выполни1мости условия...GO,(4) где PeZ и РгК -содержимое соответствующих регистров. Если это условие выполн.яется, то вырабатывается импульс «+1 (формирующие цеп.очки. не показаны), .который добавляется к содержимому регистра. Такой переход обеспечивает выборку уч-астка адресной системы, построенного на ключах: 11 М « У2П-1, 3/j) J У / У у У / 1 /еРЛ1а елл12 11 елл11 Этот участок содержит Диод но-трансформатореый яе|щифратор с двуполярными выходньвми токами « с число1М выходов Q 2-2 rt- - 64-32 2048 (запоминающий блок, которому сопоставлен этот участок для обслуживания, содержит Э 2048 ячеек) и с однополярными выходными токами на ее выходных ячеек, которые выполняют функции) усилителей записи для данного блока. Адрес выбираемой ячейки записьивается IB регистры РгУ и РгХ через выходные дешифраторы в момент действия третьего (считывания) « четвертого (запись) тактовых импульсов, которые обеспечивают ее выборку. .Пример 1. Пусть в регистры РгК и РгХ. (приня.ты кодовые наборы: ЯгУ1 0000 У, 1 РгХ 00000 X, j С 1В031бужде«Ием толовой шииы считывания Сч открыты ключи УН и 22, С коллектором транзисторов inepiBOiro и с эмиттерОМ второго которЫХ соединена первая :полуобм.отка выбираемого традасфорлгатора, иагрузкой котораго является обмотка считыва.ния ячейки 1. Деши.фрированной оказывается первая -ячейка блока 0yVfi. С возбуждением тактовой шйгаы Зап (затись, восстаиовлеяие) вновь отпирается .ключ УН, ,НО € КЛЮЧО М YZZ, С ЭМИГГТером- транзистора которого соедииан коиец второй полуобмотки того же трансформатора. Одеоврамеино с посылкой -полУтока восота.ноевления той же шиной записи через логические схемы «И, ко входам которых подведена соответствующая разрядная шина регистра числа, отпираются те пары матричных ключей разрядных матриц записи, по выходны-м обмоткам которых 1нео|бходимо посылать разрядный ток записи. Еслда, например, необходимо записать «1 по всем разряда-м деШ1ифрир01ван1Еой ячейки (все разрядные шины р, 2р, 5р, ..., сбр регистра числа возбуждены), то отпираются матричные ключи с , с У,2, с Гзь..., , с . разрядных матриц Р/И, РМ2, ..., РМ соответственно, которые обеспечивают посылку токов записи по разрядным обмоткам данного блока. Точно так же выбирается любая другая ячейка запоминающего блока. Пример 2. В регистры РгУ и РгХ приняты кодовые наборы РгУ| з1111 У„/2 РгХ1 Тогда при неизменных кодовых наборах региCTpoiB PaZ и РгК выбирается последняя ячейка (вторичная Обмотка последнего трансформ-атора рассматриваемого участка, средняя TO;4iKa вывода которого соединена с коллектором Yin, а начало и конец - с эммвтерами транзисторов ключей Yzn-i и У2п соответственно), с которой производится считывание или в которую записывается информация. Дешифрация любых других участков адресной системы и обслуживаемых ими запоМИнающИХ блоков происходит в полном соответствии с системой фиг. 2 аналогичным образом. Предмет изобрете.ния Многопозиционная матрица управления, содерл ащая адресную многопозиционную матрицу, выполненную на электронных ключах с диодно-трансфоргматоркыми схемами совпадения на входе, управляемую четырехкоординатной системой дешифрации, и разрядные устройства записи, отличающаяся тем, что, с целью сокращения аб 0рудования и повышения надежности, разрядные устрой,ства записи состоят из га одностолбцовых матриц электронных ключей с ди о дно-т ранефор:маторными схемами совпадения на входе, причем t-я выходная шина первого дешифратора через ключ соединена с общей шиной, объединяющей катоды одной группы диодов, аноды которых соединены с коллекторами транзисторов t-й строки и с первым входом первичных обмоток трансформатора схем совпадения, f-я выходная шина второго дешифратора через электронный ключ подсоединена к общей шине, объединяющей аноды другой группы диодов, катоды которых соединены с эмиттерамИ транзисторов электронных ключей г-й строки и со в.ходами вторых первичных обмоток трансформаторов схем совпадения этой строки, а каждая разрядная шина регистра числа соединена со входами двух согласующих схем «И, выходы которых соединены соответственно со вторыми входами йервой и второй обмоток трансформаторов схем совпадения электронных ключей /-Й одностолбцовой матрицы записи.

S. иг

Г,

2

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

| ЕНБЛИО-ГЕКАС. А. Петросян | 1971 |

|

SU291200A1 |

| МНОГОПОЗИЦИОННОЕ ПРОГРАММНОЕ УСТРОЙСТВО | 1971 |

|

SU320003A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Оперативное запоминающее устройство | 1986 |

|

SU1483493A1 |

| ФОРМИРОВАТЕЛЬ МАТРИЧНЫХ КОМАНД | 2013 |

|

RU2540780C2 |

| Полупроводниковое запоминающее устройство с произвольной выборкой | 1984 |

|

SU1215135A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

Даты

1972-01-01—Публикация