1

Изобретение относится к вычислительной технике.

Известен формирователь импульсов, содерл ащий триггеры, элементы «ИЛИ, элементы задержки, инвертор.

Цель изобретения - раснознавание изменений двоичных сигналов. Достигается она тем, что предлагаемый формирователь выполнен в виде входного 7 5-триггера и двух формирующих узлов, каждый из которых содержит выходной / 5-триггер, прямой выход которого соединен с первой и второй выходными шинами формирователя и через элемент задержки- с ./ -входом промежуточного триггера узла, подключенного своим прямым выходом к первому входу элемента «ИЛИ, выход которого соединен с -входом выходного триггера этого узла, причем S-входы выходных триггеров первого и второго формирующих узлов подключены соответственно к прямому и ииверсному выходам входного триггера формирователя, а также ко второму входу элемента «ИЛИ и к У -входу промел :уточного триггера противоположного узла. Первая и вторая выходные нлины через элемент «ИЛИ соединены с третьей выходной шиной формирователя,- входная /Шина которого соединена с 5-входом и через инвертор - с / -входом входного триггера.

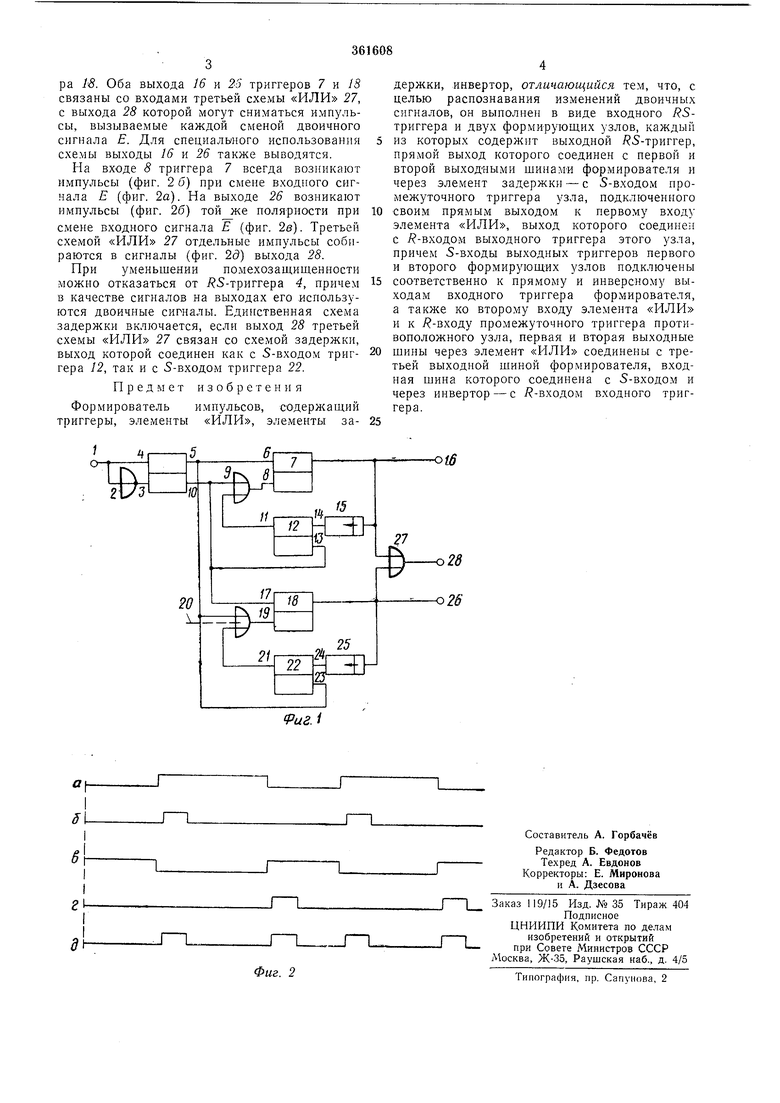

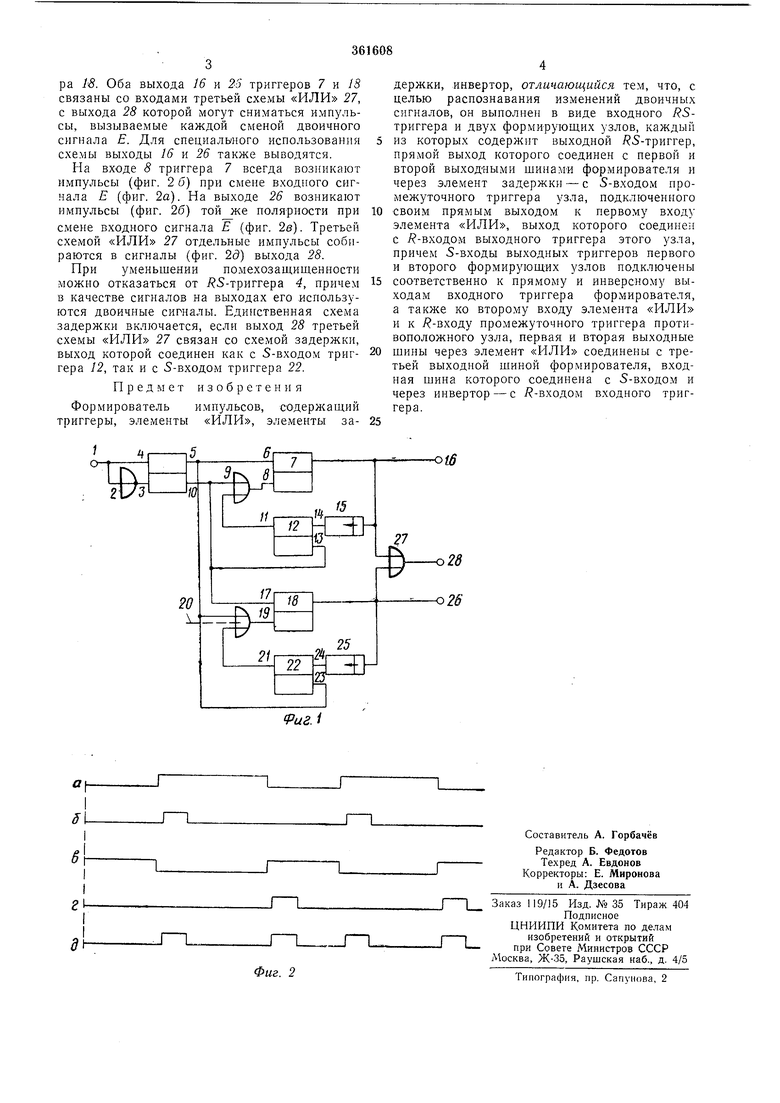

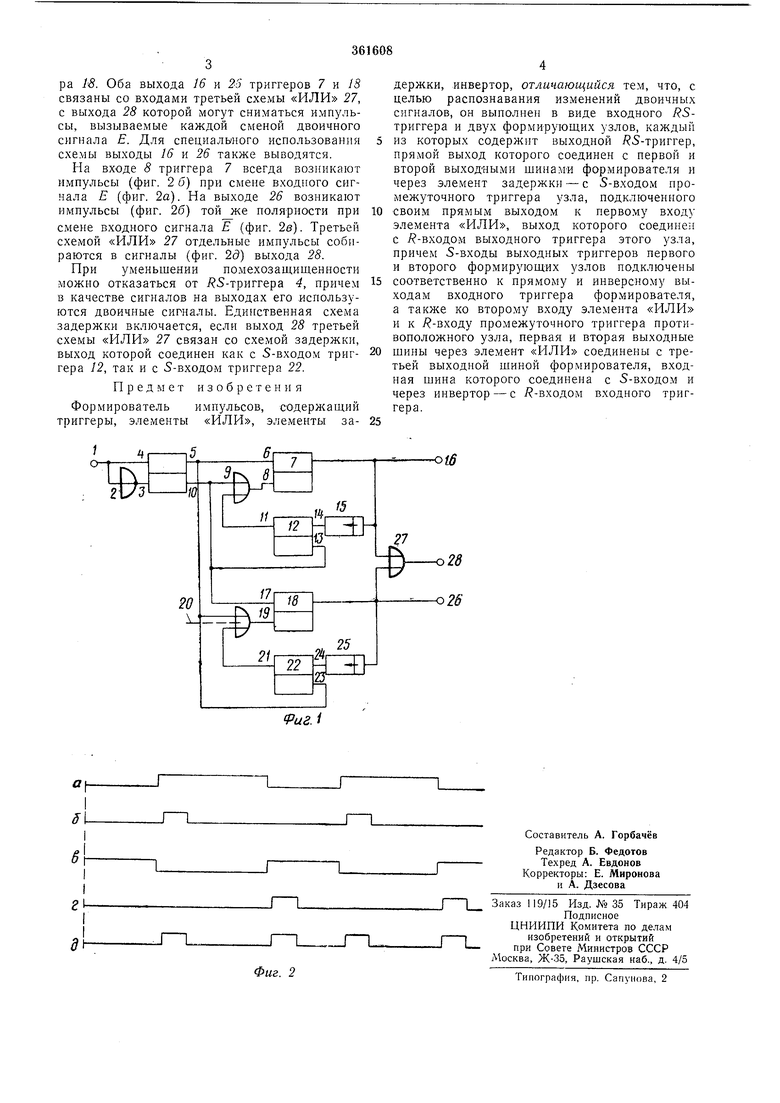

На . 1 нриведена моностабильная релаксационная схема для распознавания изменения сигнала; на фиг. 2 - диаграмма сигналов.

Двоичный сигнал Е, поданный на вход 1, пройдя через инвертор 2, в виде двоичного| сигнала Е подается на / -вход 3 RSтриггера 4. Q-выход 5 / 5-триггера управляет S-входом 6 доминирующе сбрасываемого выходного / 5-триггера 7, перед / -входом 8 которого включена первая схема «ИЛИ 9. Иервый вход ее управляется инверсным выходом 10 / 5-триггера 4, а второй - Q-выходом 11 промежуточного / 5-триггера 12, / -вход 13

которого управляется инверсным выходом 10 / 5-триггера 4. S-вход 14 промежуточного RSтриггера связан с выходом первой схемы задержки 15, вход которой управляется выхо-1 дом 16 5-триггера 7. 5-Бход 17 выходного

/ 5-триггера 18 управляется инверсным выхо-j дом 10 входного / 5-триггера 4. Перед -входом 19 триггера 18 включена вторая схема «ИЛИ 20 с двумя входами. Первый вход связан с Q-выходом 5 тр 1ггера 4, а второй j

управляется Q-выходом 21 промежуточного

/ 5-трнггера 22, / -вход 23 которого соединен

с Q-выходом 5 триггера 4, в время как |

S-вход 24 триггера 22 связан с выходом вто-i

рой схемы задержки 25. Вход этой схемы задержки унравляется выходом 26 / 5-триггеpa IS. Оба выхода 16 и 2-5 триггеров 7 тл IS связаны со входами третьей схемы «ИЛИ 27, с выхода 28 которой могут сниматься импульсы, вызываемые каждой сменой двоичного сигнала Е. Для специального использования схемы выходы 16 и 26 также выводятся. На входе 8 триггера 7 всегда возникают импульсы (фиг. 2 б) при смене входного сигнала Е (фиг. 2а). На выходе 26 возникают импульсы (фиг. 26) той же полярности при смене входного сигнала Е (фиг. 20). Третьей схемой «ИЛИ 27 отдельные импульсы собираются в сигналы (фиг. 2(5) выхода 28. При уменьшении помехозащищенности можно отказаться от У 5-триггера 4, причем в качестве сигналов на выходах его .используются двоичные сигналы. Единственная схема задержки включается, если выход 28 третьей схемы «ИЛИ 27 связан со схемой задержки, выход которой соединен как с S-входом триггера 12, так и с 5-входом триггера 22. Н р е д м е т изобретения Формирователь импульсов, содержащий триггеры, элементы «ИЛИ, элементы задержки, инвертор, отличающийся тем, что, с целью распознавания изменений двоичных сигналов, он выполнен в виде входного RSтриггера и двух формирующих узлов, каждый из которых содержит выходной / 5-триггер, прямой выход которого соединен с первой и второй выходными шинами формирователя и через элемент задержки - с S-входом промежуточного триггера узла, подключенного своим прямым выходом к первому входу элемента «ИЛИ, выход которого соединен с -входом выходного триггера этого узла, причем 5-входы выходных триггеров первого и второго формирующих узлов подключены соответственно к прямому и инверсному выходам входного триггера формирователя, а также ко второму входу элемента «ИЛИ и к / -входу промежуточного триггера противоположного узла, первая и вторая выходные щины через элемент «ИЛИ соединены с третьей выходной щиной формирователя, входная шина которого соединена с 5-входом и через инвертор - с / -входом входного триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ЗАПИСИ и СЧИТЫВАНИЯ АЛФАВИТНО- | 1973 |

|

SU385276A1 |

| ВСВС-ОЮОИАН | 1973 |

|

SU372712A1 |

| УСТРОЙСТВО ФАЗОВОГО УПРАВЛЕНИЯ | 1971 |

|

SU310467A1 |

| ИАТЕИТШ- 1р Ш -уйййЧЕСКАЯ * | 1970 |

|

SU279496A1 |

| ГДР)Опубликовано 10.УИ1.1973. Бюллетень № 33 Дата опубликоваиия. описания 16.L1974МПК G 06k 9/04УДК 621.391.19(088.8) | 1973 |

|

SU393850A1 |

| Устройство для управления инвертором | 1990 |

|

SU1709482A1 |

| СПОСОБ ВЫДЕЛЕНИЯ СИНХРОНИЗИРУЮЩЕГО КАНАЛА ПРИ ПЕРЕДАЧЕ ФОТОТЕЛЕГРАФНОЙ ИНФОРМАЦИИ С ПОМОЩЬЮ КОДОВО-ИМПУЛЬСНОЙ МОДУЛЯЦИИ | 1966 |

|

SU189016A1 |

| ПЕРЕСЧЕТНАЯ ЯЧЕЙКАВСЕСОЮЗНАЯJUlTHTHO-KKil^SClWЬИ6.ПИОТЕНА | 1971 |

|

SU305687A1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

| Устройство для выделения импульса | 1985 |

|

SU1272489A1 |

Авторы

Даты

1973-01-01—Публикация