Изобретение относится к дискретной импульсной технике, а именно к формирователям интервалов времени высокой точности на структурах, использующих счет по произвольному модулю с постоянным шагом в соответствии с числовыми значениями управляющих кодов, и может быть использовано в аппаратуре электронной автоматики, связи, управления подвижными объектами, локации и контрольно-измерительной техники, например, в имитаторах задерживаемых сигналов.

Аналогами предлагаемого формирователя импульсных последовательностей могут служить преобразователи кода во временной интервал [1]

Следует отметить невысокое быстродействие названных преобразователей, а следовательно, ограниченную разрешающую способность по предельной частоте тактовых синхроимпульсов на входе устройства, из-за последовательного накопления естественной задержки сигнала окончания счета, формируемого счетчиком СТ2, и из-за возможности возникновения импульсных помех малой длительности "иголок" на выходе схемы сравнения кодов (ССК), возникающих во время переходных процессов при сквозных переносах единицы счета в многоразрядной структуре СТ2, использующей позиционный двоичный код (ПДК).

Наиболее близок по совокупности существенных признаков к предлагаемому формирователю двоичный счетчик с параллельным вводом информации [2] функционирующий в ПДК при суммировании М тактовых импульсов, поступающих на вход Ф, от момента предустановки двоичного числа П до достижения состояния Zмакс, числовое значение которого определяется разрядностью и основанием 2 Zмакс 2n-1.

Названный синхронный счетчик можно рассматривать как преобразователь параллельного двоичного кода, числовое значение которого равно М, в интервал времени от момента предустановки кода числа Р до появления фронта сигнала переноса на выходе СЕ при подсчете М импульсов Ф. При этом входным воздействием служит кодовое слово Р3, Р2, Р1, Р0, числовое значение которого Р Zмакс М, и поразрядно Р3 , P2

, P2 , P1

, P1 , P0

, P0 .

.

У выбранного прототипа, использующего счет в ПДК, также ограничена разрешающая способность по минимальному дискрету тактовых синхроимпульсов из-за появления помех "иголок", формируемых дешифратором состояния Zмакс, и на подавление которых при счете затрачивается половина дискрета Ф, из-за введения запрета в элемент переноса СЕ по дополнительному входу на время переходных процессов в счетной структуре. При этом фронт импульса, формируемого элементом СЕ, отстоит на половину дискрета Ф от фронта соответствующего синхроимпульса, а длительность уменьшается на половину дискрета Ф.

При каскадировании двух подобных устройств для последовательного формирования задержки фронта и длительности импульса, после подсчета числа дискретов, заданного кодом задержки, необходимо время внутри очередного дискрета для запуска формирователя длительности импульса, что также ухудшит разрешающую способность по минимальному дискрету тактовых синхроимпульсов на входе.

При этом возможно "дрожание" фронта формируемого импульса из-за нестабильности естественной задержки фронтов сигналов, формируемых элементами, задействованными в цепи запуска второго формирователя.

Задача предлагаемого изобретения заключается в повышении аппаратурной точности интервалов задержки фронта и длительности импульсов, обеспечиваемой ждущим формирователем импульсов за счет улучшения разрешающей способности n-разрядного счетчика импульсов, из его состава, по минимальному дискрету тактовых синхроимпульсов.

Решение поставленной задачи обеспечивается построением формирователя, запускаемого фронтом старт-импульса, на основе n-разрядного синхронного счетчика импульсов в коде Грея, с инфракрасной емкостью N до (2n-1) единиц счета и непрерывным счетом при последовательном формировании интервалов задержки фронта и длительности импульса, задаваемых числовыми значениями управляющих кодов, когда в момент предустановки в счетчик импульсов вводится параллельный код задержки фронта импульса по  и

и  -входам IK-триггеров нулевого и n значащих разрядов счетчика импульсов, а для сформирования собственно импульса заданной длительности служит дополнительный (n+1)-й синхронный IK-триггер, открывающий схему сравнения кодов, которая останавливает счет в момент опознания результата подсчитанной длительности.

-входам IK-триггеров нулевого и n значащих разрядов счетчика импульсов, а для сформирования собственно импульса заданной длительности служит дополнительный (n+1)-й синхронный IK-триггер, открывающий схему сравнения кодов, которая останавливает счет в момент опознания результата подсчитанной длительности.

Повышение разрешающей способности по дискрету единицы счета на входе формирователя достигается за счет специфики кода Грея и предлагаемого построения функциональной схемы.

При считывании текущей информации со счетчика Грея принципиально исключены импульсные помехи-"иголки", а перепад потенциала, прекращающий счет, формируется схемой опознания непосредственно из перепада 0 ->> 1 с выхода тока IK-триггера, который переключается последним импульсом счета в цикле формирования.

Упрощение поразрядной предустановки кода задержки фронта формируемого импульсного достигается организацией перекрестного ввода логических "нуля" и "единицы" по  и

и  -входам IK-триггера старшего n-го разряда счетчика импульсов, так как вводимое дополнение кода Грея до числового значения (2n-1) отличается от кода, числовое значение которого соответствует числу дискретов задержки фронта, досчитываемых после предустановки, только инверсным значением одного старшего разряда.

-входам IK-триггера старшего n-го разряда счетчика импульсов, так как вводимое дополнение кода Грея до числового значения (2n-1) отличается от кода, числовое значение которого соответствует числу дискретов задержки фронта, досчитываемых после предустановки, только инверсным значением одного старшего разряда.

Синхронность всех дискретов в интервале счета, включающего задержку фронта и длительность формируемого импульса, обеспечивается непрерывностью счета с использованием свойства "отражения" кода в n значащих разрядах счетчика импульсов после подсчета (2n-1)-го тактового синхроимпульса и синхронного переноса 2n-го (нулевого) синхроимпульса, устанавливающего (n+1)-й IK-триггер в состояние единица по С-входу.

Полная информационная емкость предлагаемого устройства, в зависимости от числовых значений управляющих кодов, до (2n-2) единиц счета, по формируемой задержке фронта, плюс до (2n-1) единиц счета, по длительности импульса, а конкретные величины задержек ti и длительностей τj находятся в пределах значений

1 . Tc + Δ t3 < ti < (2n-2)Tc + Δt3

1 . Tc + Δ τв< τj < (2-1)Tc + Δtв где Тс период повторения тактовых синхроимпульсов (дискрет счета);

Δt3 погрешность формирования интервала задержки фронта импульса из-за несинхронности запуска устройства (0 < <Δt3 < Tc);

Δtв время восстановления исходного состояния устройства, определяемое суммой естественных задержек перепадов потенциала последовательно срабатывающих элементов.

Для функционирования устройства без сбоя в цикле формирования, период следования СТАРТ-импульсов (с запасом в ЗТс) должен быть:

Тмин ≥ tмакс + τмакс + 3Тс.

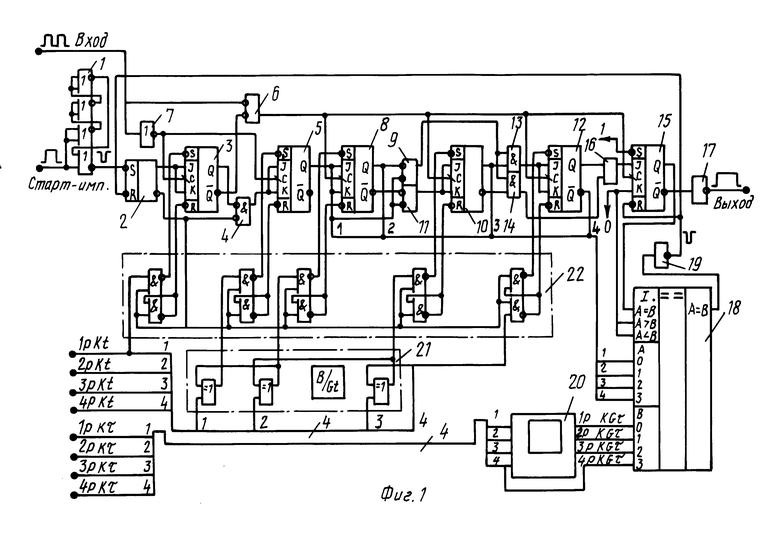

На фиг.1 приведена функциональная схема ждущего формирователя импульсов, как пример реализации предлагаемого устройства, на основе четырехразрядного счетчика импульсов в коде Грея (n 4) с информационной емкостью в 15 единиц счета (N 2n-1), формирующего задержку фронта импульса, равной 10-ти интервалам счета t 10Тс, и его длительность, равной 6-и интервалам счета τ 6Тс, на фиг. 2 временные соотношения перепадов потенциала входных, промежуточных и формируемых импульсных последовательностей.

Ждущий формирователь импульсов на основе n-разрядного счетчика импульсов 3,4,15,16 и 17 с информационной емкостью N (2n-1) единиц счета, включающий группу из (n+2) синхронных IK-триггеров 3,5,8,10,12 и 15 с установкой нуля и единицы, первый инвертор 7, выход которого подключен к С-входам IK-триггеров нулевого 3 и первого 5 разрядов счетчика импульсов, элемент 2И 6 инверсной логики, первый вход которого подключен к  -выходу IK-триггера 3 нулевого разряда, а выход к С-входам IK-триггеров, начиная со второго разряда 8 по (n+1)-й дополнительный IK-триггер 15, группу из n элементов 2И 4, 11, 13, 16, первый 4 и второй 11 из которых являются элементами 2И инверсной логики, последовательную цепь из (n-2) элементов 2И 9 и 14 сквозного переноса, первый из которых 9 элемент 2И инверсной логики, а также второй выходной инвертор 17, вход которого подключен к

-выходу IK-триггера 3 нулевого разряда, а выход к С-входам IK-триггеров, начиная со второго разряда 8 по (n+1)-й дополнительный IK-триггер 15, группу из n элементов 2И 4, 11, 13, 16, первый 4 и второй 11 из которых являются элементами 2И инверсной логики, последовательную цепь из (n-2) элементов 2И 9 и 14 сквозного переноса, первый из которых 9 элемент 2И инверсной логики, а также второй выходной инвертор 17, вход которого подключен к  -выходу (n+1)-го IK-триггера 15, кроме счетчика импульсов, содержит еще схему параллельного ввода кода задержки 22, включающую (n+1)-у логическую пару элементов 2И-НЕ, первый n-разрядный преобразователь 21 параллельного двоичного кода (ПДК) задержки в код Грея (В/Gt), включающий (n-1) элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй n-разрядный преобразователь ПДК длительности импульса в код Грея (B/Gτ ), также включающий (n-1) элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первую n-разрядную контактную группу параллельного ПДК задержки (Kt), поразрядно подключенную ко входам первого преобразователя 21 В/Gt, вторую n-разрядную контактную группу параллельного ПДК длительности импульса (К τ), поразрядно подключенную ко входам второго преобразователя 20 B/Gτ n-разрядную схему сравнения двоичных параллельных кодов 18, выход которой А В подключен ко входу третьего инвертора 19, первую входную шину Вход, подключенную ко входу первого инвертора 7 и ко второму входу элемента 2И 6 инверсной логики, соединенного с С-входами IK-триггеров 8, 10, 12 и 15, выходную шину Выход, подключенную к выходу второго инвертора 17, вторую входную шину старт-импульса, подключенную ко входам детектора 1 его фронта, построенного на элементах 2И-НЕ, выход которого подключен к

-выходу (n+1)-го IK-триггера 15, кроме счетчика импульсов, содержит еще схему параллельного ввода кода задержки 22, включающую (n+1)-у логическую пару элементов 2И-НЕ, первый n-разрядный преобразователь 21 параллельного двоичного кода (ПДК) задержки в код Грея (В/Gt), включающий (n-1) элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй n-разрядный преобразователь ПДК длительности импульса в код Грея (B/Gτ ), также включающий (n-1) элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первую n-разрядную контактную группу параллельного ПДК задержки (Kt), поразрядно подключенную ко входам первого преобразователя 21 В/Gt, вторую n-разрядную контактную группу параллельного ПДК длительности импульса (К τ), поразрядно подключенную ко входам второго преобразователя 20 B/Gτ n-разрядную схему сравнения двоичных параллельных кодов 18, выход которой А В подключен ко входу третьего инвертора 19, первую входную шину Вход, подключенную ко входу первого инвертора 7 и ко второму входу элемента 2И 6 инверсной логики, соединенного с С-входами IK-триггеров 8, 10, 12 и 15, выходную шину Выход, подключенную к выходу второго инвертора 17, вторую входную шину старт-импульса, подключенную ко входам детектора 1 его фронта, построенного на элементах 2И-НЕ, выход которого подключен к  -входу IK-триггера 2 интервала счета, Q-выход которого подключен к I- и К-входам IK-триггера 3 нулевого разряда, и

-входу IK-триггера 2 интервала счета, Q-выход которого подключен к I- и К-входам IK-триггера 3 нулевого разряда, и  -выход к первому входу первого элемента 2И 4 инверсной логики межразрядной связи, второй вход которого подключен к Q-выходу IK-триггера 3 нулевого разряда, а выход к I и K-входам IK-триггера 5 первого разряда,

-выход к первому входу первого элемента 2И 4 инверсной логики межразрядной связи, второй вход которого подключен к Q-выходу IK-триггера 3 нулевого разряда, а выход к I и K-входам IK-триггера 5 первого разряда,  -выход RS-триггера 2 подключен также к 2 . (n+1) управляющим входам логических пар элементов 2И-НЕ схемы 22 параллельного ввода кода задержки, а информационные входы логических пар, начиная с соединенной своими выходами с

-выход RS-триггера 2 подключен также к 2 . (n+1) управляющим входам логических пар элементов 2И-НЕ схемы 22 параллельного ввода кода задержки, а информационные входы логических пар, начиная с соединенной своими выходами с  и

и  входами IK-триггера 5 первого разряда, поразрядно подключены к выходам первого преобразователя 21 В/Gt, Q-выход IK-триггера 5 первого разряда подключен к I и К-входам IK-триггера 8 второго разряда и к первому входу второго элемента 2И 11 инверсной логики межразрядной связи, выход которого подключен к I- и К-входам IK-триггера 10 третьего разряда, первый вход первого элемента 2И 9 инверсной логики цепи сквозного переноса также подключен к Q-выходу IK-триггера 5 первого разряда и соединен с первым входом второго элемента 2И 11 межразрядной связи, второй вход второго элемента 2И 1 инверсной логики межразрядной связи подключен к

входами IK-триггера 5 первого разряда, поразрядно подключены к выходам первого преобразователя 21 В/Gt, Q-выход IK-триггера 5 первого разряда подключен к I и К-входам IK-триггера 8 второго разряда и к первому входу второго элемента 2И 11 инверсной логики межразрядной связи, выход которого подключен к I- и К-входам IK-триггера 10 третьего разряда, первый вход первого элемента 2И 9 инверсной логики цепи сквозного переноса также подключен к Q-выходу IK-триггера 5 первого разряда и соединен с первым входом второго элемента 2И 11 межразрядной связи, второй вход второго элемента 2И 1 инверсной логики межразрядной связи подключен к  -выходу IK-триггера 8 второго разряда, а второй вход первого элемента 2И 9 инверсной логики цепи сквозного переноса подключен к Q-выходу IK-триггера 8 второго разряда, выход i-го элемента 2И, начиная с первого 9, цепи сквозного переноса подключен к первому входу (i+1)го элемента 2И 14 цепи сквозного переноса и к первому входу (i+2)-го элемента 2И 13 межразрядной связи, второй которого подключен к

-выходу IK-триггера 8 второго разряда, а второй вход первого элемента 2И 9 инверсной логики цепи сквозного переноса подключен к Q-выходу IK-триггера 8 второго разряда, выход i-го элемента 2И, начиная с первого 9, цепи сквозного переноса подключен к первому входу (i+1)го элемента 2И 14 цепи сквозного переноса и к первому входу (i+2)-го элемента 2И 13 межразрядной связи, второй которого подключен к  -выходу IK-триггера 10 (i+2)-го разряда, а выход к I- и К-входам IK-триггера 12 (i+3)-го разряда, и второй вход (i+1)-го элемента 2И 14 цепи сквозного переноса подключен к Q-выходу IK-триггера 10 (i+2)-го разряда, согласно изобретению n-разрядный счетчик импульсов 3,4,15,16 и 17 является синхронным счетчиком в коде с информационной емкостью N= (2n-1) единиц счета, у которого S-входы IK-триггеров нулевого 3, первого 5,i-го 8,(n-1)-го 10 разрядов и

-выходу IK-триггера 10 (i+2)-го разряда, а выход к I- и К-входам IK-триггера 12 (i+3)-го разряда, и второй вход (i+1)-го элемента 2И 14 цепи сквозного переноса подключен к Q-выходу IK-триггера 10 (i+2)-го разряда, согласно изобретению n-разрядный счетчик импульсов 3,4,15,16 и 17 является синхронным счетчиком в коде с информационной емкостью N= (2n-1) единиц счета, у которого S-входы IK-триггеров нулевого 3, первого 5,i-го 8,(n-1)-го 10 разрядов и  -вход IK-триггера 12 n-го разряда поразрядно подключены к прямым информационным выходам логических пар элементов 2И-НЕ схемы параллельного ввода 22 кода задержки, а

-вход IK-триггера 12 n-го разряда поразрядно подключены к прямым информационным выходам логических пар элементов 2И-НЕ схемы параллельного ввода 22 кода задержки, а  -входы IK-триггеров нулевого 3, первого 5, i-го 8,(n-1)-го 10 разрядов и

-входы IK-триггеров нулевого 3, первого 5, i-го 8,(n-1)-го 10 разрядов и  -вход IK-триггера 12 n-го разряда поразрядно подключены к инверсным информационным выходам названных пар элементов 2И-НЕ, и в состав счетчика импульсов введен (n+1)-й синхронный IK-триггер 15, I-вход которого подключен к выходу n-го элемента 2И 16 межразрядной связи, первый вход которого подключен к Q-выходу IK-триггера 12 n-го разряда, а второй вход к выходу (n-2)-го элемента 2И 14 цепи сквозного переноса,

-вход IK-триггера 12 n-го разряда поразрядно подключены к инверсным информационным выходам названных пар элементов 2И-НЕ, и в состав счетчика импульсов введен (n+1)-й синхронный IK-триггер 15, I-вход которого подключен к выходу n-го элемента 2И 16 межразрядной связи, первый вход которого подключен к Q-выходу IK-триггера 12 n-го разряда, а второй вход к выходу (n-2)-го элемента 2И 14 цепи сквозного переноса,  -вход (n+1)-го IK-триггера 15 подключен к шине логической "единицы", а К-вход к шине логического "нуля", Q-выход (n+1)-го IK-триггера 15 подключен к стробируемому входу А=В схемы сравнения 18 параллельных n-разряднеых кодов, а выход

-вход (n+1)-го IK-триггера 15 подключен к шине логической "единицы", а К-вход к шине логического "нуля", Q-выход (n+1)-го IK-триггера 15 подключен к стробируемому входу А=В схемы сравнения 18 параллельных n-разряднеых кодов, а выход  третьего инвертора 19 подключен к R-входу (n+1)-го IK-триггера 15 и к

третьего инвертора 19 подключен к R-входу (n+1)-го IK-триггера 15 и к  -входу RS-триггера 2, и n-входов группы А схемы сравнения 18 поразрядно подключены к Q-выходам IK-триггеров первого 5, i-го 8,(n-1)-го 10 разрядов счетчика импульсов и к

-входу RS-триггера 2, и n-входов группы А схемы сравнения 18 поразрядно подключены к Q-выходам IK-триггеров первого 5, i-го 8,(n-1)-го 10 разрядов счетчика импульсов и к  -выходу IK-триггера 12 n-го разряда, а n входов группы В поразрядно подключены к n выходам второго преобразователя 20 В/Gτ и информационный вход логической пары элементов 2И-НЕ параллельного ввода кода задержки, выходы которой соединены с

-выходу IK-триггера 12 n-го разряда, а n входов группы В поразрядно подключены к n выходам второго преобразователя 20 В/Gτ и информационный вход логической пары элементов 2И-НЕ параллельного ввода кода задержки, выходы которой соединены с  и

и  -входами IK-триггера 3 нулевого разряда, подключен к контакту IpK1 младшего разряда контактной группы ПДК задержки, и С-входы IK-триггеров 8, 10, 12 значащих разрядов счетчика импульсов, начиная с IK-триггера 8 второго разряда по n-й включительно, а также С-вход (n+1)-го IK-триггера 15 подключены к выходу элемента 2И 6 инверсной логики, первый вход которого подключен к

-входами IK-триггера 3 нулевого разряда, подключен к контакту IpK1 младшего разряда контактной группы ПДК задержки, и С-входы IK-триггеров 8, 10, 12 значащих разрядов счетчика импульсов, начиная с IK-триггера 8 второго разряда по n-й включительно, а также С-вход (n+1)-го IK-триггера 15 подключены к выходу элемента 2И 6 инверсной логики, первый вход которого подключен к  -выходу IK-триггера 3 нулевого разряда, а второй к первой входной шине.

-выходу IK-триггера 3 нулевого разряда, а второй к первой входной шине.

Работа ждущего формирователя импульсов описана на примере устройства, реализованного на основе четырехразрядного (n=4) счетчика импульсов, с внешним запуском от фронта старт-импульса (фиг.2.1).

Последовательность тактовых синхроимпульсов "Вход" (фиг.2.3) с периодом Тс поступает на вход первого инвертора 7 и на второй (сигнальный) вход элемента 2И 6 инверсной логики. Запускающий импульс отрицательной полярности (фиг. 2.1) с выхода детектора фронта 1 старт-импульса поступает на  -вход RS-триггера 2 и переключает его в состояние разрешения счета (фиг.2.2).

-вход RS-триггера 2 и переключает его в состояние разрешения счета (фиг.2.2).

Положительный период потенциала с Q-выхода, а отрицательный с  -выхода RS-триггера 2, переводят счетчик импульсов в рабочее состояние, поступая на I- и К-входы IK-триггера 3 нулевого разряда и на первый (управляющий) вход элемента 2И 4 инверсной логики.

-выхода RS-триггера 2, переводят счетчик импульсов в рабочее состояние, поступая на I- и К-входы IK-триггера 3 нулевого разряда и на первый (управляющий) вход элемента 2И 4 инверсной логики.

Импульсы отрицательной фазы с Q-выхода IK-триггера 3 поступает на второй (сигнальный) вход элемента 2И 4, формируя последовательность "Выход 4" (фиг. 2.6), управляющую переключениями IK-триггера 5 первого разряда по I- и К-входам. Переключения IK-триггера 3 вызываются перепадами 1 ->> 0 группы импульсов последовательности "Выход 7" (фиг.2.4), поступающими на его С-вход, а переключения IK-триггера 5 только нечетными перепадами 1 ->> 0 импульсов этой группы.

Переключения IK-триггеров 8, 10, 12 и включение дополнительного пятого IK-триггера 15 вызываются перепадами 1 ->> 0 импульсов последовательности "Выход 6" (фиг.2.5), формируемой элементом 2И 6 при совпадении импульсов инверсной фазы последовательности "вход", поступающих на второй (сигнальный) вход элемента 2И 6, с импульсами инверсной фазы поступающими с  -выхода IK-триггера 3 нулевого разряда на первый (управляющий) вход. При этом названные перепады 1 ->> 0 синхронны счетными перепадами 1 ->> 0 группы импульсов, вызывающей переключения IK-триггера 3 нулевого разряда счетчика импульсов.

-выхода IK-триггера 3 нулевого разряда на первый (управляющий) вход. При этом названные перепады 1 ->> 0 синхронны счетными перепадами 1 ->> 0 группы импульсов, вызывающей переключения IK-триггера 3 нулевого разряда счетчика импульсов.

Запас по возможному наращиванию разрядности n счетчика импульсов при минимальном дискрете Тс единицы счета обеспечивается организацией синхронного запуска IK-триггеров всех разрядов, начиная с IK-триггера 8 второго разряда, перепадами 1 ->> 0 импульсов последовательности "Выход 6" с удвоенным периодом повторения 2Тс, и синхронного запуска IK-триггеров 3 и 5, за счет введения инвертора 7, формирующего их синхроимпульсы (фиг.2.4), для компенсации естественного запаздывания перепадов 1 ->> 0, вносимого элементом 2И 6.

При опознании исходным кодом Gτ текущего кода формируемой длительности импульса в предшествовавшем цикле формирования, на А=В выходе схемы сравнения 18 возникает перепад потенциала 0 ->> 1 (фиг.2.12), который, инвертируясь элементом 19 (фиг.2.13), формирует срез выходного импульса (фиг.2.14), переключая IK-триггер 15 в нулевое состояние, останавливает счет, возвращая RS-триггер 2 (фиг.2.2) в исходное состояние по  -входу, а перепад потенциала 0 ->> 1 с

-входу, а перепад потенциала 0 ->> 1 с  -выхода RS-триггера, поступающий на 10 управляющих входов пяти логических пар элементов 2И-НЕ схемы 22, вводит новые данные о задержке фронта формируемого импульса.

-выхода RS-триггера, поступающий на 10 управляющих входов пяти логических пар элементов 2И-НЕ схемы 22, вводит новые данные о задержке фронта формируемого импульса.

При этом в IK-триггер 3 нулевого разряда записывается единица младшего разряда ПДК задержки, а в IK-триггеры 12, 10, 8, 5 значащих разрядов счетчика импульсов поразрядно записывается дополнение 0III до I000 кода IIII задержки фронта импульса в соответствии с числовыми значениями 5,15(24-1) и 10.

С приходом очередного старт-импульса и переходом RS-триггера 2 в состояние разрешения счета, происходит счет на сложение от промежуточного значения 0III до I000 (фиг.2.7-10), в результате чего на I-входе IK-триггера 15, находившегося в состоянии нуля, появляется положительный импульс "Выход 16" (фиг. 2.11), как результат последовательных совпадений в цепи элементов 2И 9, 14 и 16 инверсной фазы Q-выхода IK-триггера 5 с инверсной фазой Q-выхода IK-триггера 8, с основной фазой  -выхода IK-триггера 10 и с основной фазой Q-выхода IK-триггера 12 во время 15-го и нулевого тактов счета.

-выхода IK-триггера 10 и с основной фазой Q-выхода IK-триггера 12 во время 15-го и нулевого тактов счета.

Перепад 1 ->> 0 импульса последовательности "Выход 6" (фиг.2.5), совпавший с импульсом "Выход 16" в начале нулевого такта счета, синхронно переключает IK-триггер 15 в состояние единица и начинает формирование длительности выходного импульса, без останова счета IK-триггерами 3, 5, 8, 10 и 12.

Перепад потенциала 0 ->> 1 (фиг.2.14) с Q-выхода IK-триггера 15 открывает схему сравнения кодов 18 по входу А=В опознания четырехразрядного параллельного кода Грея, считываемого группой А внешним кодом Gτ заданной длительности импульса, поразрядно подключенным к четырем входам группы В схемы сравнения.

Подключение к шине логического "нуля" входов A>B и A<B логического элемента типа СП1, изображенного в качестве примера 18 на фиг.1, не имеет принципиального значения.

При совпадении текущего состояния IK-триггеров значащих разрядов счетчика импульсов  Q10Q8Q5 в коде Грея, считываемого входами группы А схема сравнения 18, с кодом Gτ 0I0I заданной длительности импульса группы В, на выходе результата А=В схемы сравнения появляется перепад потенциала 0 ->> 1, который, инвертируясь элементом 19, переводит устройство в исходное состояние (фиг.2.12, 13), прекращая счет, завершая формирование выходного импульса (фиг.2.14) и импульса предустановки (фиг.2.13), при занесении очередных данных о задержке фронта импульса схемой параллельного ввода кода 22, вызванных перепадом 0 ->> 1 с

Q10Q8Q5 в коде Грея, считываемого входами группы А схема сравнения 18, с кодом Gτ 0I0I заданной длительности импульса группы В, на выходе результата А=В схемы сравнения появляется перепад потенциала 0 ->> 1, который, инвертируясь элементом 19, переводит устройство в исходное состояние (фиг.2.12, 13), прекращая счет, завершая формирование выходного импульса (фиг.2.14) и импульса предустановки (фиг.2.13), при занесении очередных данных о задержке фронта импульса схемой параллельного ввода кода 22, вызванных перепадом 0 ->> 1 с  -выхода RS-триггера при выключении счета.

-выхода RS-триггера при выключении счета.

Исходная информация в ПДК о задержке фронта и формируемой длительности импульса преобразуется в код Грея двумя четырехразрядными преобразователями B/Gt 21 и B/Gτ 20, каждый из которых содержит по три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, включенных по известной схеме [2]

Схема параллельного ввода 22 кода задержки по  и

и  -входам IK-триггеров счетчика импульсов включает 5 известных логических пар элементов 2И-НЕ, аналогичных используемым в "Двоичном счетчике с параллельным вводом информации" [2] причем пятая логическая пара обеспечивает инверсный ввод информации о задержки фронта по

-входам IK-триггеров счетчика импульсов включает 5 известных логических пар элементов 2И-НЕ, аналогичных используемым в "Двоичном счетчике с параллельным вводом информации" [2] причем пятая логическая пара обеспечивает инверсный ввод информации о задержки фронта по  - и

- и  -входам IK-триггера 12 четвертого разряда.

-входам IK-триггера 12 четвертого разряда.

Синхронизируемые последовательностью старт-импульсов, циклы формирования возобновляются и повторяются при неизменных исходных данных.

Известно, что точность преобразования кодовых комбинаций в интервалы времени счетными структурами определяется минимальным дискретом тактовых синхроимпульсов, т. е. быстродействием используемых счетных элементов и архитектурой устройства.

Кроме методической погрешности формирования суммы обоих интервалов времени задержки фронта и длительности импульса, определяемый произведением погрешности дискрета счета Δ Тс на сумму числовых значений, соответствующих каждому из кодов задержки фронта и длительности импульса, присутствует погрешность формирования задержки фронта t Δ t, определяемая задержкой перепада 1 ->> 0 импульса из последовательности "Выход 7" (фиг.2.4) или "Выход 6" (фиг.2.5), совпавшего с началом счета, относительно фронта старт-импульса, а также погрешность формирования длительности импульса τ-Δτв вызванная задержкой выключения (n+1)-го IK-триггера 15 по  -входу.

-входу.

Δτв t1118 + t1019 + t1015, где t1118 естественная задержка срабатывания схемы сравнения кодов 18 по перепаду 0 ->> 1, пришедшему на один из входов (AI) группы А;

t1019 время включения третьего инвертора 19;

t1015 время выключения IK-триггера по  -входу.

-входу.

Для выполнения жестких требований, предъявляемых к точности преобразования при минимальном дискрете Тс единицы счета, элементы 1,2,3,4,5,6,7,8,9,10,11,12,13,14, 15,16,18, и 19, образующие структуру счетчика импульсов с цепями запуска, синхронизации, межразрядных связей, опознания кода длительности и возврата к исходным данным, должны иметь повышенное быстродействие, а значит и высокое потребление тока от вторичного источника электропитания (ВИЭП).

Так как импульсные ключи потребляют "ПИК" мощности от ВИЭП-Я при формировании перепадов потенциала 1 ->> 0 и 0 ->> 1, то суммарное потребление тока по цепи питания растет с увеличением частоты дискретизации Fc 1/Tс и разрядности n-счетной структуры.

Внедрение формирователей, реализуемых по предлагаемой функциональной схеме, позволяет получить разрешение по максимальной частоте единицы счета n-разрядной синхронной структурой порядка половины паспортного значения, гарантируемого базовым элементом синхронным IK-триггером. Использование, например, ИМС ТТЛШ менее мощных серий, при выполнении требований к точности преобразования, поможет снизить потребление тока от ВИЭП, обеспечить тепловой режим комплектующих элементов, а также частично упростить трассировку печатного основания вследствие повторного задействования IK-триггеров n значащих разрядов счетчика импульсов на время формирования импульса заданной длительности.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| ДИСКРЕТНО-АНАЛОГОВЫЙ СИНУС-ГЕНЕРАТОР | 1995 |

|

RU2108657C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2037958C1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2110146C1 |

| СЧЕТНОЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ | 1993 |

|

RU2074513C1 |

| Комбинированное устройство временной задержки и формирования импульсов | 1987 |

|

SU1443151A1 |

| Цифровой измеритель длительности одиночных импульсов | 1983 |

|

SU1171444A1 |

Использование: в импульсной технике, в частности в устройствах автоматики и вычислительной техники. Сущность изобретения: устройство содержит управляющий RS-триггер, шесть JK-триггеров 3,5,8,10,12,15, два преобразователя 20,21, схему параллельного ввода данных 22, детектор фронта старт-импульсов 1, пять элементов совпадения 4,6,11,13,16, две кодовые шины Kτ и Kt, входную шину, шину старт-импульсов, три инвертора 7,17,19, выходную шину, элемент сравнения кодов 18. 2 ил.

ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ, содержащий входную шину, управляющую шину "Старт-имп.", управляющий RS-триггер, счетчик импульсов, элемент сравнения кодов, первую кодовую шину Kτ, вторую кодовую шину Kt и выходную шину, отличающийся тем, что в него введены выходной инвертор, выход которого соединен с выходной шиной, второй инвертор, вход которого соединен с выходом "Равно" (A B) элемента сравнения кодов, первый преобразователь ПКД в код Грея B/Gτ, входы которого поразрядно соединены с первой кодовой шиной Kτ, а выходы с входами группы входов B элемента сравнения кодов, второй преобразователь ПДК в код Грея B/Gt, входы которого поразрядно соединены с второй кодовой шиной Kt, а выходы с информационными входами схемы параллельного ввода данных в элементы значащих разрядов счетчика импульсов, включающей n+1 логических пар элементов 2И-НЕ, детектор фронта старт-импульсов, группа входов которого соединена с управляющей шиной, а выход с  -входом запуска управляющего RS-триггера, причем счетчик импульсов является n-разрядным счетчиком в коде Грея, включающим группу из n+2 синхронных JK-триггеров с установкой нуля и единицы, третий инвертор, выход которого соединен с C-входами JK-триггеров нулевого и первого разрядов счетчика импульсов, а вход с шиной и первым входом элемента 2И-НЕ инверсной логики, второй вход которого соединен с

-входом запуска управляющего RS-триггера, причем счетчик импульсов является n-разрядным счетчиком в коде Грея, включающим группу из n+2 синхронных JK-триггеров с установкой нуля и единицы, третий инвертор, выход которого соединен с C-входами JK-триггеров нулевого и первого разрядов счетчика импульсов, а вход с шиной и первым входом элемента 2И-НЕ инверсной логики, второй вход которого соединен с  -выходом JK-триггера нулевого разряда, а выход с C-входами JK-триггеров, начиная с JK-триггера второго разряда по n-й включительно, и с C-входом дополнительного (n+1)-го JK-триггера,

-выходом JK-триггера нулевого разряда, а выход с C-входами JK-триггеров, начиная с JK-триггера второго разряда по n-й включительно, и с C-входом дополнительного (n+1)-го JK-триггера,  -вход которого соединен с шиной логической единицы, а K-вход с шиной логического нуля, и

-вход которого соединен с шиной логической единицы, а K-вход с шиной логического нуля, и  -входы JK-триггеров первого, i-го, (n-1)-го разрядов и

-входы JK-триггеров первого, i-го, (n-1)-го разрядов и  -входы JK-триггеров нулевого и n-го разрядов соединены с прямыми информационными выходами всех логических пар элементов 2И-НЕ схемы параллельного ввода данных, а

-входы JK-триггеров нулевого и n-го разрядов соединены с прямыми информационными выходами всех логических пар элементов 2И-НЕ схемы параллельного ввода данных, а  -входы JK-триггеров первого, i-го, (n-1)-го разрядов и

-входы JK-триггеров первого, i-го, (n-1)-го разрядов и  -входы JK-триггеров нулевого и n-го разрядов с инверсными информационными выходами названных логических пар, причем информационный вход логической пары элементов 2И-НЕ ввода данных в JK-триггер нулевого разряда соединен с входом ПДК младшего разряда IpKt второй кодовой шины, а счетчик импульсов включает также группу из n элементов совпадения межразрядной связи и цепь сквозного переноса из n-2 элементов совпадения, а J и K-входы JK-триггера нулевого разряда соединены с Q-выходом управляющего RS-триггера,

-входы JK-триггеров нулевого и n-го разрядов с инверсными информационными выходами названных логических пар, причем информационный вход логической пары элементов 2И-НЕ ввода данных в JK-триггер нулевого разряда соединен с входом ПДК младшего разряда IpKt второй кодовой шины, а счетчик импульсов включает также группу из n элементов совпадения межразрядной связи и цепь сквозного переноса из n-2 элементов совпадения, а J и K-входы JK-триггера нулевого разряда соединены с Q-выходом управляющего RS-триггера,  -выход которого соединен с 2(n+1) управляющими входами логических пар элементов 2И-НЕ схемы параллельного ввода данных и с первым входом первого элемента 2И-НЕ инверсной логики межразрядной связи, второй вход которого соединен с Q-выходом JK-триггера нулевого разряда, а выход с J и K-входами JK-триггера первого разряда, Q-выход которого соединен с J и K-входами JK-триггера второго разряда, с первым входом первого элемента 2И-НЕ инверсной логики цепи сквозного переноса, второй вход которого соединен с Q-выходом JK-триггера второго разряда, и первый вход второго элемента 2И-НЕ инверсной логики межразрядной связи также соединен с Q-выходом JK-триггера первого разряда, а второй с

-выход которого соединен с 2(n+1) управляющими входами логических пар элементов 2И-НЕ схемы параллельного ввода данных и с первым входом первого элемента 2И-НЕ инверсной логики межразрядной связи, второй вход которого соединен с Q-выходом JK-триггера нулевого разряда, а выход с J и K-входами JK-триггера первого разряда, Q-выход которого соединен с J и K-входами JK-триггера второго разряда, с первым входом первого элемента 2И-НЕ инверсной логики цепи сквозного переноса, второй вход которого соединен с Q-выходом JK-триггера второго разряда, и первый вход второго элемента 2И-НЕ инверсной логики межразрядной связи также соединен с Q-выходом JK-триггера первого разряда, а второй с  -выходом триггера второго разряда, и выход его соединен с J и K-входами JK-триггера третьего разряда, а выход i-го элемента совпадения цепи сквозного переноса, начиная с первого, соединен с первым входом (i+1)-го элемента 2И цепи сквозного переноса и с первым входом (i+2)-го элемента 2И межразрядной связи, второй вход которого соединен с Q-выходом JK-триггера (i+2)-го разряда, а выход с J и K-входами JK-триггера (i+3)-го разряда, и второй вход (i+1)-го элемента 2И сквозного переноса соединен с

-выходом триггера второго разряда, и выход его соединен с J и K-входами JK-триггера третьего разряда, а выход i-го элемента совпадения цепи сквозного переноса, начиная с первого, соединен с первым входом (i+1)-го элемента 2И цепи сквозного переноса и с первым входом (i+2)-го элемента 2И межразрядной связи, второй вход которого соединен с Q-выходом JK-триггера (i+2)-го разряда, а выход с J и K-входами JK-триггера (i+3)-го разряда, и второй вход (i+1)-го элемента 2И сквозного переноса соединен с  -выходом JK-триггера (i+2)-го разряда, J-вход дополнительного (n+1)-го JK-триггера соединен с выходом n-го элемента 2 И межразрядной связи, первый вход которого соединен с выходом (n-2)-го элемента совпадения цепи сквозного переноса, а второй с Q-выходом JK-триггера n-го разряда, и

-выходом JK-триггера (i+2)-го разряда, J-вход дополнительного (n+1)-го JK-триггера соединен с выходом n-го элемента 2 И межразрядной связи, первый вход которого соединен с выходом (n-2)-го элемента совпадения цепи сквозного переноса, а второй с Q-выходом JK-триггера n-го разряда, и  -выход (n+1)-го JK-триггера соединен с входом выходного инвертора, а Q-выход с управляющим входом "Равно" (A B элемента сравнения кодов, n входов группы входов A которого поразрядно соединены с Q-выходами JK-триггеров первого, i-го, (n-1)-го разрядов и с

-выход (n+1)-го JK-триггера соединен с входом выходного инвертора, а Q-выход с управляющим входом "Равно" (A B элемента сравнения кодов, n входов группы входов A которого поразрядно соединены с Q-выходами JK-триггеров первого, i-го, (n-1)-го разрядов и с  -выходом JK-триггера n-го разряда счетчика импульсов, а выход "Равно"

-выходом JK-триггера n-го разряда счетчика импульсов, а выход "Равно"  второго инвертора соединен с

второго инвертора соединен с  -входами (n+1)-го триггера и управляющего RS-триггера.

-входами (n+1)-го триггера и управляющего RS-триггера.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР N 1592941, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-11-10—Публикация

1993-03-01—Подача