Известны пороговые регистраторы, содержащие реверсивный счетчик и генератор опорного сигнала. Однако они не обладают требуемой точностью.

Предлагаемый пороговый регистратор содержит две схемы совпадения и два дешифратора. При этом выходы разрядов реверсивного счетчика через дешифраторы подключены к входам схем совпадения, выходы которых соединены с входами реверсивного счетчика. Такое выполнение повышает точность устройства.

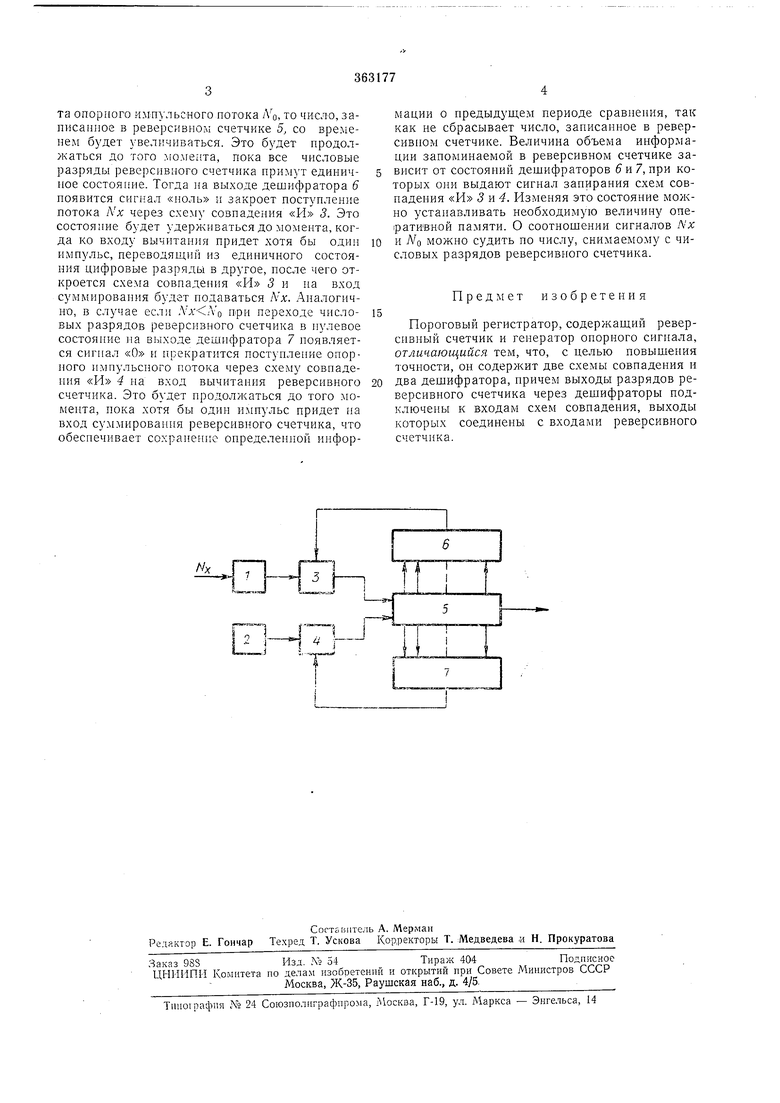

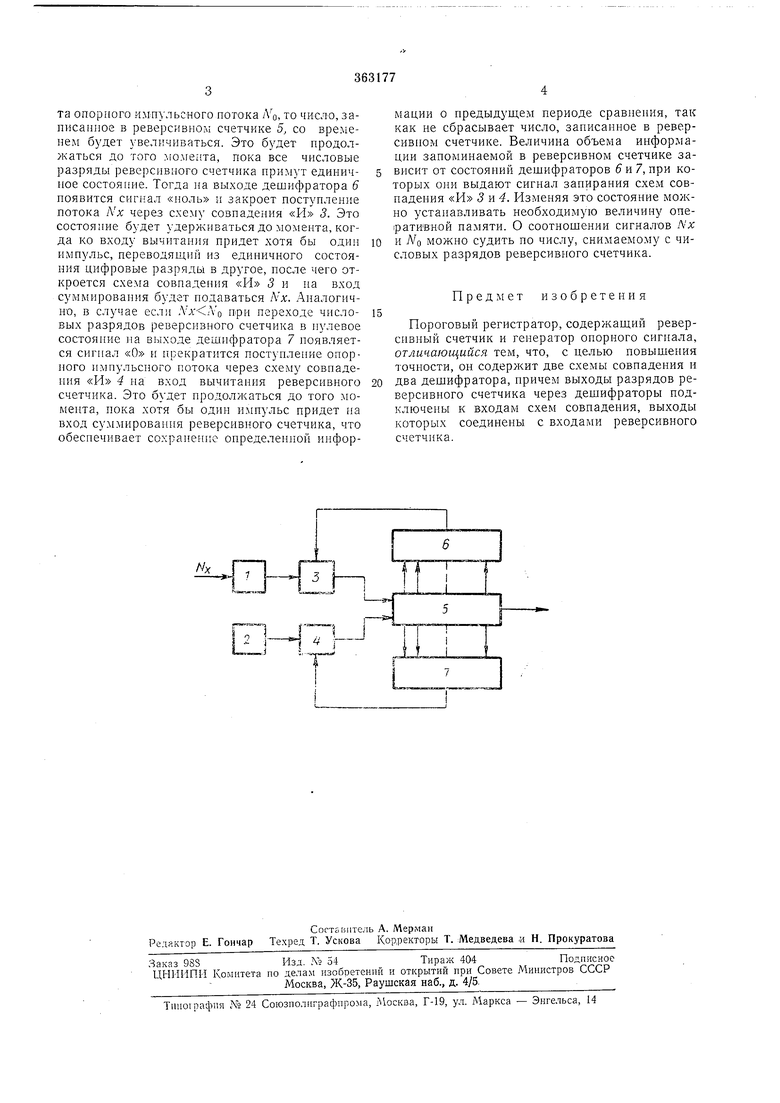

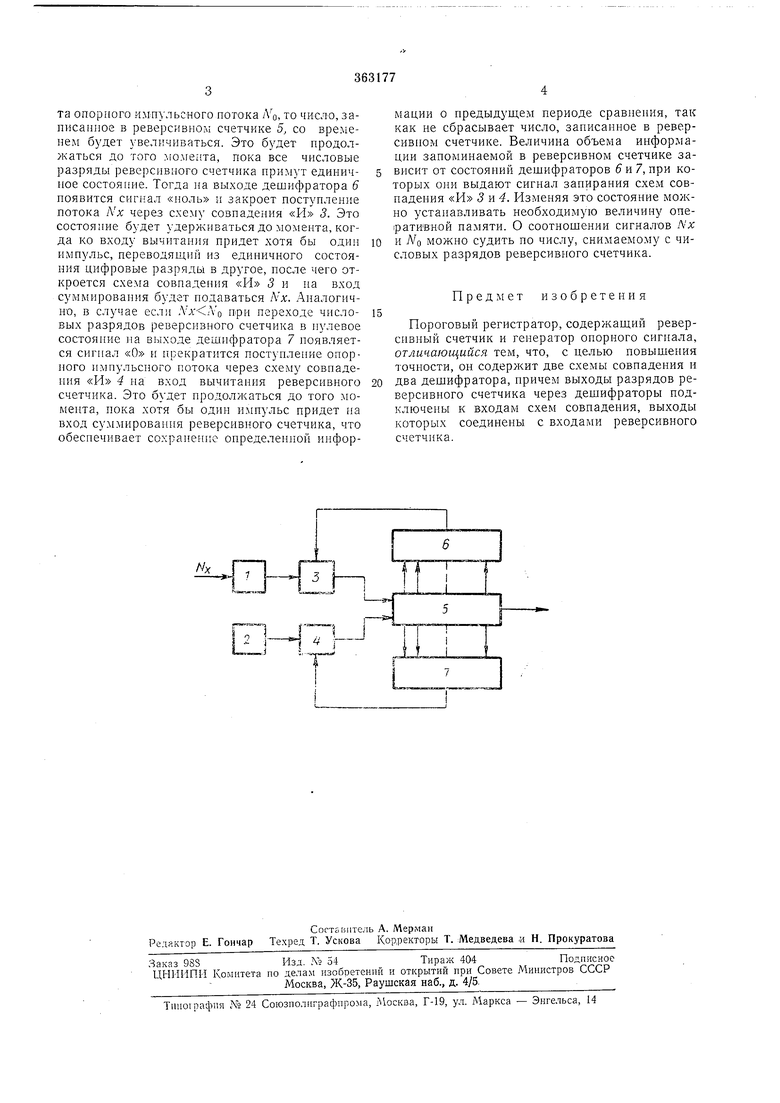

На чертеже приведена блак-схема устройства.

Она содержит входные клеммы /, генератор опорного сигнала 2, схема совпадения «И 3, схема совпадения «И 4, реверсивный счетчик 5, дешифратор 6 и дешифратор 7.

Кабель, по которому подается анализируемый сигнал, подключен к входным клеммам 1, соединенным с входом схемы совпадения «И 3. Выход схемы совпадения «И 3 соединен с входом «суммирования реверсивного счетчика 5, второй вход схемы совпадения «И 3 соединен с входом дешифратора 6.

Выход генератора опорного сигнала 2 соединей с входом схемы совпадения «И 4. Второй вход схемы совпадения «И 4 соединен с выходом дешифратора 7, а выход схемы совпадения «И 4 соединен с входом «вычитания реверсивного счетчика 5.

Входы дешифраторов 6, / подключены к выходам числовых разрядов реверошного счетчика 5.

В зависимости от того, необходимо ли регистрировать порог превышения средней , скорости счета анализируемого сигнала над средней скоростью счета опорного сигнала или порог превышения средней скорости счета опорного сигнала над средней скоростью счета анализируемого сигна.а, выход генератора опорного сигнала 2 может быть подключен к входу схемы совпадения «И 3 и входные клеммы 1 анализируемого сигнала к входу схемы совпадения «И 4.

Предположим что на выходе дешифратора 6 появляется сигнал «О только в том случае, если в реверсивном счетчике 5 все числовые разряды находятся в единичном состоянии, а на выходе дешифратора 7 появляется сигнал «О только в том случае, если в реверсивном счетчике 5 все 4HCviOBbie разряды находятся в нулевом состоянии.

Импульсные потоки от входных клемм У и от генератора опорного с 1гнала 2 через схемы совпадения «И 3 и 4 поступают на соответствующие входы реверсивного счетчика 5. В реверсивном счетчике 5 происходит вычитание импульсных потоков. В случае, если средняя скорость счета анализируемого импульсного потока .V.;t будет -больше средней скорости счета опорного и.М:пульсного потока NO, то число, записанное в реверсивном счетчике 5, со временем будет увеличиваться. Это будет продолжаться до того момента, пока все числовые разряды реверсивного счетчика примут единичное состояние. Тогда па выходе дешифратора 6 появится сигнал «ноль и закроет поступление потока NX через схему совпадения «И 3. Это состояние будет удерживаться до момента, когда ко входу вычитания придет хотя бы один импульс, переводящий из единичного состояния цифровые разряды в другое, после чего откроется схема совпадения «И 3 и на вход суммирования будет подаваться Л-.. Аналогично, в случае если ирн переходе чнсловых разрядов реверсивного счетчика в нулевое состояние на выходе дешифратора 7 ноявляется сигнал «О и прекратится поступление опорного импульсного потока через схему совпадения «И 4 на вход вычитания реверсивного счетчика. Это будет продолжаться до того момента, пока хотя бы один импульс придет на вход суммирования реверсивного счетчика, что обеснечивает сохране н;е определенной информации о предыдущем периоде сравнения, так как не сбрасывает число, записанное в реверсивном счетчике. Величина объема информации запоминаемой в реверсивном счетчике зависит от состояний дешифраторов б и 7, при которых они выдают сигнал запирания схем совпадения «И 3 и4. Изменяя это состояние можно устанавливать необходимую величину оперативной памяти. О соотношении сигналов Лх и можно судить по числу, снимаемому с числовых разрядов реверсивного счетчика.

Предмет изобретения

Пороговый регистратор, содержащий реверсивиый счетчик и генератор опорного сигнала, отличающийся тем, что, с целью повышения точности, он содержит две схемы совпадепия и два дешифратора, причем выходы разрядов реверсивного счетчика через дешифраторы подключены к входам схем совпадения, выходы которых соединены с входами реверсивного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ИЗМЕРЕНИЯ ОТНОШЕНИЯ СРЕДНИХ СКОРОСТЕЙ СЧЕТА ДВУХ ИМПУЛЬСНЫХ ПОТОКОВ | 1971 |

|

SU310188A1 |

| Устройство для измерения интервала электрокардиосигнала | 1976 |

|

SU606577A1 |

| ФОТОЭЛЕКТРИЧЕСКОЕ СЛЕДЯЩЕЕ УСТРОЙСТВО | 1971 |

|

SU305442A1 |

| КОРРЕЛЯТОР | 1972 |

|

SU432510A1 |

| СИНУСНО-КОСИНУСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1970 |

|

SU283693A1 |

| ФОТОЭЛЕКТРИЧЕСКИЙ ГИД ТЕЛЕСКОПА | 1969 |

|

SU243879A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЙ ПО СКОЛЬЗЯЩЕЙ ВЫБОРКЕ | 1973 |

|

SU432516A1 |

| ПРЕОБРАЗОВАТЕЛЬ «НАПРЯЖЕНИЕ— КОД». | 1968 |

|

SU209086A1 |

| ЦИФРОВОЙ АНАЛИЗАТОР ВРЕМЕИНЫХ ХАРАКТЕРИСТИК ТРАНЗИСТОРНЫХ СХЕМ | 1971 |

|

SU297011A1 |

| СЧЕТЧИК С ПРЕДУСТАНОВКОЙ | 1970 |

|

SU269207A1 |

I

.,

.

асцг п дддцж, „ ц.едгЛ

Авторы

Даты

1973-01-01—Публикация