1

Изобретение относится к снециализированным средствам вычислительной техники и может быть использовано для решения ряда статистических задач радиотехники, систем автоматического управления, физики, связи и других областей науки и техники.

Известен коррелятор, содержащий схему сравнения, вентили, дешифратор, счетчики, триггеры, характеризующийся сложностью аппаратуры и невысокой точностью, объясняемыми наличием в его составе управляемой линии задержки, включенной в цепь одного из входных сигналов. Эта линия задержки предназначена для предварительной временной задержки на интервал корреляции одного из процессов с целью получения возможности вычисления взаимной корреляционной функции в области отрицательных значений аргумента.

Целью изобретения является повышение точности коррелятора. Это достигается введением в состав прибора двух дополнительных переключателей, схемы «ИЛИ, реверсивного адресного счетчика запоминающего устройства, а также соответствующими связями между известными и вновь введенными лементами коррелятора. Коррелятор в таком исполнении исключает необходимость в управляемой линии задержки, что обеспечивает повышение его точности и упрощение конструкции.

В описываемом корреляторе для положительных аргументов реализуется следующая зависимость

Р, (иД) КI у (t, -f i.A)/.x (t A (1)

i-i

При изменении |LI от нуля до -Ьцмакс. происходит вычисление первой части корреляционной функции р.х-(/(т). Вычисление второй ее части, соответствующей отрицательному аргументу, заменяется вычислением корреляционной функции рг/.г-(т), поскольку справедливо соотношение

(-) Руж(+)

При этом реализуется следующая зависимость

Р,(- fiiO Pyx(Д) Ky,x(t, fiA) X

x/y(,)n

(2)

Автокорреляционные функции могут быть вычислены по любой из зависимостей (1) или

(2), полагая при этом x(ti)y(ti). Поскольку автокорреляционная функция является частным случаем взаимной корреляционно функции, описание работы коррелятора про 1зведем на iipiiMepe вь 4 сления корреляционной функции (ВКФ).

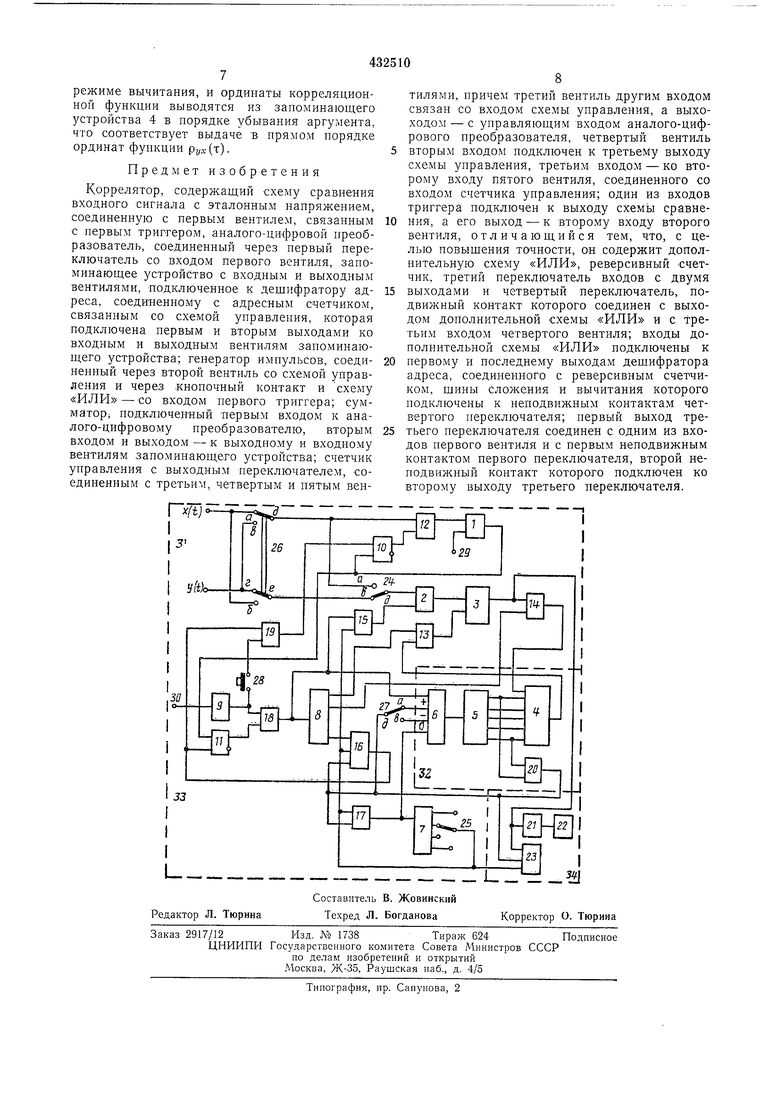

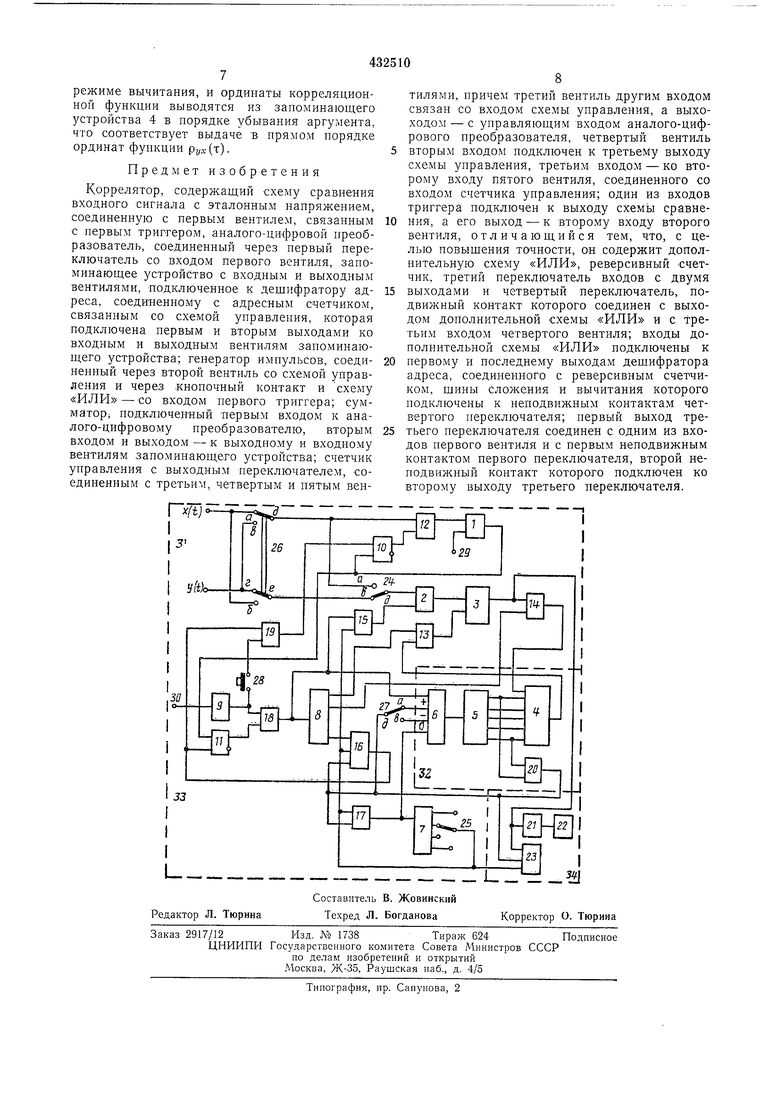

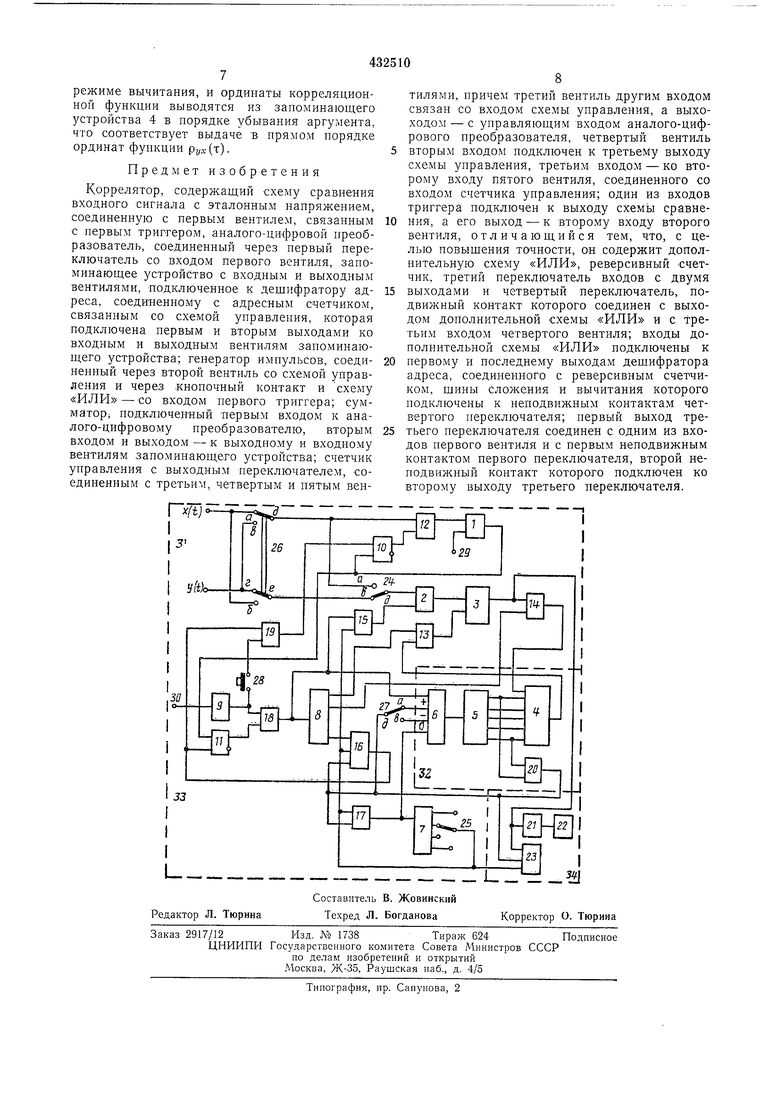

Блок-схема коррелятора показана на чертеже.

Коррелятор содержит схему сравнения 1, аналого-цифровой преобразователь 2, сумматор 3, запоминающее устройство 4, дешифратор адреса 5, адресный счетчик 6, счетчик управления 7, схему (устройство) управления 8, генератор импульсов 9, триггеры 10 и И, вентили 12-18, схемы «ИЛИ 19 и 20, преобразователь кодов в напряжения 21, электронный осциллограф 22, выходной разъем 23, переключатели 24-27 и кнопочный контакт 28. На схеме коррелятора обозначены: 29 - вход установки уровня анализа схемы сравнения 1; 30-вход установки частоты генератора импульсов 9; 31-34 - блоки коррелятора - блок ввода и вычисления, блок накопления и заноминация, блок управления и выходной блок соответственно.

Контакты «а и «б переключателя 26 подключены к источнику первого входного сигнала, а контакты «в и «г - к источнику второго сигнала. Общий контакт «д нервой половины переключателя 26 соединен с первым входом вентиля 12 и с контактом «а переключателя 24, контакт «в которого подключен к общему контакту «е второй половины переключателя 26, а контакт «д - к основному входу аналого-цифрового преобразователя 2. Вентиль 12 подключен ко входу схемы сравнения 1, выход которой соединен с нулевым входом триггера 10 и единичным входом триггера 11. Выход триггера 10 подключен к управляющему входу вентиля 12, а единичный вход - к выходу схемы «ИЛИ 19. Аналого-цифровой нреобразователь 2 связан с первым входом сумматора 3, выход которого подключен ко входам вентиля 14 и преобразователя кодов в напряжения 21, а также к выходному разъему 23, предназначенному для связи коррелятора с Э.В.М. Выход преобразователя 21 подключен к электронному осциллографу 22, предназначенному для визуального наблюдения вычисленных корреляционных функций, а выход вентиля 14 - ко входу запоминаюпдего устройства 4, выход которого связан с вентилем 13, подключенным ко второму входу сумматора 3. Генератор импульсов 9 подключен через кнопочный контакт 28 ко входу схемы «ИЛИ 19 и неносредственно-к основному входу вентиля 18, связанного со входами схемы управления 8, адресного счетчика 6 и вентиля 15, выход которого соединен со входом запуска аналогоцифрового преобразователя 2, работающего в ждущем режиме. Первый, второй и третий выходы схемы управления 8 подключены соответственно к управляющим входам вентилей 13, 14 и 16, выход последнего из которых связан со входом схемы «ИЛИ 19 и нулевым входом триггера 11, единичным выходом соединенного с управляющим входом вентиля 18. Адресный счетчик 6 запоминающего устройства 4 является реверсивным, он имеет 2,Цыакс. состояний, ИЗ которых одна половина

состоянии соответствует положительному знаку, а вторая - отрицательному (знак определяется ноложением знакового разряда). Выход адресного счетчика 6 подключен к дешифратору адреса 5, выходы которого соединены с адресными входами заноминающего устройства 4. Первый и последними выходы адресного дещифратора 5 подключены также через с.хему «ИЛИ 20 к выходному разъему 23, ко входам вентнля 16 и к общему контакту «д переключателя 27, предназначенного для управления режимом работы (режим суммирования или вычитания) реверсивного счетчика 6. Контакты «а и «в этого переключателя связаны соответственно с щинамн управления су| :мированием и вычитанием счетчика 6. Выход вентиля 17 соединен со входом установки в нулевое состояние счетчика 6 и счетным входом счетчика управления 7, выходы которого через переключатель 25, служащий для задания необходимого числа ординат процесса, но которым производится вычисление каждого значения корреляционной функции, связаны с выходным разъемом 23 и входами вентилей 15-17.

Перед вычислением первой части ВКФ в соответствии с зависимостью (1) переключатели 24, 26 и 27 устанавливаются в положение, показанное на чертеже, а с иомощью переключателя 25 задается необходимое число ординат второго процесса, по которым будет производиться вычисление каждой ординаты корреляцио;пюй функции. При этом адресный счетчик 6 будет в нулевом состоянии и подготовлен к режи.му суммирования. На входе 29 схемы сравнения 1 будет установлено нанряжение, соответствуюидее выбранному уровню анализа, а но входу управления 30 - задаваться частота генератора импульсов 9 так, чтобы на интервал корреляции Тмакс. приходилось около |„.макс. периодов импзльсов.

Работа коррелятора начинается после замыкания кнопочного контакта 28. При этом имнульс генератора 9 через схему «ИЛИ 19 поступает па триггер 10 н устанавливает его в единичное состояние; вентиль 12 открывается и входной процесс поступает на вход схемы сравнения 1. При достижении процессом x(t) заданного уровня анализа X схема сравнения I вырабатывает импульс, который устанавливает триггер 10 в нулевое состояние, в результате чего вентиль 12 закрывается. Импульс с выхода схемы сравнения 1 поступает также на триггер 11 и устанавливает его в единичное состояпие. При этом вентиль 18 открывается, и первый импульс генератора 9 поступает на вход адресного счетчика 6, устанавливая в нем «единицу, на вход схемы управления 8, которая на каждый входной импульс вырабатывает сигналы последовательно на всех своих выходах, а также через открытый вентиль 15-на вход запуска аналого-цифрового преобразователя 2. Преобразователь 2, работающий в ждущем режиме, в момент поступления импульсов с вентиля 15 преобразует ординату непрерывно поступающего на его вход второго процесса в код и передает этот код в сумматор 3. Дешифратор 5, подключенный к счетчику 6, дешифрирует состояние счетчика б с учетом его знакового старшего разряда. Поскольку после прихода первого импульса в счетчике 6 устапавливается положительное число, равное «единице, дешифратор 5 вырабатывает сигнал на выходе, соответствующий адресу середины массива запоминающего устройства 4. По сигналу с первого выхода схемы управления 8, который появляется после передачи кода ординаты второго процесса из преобразователя 2 в сумматор 3, содержимое выбранной ячейки запоминающего устойства 4 считывается, передает. ся в сумматор 3 и суммируется с кодом ординаты второго процесса. Сигнал со второго выхода схемы управления 8 открывает вентиль 14 и записывает образовавшуюся сумму в ту же ячейку запоминающего устройства 4. Сигнал с третьего выхода схемы управления 8 через .вентиль 6 не проходит, поскольку он остается закрытым до тех пор, пока не появляется разрешающий сигнал на выходе схемы «ИЛИ 20, соответствующий моменту образования сигнала на последней (нижней) шине дешифратора 5. Следующий импульс генератора 9 через заданный интервал повторит все описанные операции с той лишь разницей, что аналого-цифровой преобразователь 2 передает в сумматор 3 код второй ординаты второго процесса, который просуммируется с содержимым следующей ячейки запоминающего устройства 4, поскольку в адресном счетчике 6 будет число «два.

Описанные операции повторяются до тех пор, пока не будет обработано таким образом (Лмакс. ординат процесса. При этом сигнал, образовавшийся на последнем (нижнем) выходе дешифратора, пройдет через схему «ИЛИ 20, подтвердит режим суммирования счетчика 6, откроет вентиль 16 и, пройдя через вентиль 17, установит в счетчике 6 нулевое число, а в счетчике управления 7 - «единицу. После этого сигнал с третьего выхода схемы управления 8 пройдет через открывшийся вентиль 16, установит триггер 11 в нулевое состояние, в результате чего вентиль 18 закроется, и, пройдя через схему «ИЛИ 19, установит триггер 10 в единичное состояние. При этом вентиль 12 откроется и первый входной процесс будет вновь поступать на схему сравнения 1. При достижении этим процессом заданного уровня анализа схема сравнения вновь срабатывает, и повторяется цикл обработки следующих ординат заданного числа второго процесса, каждая из которых задержана относительно момента срабатывания схемы сравнения 1 на вре.мя цА В каждом таком цикле ординаты второго процесса преобразуются в код и суммируются с суммой иредыдущих ординат по каждому значению .i. В конце последнего цикла работы на общей клемме переключателя 25, с помощью которого задавалось число циклов, появляется сигнал, который закрывает вентили 15-17, в результате чего вычисление первой части ВКФ прекращается. При этом во второй половине

запоминающего устройства 4 располагаются

числа, пропорциональные ординатам при

всех положителы;ых дискретных значениях

аргумента.

Для вычисления второй половины ВКФ в

соответствии с завис;1мостью (2) переключатели 26 и 27 устанавливаются в положения, противоположные показанным на чертеже. При этом nepBbiii процесс поступает на аналого-цифровой преобразователь 2, а второй процесс - через вентиль 12 на схему сравнения 1; счетчик адреса 6 будет подготовлен к режиму вычитания. В этом режиме вычисления коррелятор работает аналогично описанному, разница заключается лишь в том, что преобразуются в код и накапливаются теперь ординаты первого процесса, и полученные сум: ;ui орД1Ь:ат по каждому значению ц располаriborcH в первой половине ячеек запоминающего устройства 4. После прекращения вычислений зторой части ВКФ в запоминающем устройстве 4 по порядку располагаются ординаты ВКФ всех отрицательпых дискретных значениях аргулепта. После окончания вычислений начинается

режш; вывода рез -льтатов. При этом переключатель 27 устанавливается в положение, показанное на чертеже. В этом режиме сигпллом с переключателя 25 вентили 15-17 закрываются, а счетчик 6 подготовлен к режиму

суммирования.

При выводе результатов на каждый импульс генератора 9 происходит увеличение числа в адресном счетчике 6, чтение числа из соответствующей ячейки запоминающего устройства 4 и передача этого числа через вентиль 13 в сумматор 3. Это число из сумматора 3 поступает на выходной разъем 23, преобразователь кодов в напряжении 21 и через вентиль 14 записывается вновь в ячейку запоминающего устройства 4 по прежнему адресу. Число в счетчике 6 увеличивается до максимального значения, затем возникает переполнение счетчика 6, и число в нем скачком изменяется до -Цмакс., после чего оно вновь увеличивается.

При циклическом изменении адреса запоминающего устройства 4 от зпачения -iHMaitc. до значения +UMai;c. все ординаты ВКФ поочередно выводятся в сумматор 3, преобразователь кодов в напряженпя 21 и выходной разъем 23. На экране электронного осциллографа 22, подключенного к выходу преобразователя 21, наблюдается график выводимой функции. Многократный циклический вывод результатон обеспечивает воспроизведение на экране осциллографа 22 устойчивого изображения. При выводе результатов вычислений переключатель 27 может быть установлен в положение, когда замкнуты контакты «в и «д.

В этом случае адресный счетчик 6 работает в

режиме вычитания, и ординаты корреляционной функции выводятся из запоминающего 5стройства 4 в норядке убывания аргумента, что соответствует выдаче в прямом цорядке ординат функции рг/х(т).

Предмет изобретения

Коррелятор, содержащий схему сравнения входного сигнала с эталонным напряжением, соединенную с первым вентилем, связанным с первым триггером, аналого-цифровой нреобразователь, соединенный через первый переключатель со входом первого вентиля, запоминающее устройство с входным и выходным вентилями, подключенное к дещифратору адреса, соединенному с адресным счетчиком, связанным со схемой управления, которая подключена первым и вторым выходами ко входным и выходным вентилям запоминающего устройства; генератор импульсов, соединенный через второй вентиль со схемой управления и через кнопочный контакт и схему входом первого триггера; сумматор подключенный первым входом к аналого-цифровому преобразователю, вторым входом и выходом - к выходному и входному вентилям запоминающего устройства; счетчик управления с выходным переключателем, соединенным с третьим, четвертым и пятым вентилями, причем третий вентиль другим входом связан со входом схемы управления, а выхоходом - с управляющим входом аналого-цифрового преобразователя, четвертый вентиль вторым входом подключен к третьему выходу схемы управления, третьим входом - ко второму входу пятого вентиля, соединенного со входом счетчика управления; один из входов триггера подключен к выходу схемь сравнения, а его выход - к второму входу второго вентиля, отличающийся тем, что, с целью повыщения точности, он содержит дополнительную схему «ИЛИ, реверсивный счетчик, третий переключатель входов с двумя

выходами и четвертый переключатель, подвижный контакт которого соединен с выходом дополнительной схемы «ИЛИ и с третьим входом четвертого вентиля; входы дополнительной схемы «ИЛИ подключены к

первому и последнему выходам дещифратора адреса, соединенного с реверсивным счетчиком, шины сложения и вычитания которого подключены к неподвижным контактам четвертого переключателя; первый выход третьего переключателя соединен с одним из входов первого вентиля и с первым неподвижным контактом первого переключателя, второй неподвижный контакт которого подключен ко второму выходу третьего переключателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯТОР | 1973 |

|

SU374607A1 |

| Цифровой коррелятор | 1980 |

|

SU940172A1 |

| Цифровой коррелятор | 1982 |

|

SU1045233A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Цифровой коррелятор | 1980 |

|

SU903892A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Устройство для определения взаимной корреляционной функции | 1987 |

|

SU1427383A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВЕРОЯТНОСТНЫХ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU432512A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

Даты

1974-06-15—Публикация

1972-06-05—Подача