1

Известны преобразователи разности частот двух сигналов в код, содержащие блок управления, ключ, счетчик результата, два двоичных умножителя, состояндих из управляющего счетчика, счетчика и системы ключей, и генератор опорной частоты, соединенный с входом первого двоичного у.11южителя.

Цель изобретения - повыщение быстродействия устройства.

Это достигается тем, что выход первого двоичного умножителя соединен со входом второго, выход последнего - со счетными в.ходами управляющих счетчиков двоичных Змножителей и со счетным входом счетчика результата через ключ, управляющий вход которого соединен с первым выходом блока управления, другой выход которого подключен к установочны.м входа м управляющих счетчиков и счетчика результата. При этом два входа блока управления соединены с входными клеммами преобразователя, а третий вход - с выходом генератора опорной частоты.

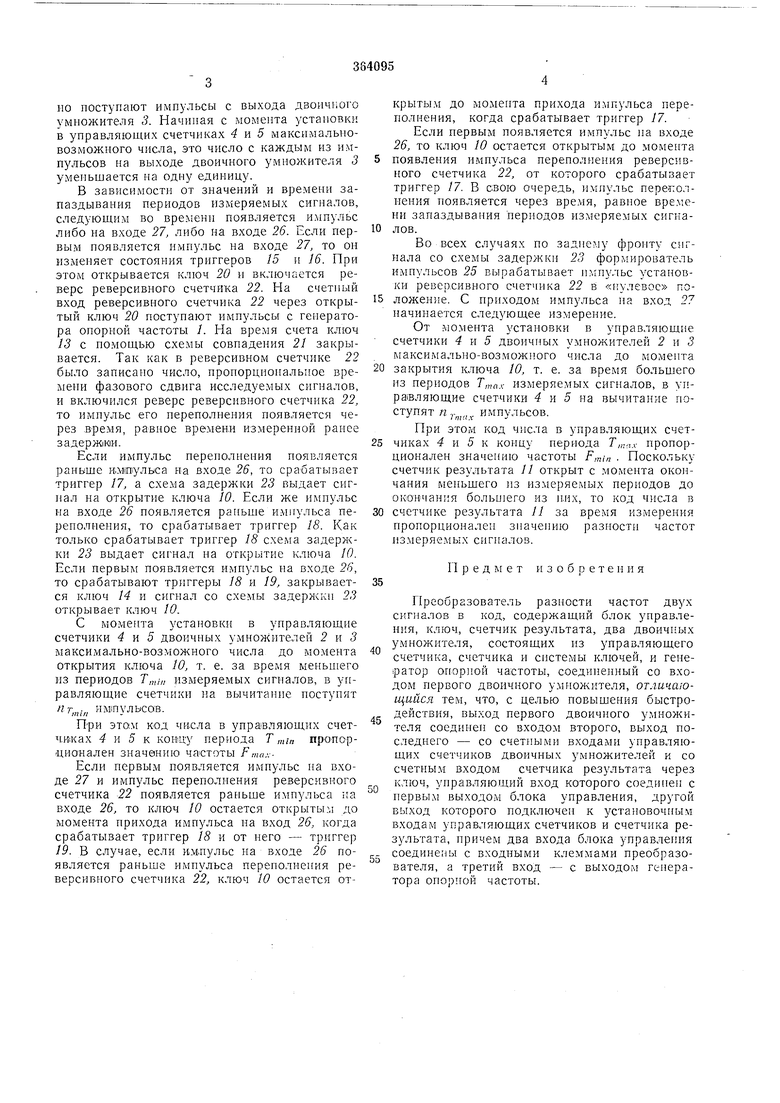

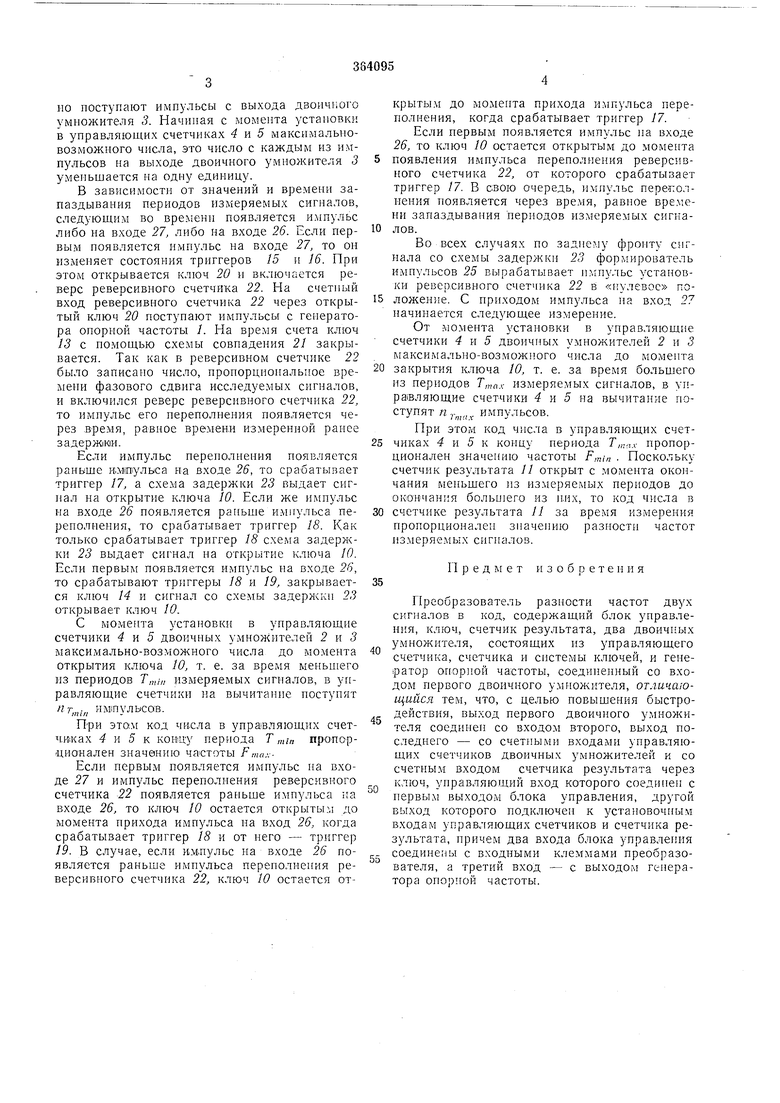

На чертеже приведена блок-схема устройства.

Устройство содержит генератор опорной частоты У, два двоичных умножителя 2 и 3, каждый из которых состоит из управляющих счетчиков 4 и 5, систем ключей 6 и 7, счетчиков S и 5, ключ 10, счетчик результата У/ и блок управления 12, в состав

которого входят ключи 3 и 14, триггеры 15- 19, ключ 20, схема совпадения 21, реверсивный счетчик 22, схема задержки 23, ключ 24 и формирователь импульсов 25. На входе 26 и 27 поступают импульсы сигналов, разностную частоту которых необходпмо измерить.

С появлением опорного импульса на входе 27 срабатывают триггеры 15, 16 и 19. При

этом открываются ключи 14 и 20 и импульсы с выхода генератора опорной частоты / ноступают на счетный вход реверсивного счетчика 22 (на сложение или вычитание в зависимости от положения триггера 16.

От имиульса измеряемого сигнала со входа 26 через открытые ключи 13 и 14 срабатывают триггеры 15, 17 и 18. При срабатывании триггера 15 закрывается ключ 20. К этому моменту времени код в реверсивном счетчике

22 пропорционален времени фазового сдвига исследуемых сигналов. Этот код хранится до определенного момента в реверсивном счетчике 22.

При срабатывании триггера 18 с его выхода формируется имиульс установки в управляющие счетчики 4 } 5 двоичных умножителей .2 и 3 максимально-возможного числа и «нулевого положения счетчика результата 11, а также закрывается ключ 13. На счетные

входы управляющих счетчиков 4 и 5 постоянно поступают импумьсы с выхода двоичного умножителя 3. Начиная с момента установки в управляющих счетчиках 4 и 5 максимальновозможного числа, это число с каждым из импульсов на выходе двоичного умножителя ,3 уменьшается на одну единицу.

В зависимости от значений и времени запаздывания периодов измеряемых сигналов, следующим во появляется импульс либо на входе 27, лнбо на входе 26. Если первым появляется импульс на входе 27, то он изменяет состояния триггеров 15 и 16. При этом открывается ключ 20 и включается реверс реверсивного счетчика 22. На счетный вход реверсивного счетчика 22 через открытый ключ 20 постунают импульсы с генератора опорной частоты 1. На время счета ключ 13 с помощью схемы совпадения 21 закрывается. Так как в реверсивном счетчике 22 было записано число, пропорциональное времени фазового сдвига исследуемых сигналов, и включился реверс реверсивного счетчика 22, то импульс его переполнения появляется через время, равное времени измеренной ранее задерЖ|К1и.

Если импульс переполнения появляется раньше и,м1П1ульса на входе 26, то срабатывает триггер 17, а схема задержки 23 выдает снгнал на открытие ключа 10. Если же имнульс на входе 26 появляется раньше нмиульса переполнения, то срабатывает триггер 18. Как только срабатывает триггер 18 схема задержки 23 выдает сигнал на открытие ключа 10. Если первым появляется импульс на входе 26, то срабатывают триггеры 18 и 19, закрывается ключ 14 и сигнал со схемы задерлчкн 23 открывает ключ 10.

С момента установки в управляющие счетчики 4 и 5 двоичных у.множителей 2 к 3 максимально-возможного чнсла до момента открытия ключа 10, т. е. за время меньнюго из периодов Т,,,/,: измеряемых сигналов, в управляющие счетчики на вычитание поступят «/-„,,„ имшульсов.

При этом код числа в управляющих счетчи1ках - и 5 к концу периода Т „,,-„ пропсрционален значению частоты F,,,a.:.

Если первым появляется импульс на входе 27 и импульс переполиения реверсивного счетчика 22 появляется раньше импульса на входе 26, то ключ 10 остается открытым до момента ирихода импульса на вход 26, когда срабатывает триггер 18 и от него - триггер 19. В случае, если нмлульс на входе 26 появляется раньше нмпульса переполнения реверсивиого счетчика 22, ключ 10 остается открытым до момента прихода импульса нереполнения, когда срабатывает триггер 17.

Если первым появляется импульс па входе 26, то ключ 10 остается открытым до момента

появления импульса переполнения реверсивного счетчика 22, от которого срабатывает триггер 17. В свою Очередь, импульс пере колнения появляется через время, равное времени запаздывания периодов измеряемых сигналов.

Во всех случаях но заднему фронту сигнала со схемы задержки 23 формирователь импульсов 25 вырабатывает нмпульс установки ревер.сивного счетчика 22 в «нулевое положение. С нриходом импульса на вход 27 начинается следующее измерение.

От мо.мента установки в управляющие счетчики 4 и 5 двоичных умножителей 2 и 3 максимально-возможного числа до момента

закрытия ключа 10, т. е. за время большего из периодов Г,„ял- измеряемых сигналов, в унра1вляющие счетчики 4 и 5 на вычитание поступят Пу.д,,,. импульсов.

При этом код чнсла в управляющих счетчиках 4 и 5 к концу периода Г,,,,,,.- пропорционален значению частоты Fmin . Поскольку счетчик результата 11 открыт с момента окончания меньшего из нз.меряемых периодов до окончания больншго из шх, то код чнсла в счетчике результата // за время измерения нропорционален значению разности частот нз.меряе.мых сигналов.

Предмет изобретения

Преобразователь разности частот двух сигналов в код, содержащий блок управления, ключ, счетчик результата, два двоичных умножителя, состоящих из управляющего счетчика, счетчика и системы ключей, и генератор опорной частоты, соединенный со входом первого двоичного умножителя, отличающийся тем, что, с целью повышения быстродействия, выход первого двоичного умножителя соединен со входом второго, выход последнего - со счетными входами управляющих счетчиков двоичных умножителей и со счетным входом счетчика результата через

ключ, уиравляющий вход которого соединен с нервым выходом блока управления, другой выход которого подключен к установочным входам управляющих счетчиков и счетчика результата, нричем два входа блока управления

g соединены с входными клеммами преобразователя, а третий вход - с выходом генератора онорной частоты.

ni r-i Ur

) C| Й

--e li Ir

7

If.1 - I-..-:, .

1.e -) t i L i1

I-

тГ

U- ,-T

r-l

L

//,L

)-- I

л:.,

--.-ЛГ-жЛ Ьм-

„I

i

з

- j I

LmiJ

11

llf-p- гз

nU

:

4ir1Г Т LJ I

i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения первой разности частотно-импульсного сигнала | 1982 |

|

SU1043675A1 |

| Аналого-цифровой преобразователь сдвига фаз | 1981 |

|

SU955519A2 |

| Цифровой частотомер-фазометр | 1976 |

|

SU658496A1 |

| Умножитель частоты | 1980 |

|

SU868756A1 |

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

| Преобразователь переменного напряжения в код | 1985 |

|

SU1297226A1 |

| Умножитель частоты импульсного сигнала | 1972 |

|

SU447823A1 |

| Цифровой корреляционный фазометр | 1980 |

|

SU943598A1 |

| Устройство для вычисления плотностиНЕфТЕпРОдуКТОВ | 1979 |

|

SU811271A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

Даты

1973-01-01—Публикация