(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1983 |

|

SU1176439A1 |

| Устройство для измерения частоты | 1987 |

|

SU1465803A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Устройство для измерения отношения частот | 1983 |

|

SU1100574A1 |

| Следящий умножитель частоты | 1979 |

|

SU840892A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU993451A1 |

| Устройство для умножения частоты сигналов | 1974 |

|

SU528567A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано, в частности в быстродействующих устройствах измерения и преобразования число-импульсных сигналов. Известен умножитель частоты, содержащий формирователь, триггеры, генератор импульсов, элементы и гру пы элементов И, блок управления, ре гистры, счетчики, элемент ИЛИ и бло вычитания импульсов 1. Известен также умножитель частоты, содержащий формирователь, блок управления, элементы и группы элементов И и ИЛИ, регистры, счетчики, делитель частоты, блок вычитания и генератор .импульсов 2. Общим недостатком указанных умно жителей является относительно узкий диапазон умножаемых частот. Наиболее близким к предлагаемому является умножитель частоты, содержащий блок управления, подключенный первым импульсным входом к шине вво умножаемой частоты, вторым импульсным входом - к первому выходу генер тора сетки частот, счетным выходом к счетному входу измерителя периода выходом обнуления - ко входам обнуления измерителя периода и основного управляемого генератора, а первым управляющим выходом - к управляющему входу основного регистра, соединенного входами первой группы разрядов с информационными выходами измерителя периода, управляющий выход которого подключен к управлякяцему входу основного управляемого генератора, соединенного входами опорных частот с выходами генератора сетки частот, и выключатель частоты, выход которого является выходом умножителя частоты, а первый вход подключен к частотному выходу двоичного умножителя, соединенного частотным входом с выходом вычитателя частот, а информационными входами - с выходами разрядов основного регистра, вход управления считыванием которого подключен к выходу блока сравнения кодов, соединенного первой и второй группами входов с выходами разрядов основного регистра и с выходами измерителя периода соответственно, причем выход основного управляемого генератора подключен ко второму входу вычитателя частот и к третьему импульсному входу блока управления 13 .

Недостатком известного умножителя является то, что запаздывание при умножении изменяется в зависимости от значения входной умножаемой частоты при переходе из ..одного ,поддиапазона у множаемых частот в другой (величина поддиапазона определяется двухкратным изменением частоты). При этом в точках перехода из одного поддиапазона в другой появляется дополнительная погрешность за счет несогласованности кода периода, формируемого в измерителе периода, и кода поддиапазона, формируемого в управляемом генераторе.

Цель изобретения - повышение динамической точности, умножения.

Указанная цель достигается тем, что в умножитель частоты , содержащий блок управления, подключенный первым импульсным входом к шине ввода умножаемой част-оты, вторым импульсным входом - к первому выходу генератора сетки чартот,счетным выходом - к счетному, входу измерителя периода, выходом обнуления ко входам обнуления измерителя периода и основного управляемого генератора, а первым управляющим выходом к управляющему входу основного регистра, с9единенного. входамипервой группы разрядов с информационньоми выходами измерителя периода, управляющий выход которого подключен к управляющему входу основного управляемогго генера тора, соединенного входами опорных частот с выходами генератора сетки частот, и вычитатель частоты,, выход которого является выходом умножителя частоты, а первый вход подключен к частотному выходу двоичного умножителя, соединенного частотным входом с выходом вычит.ателя частот, введены группа из .дополни-; тельных регистров (где п - количество частот, формируемых генератором сетки частот), узел формирования задержки, формирователь импульсов и дополнительный управляемый генератор причем каждый () дополнительный регистр соединен выходами первой и второй групп разрядов соответственно со входами первой и второй групп разрядов (1+1)-го дополнительного регистра, а управляющим входом - с (1+1)-ыгл управляющим выходом блока управления, причем (п-1)-ый дополнительны.й регистр подключен выходами первой группы разрядов к инфор ационным входам двоичного умножителя, выходами второй группы разрядов - к информационным входам дополнительного управляемого генератор а управляющим входом - к п-ому управляющему выходу блока управления, соединенного третьим импульсным входом с выходом формирователя импульсов, с первым управляющим входом дво.ичного умножителя и со входом управления установкой кода дополнитель,ного управляемого генератора, а группой из п информационных входов -с первой группой выходов основного управляемого генератора, подключенного второй группой выходов ко входам второй группы разрядов основного регистра, выходы первой и второй групп разрядов которого соединены соответственно со входами первой и второй групп разрядов первого дополнительного регистра, причем дополнительный yпpaвляe лый генератор подключен входами опорных частот к выходам генера тора сеткичастот, а выходом - ко второму входу вычитате5 ля частот, причем шина ввода умножаемой частоты соединена с сигнальным входом узла формирования задержки, подключенного тактовым входом к соответствующему выходу генератора

0 сетки частот, а выходом - ко второму управляющему входу двоичного умножителя, соединенного управляющим выходом со входом формирователя импульсов .

Кроме того, блок управления содержит группу из п дешифраторов, группу из (п+1)-го элементов ИЛИ,две группы по п последовательно соединенных формирователей, п групп по п элементов И и ключ, выход которого является счетным выходом блока управления, первый вход соединен со входом первого формирователя первой. группы формирователей, а первый и второй входы ключа являются соответственно первым и вторым импульснш1и входами блока управления, причем каждый i-ый () элемент И каждой j-ой- () группы элементов И подключен первым входом к выходу / , (/1 - k/+l)-ro формирователя первой группы формирователей (где/i - k/модуль разности) , а вторым вхог.ом к выходу j-ro дешифратора, соединенного входами с информационными входами блока управления, причем каждый j-ый вход первого элемента ИЛИ подключен к выходу (n-j+l)-ro элемента Иj-oй группы элементов И, а

входы каждого k-ro. () элемента

ИЛИ соединены с выходами (k-l)-ыx элементов И всех групп элемен.тов И и с выходом (n-k+2)-ro формирователя второй группы формирователей,причем вход первого формирователя второй

5 группы формирователей является третьим импульсным входом блока управления, выход первого элемента ИЛИ является выходом обнуления блока управления, а выход каждого К.-го (2i-kin)

0 элемента ИЛИ - (К.-1)-ым управляющим

выходом блока управления.

При этом двоичный умножитель содержит группу элементов И, элемент 5 ИЛИ, счетчик и регистр, входы разрядов которого являются информационными входами двоичного умножителя, управляющий вход - первы л управляющим входом двоичного умножителя, а выходы разрядов подключены к первым входам элементов И, соединенных вторыми входами с выходами разрядов счетчика, счетный вход и вход обнуления которого являются соответственно частотным входом и вторым управляющим входом двоичного умножителя, а выход переполнения -.управляющим выходом двоичного умножителя причем выходы элементов И подключены ко входам элемента ИЛИ, выход которого является частотным выходом двоичного умножителя.

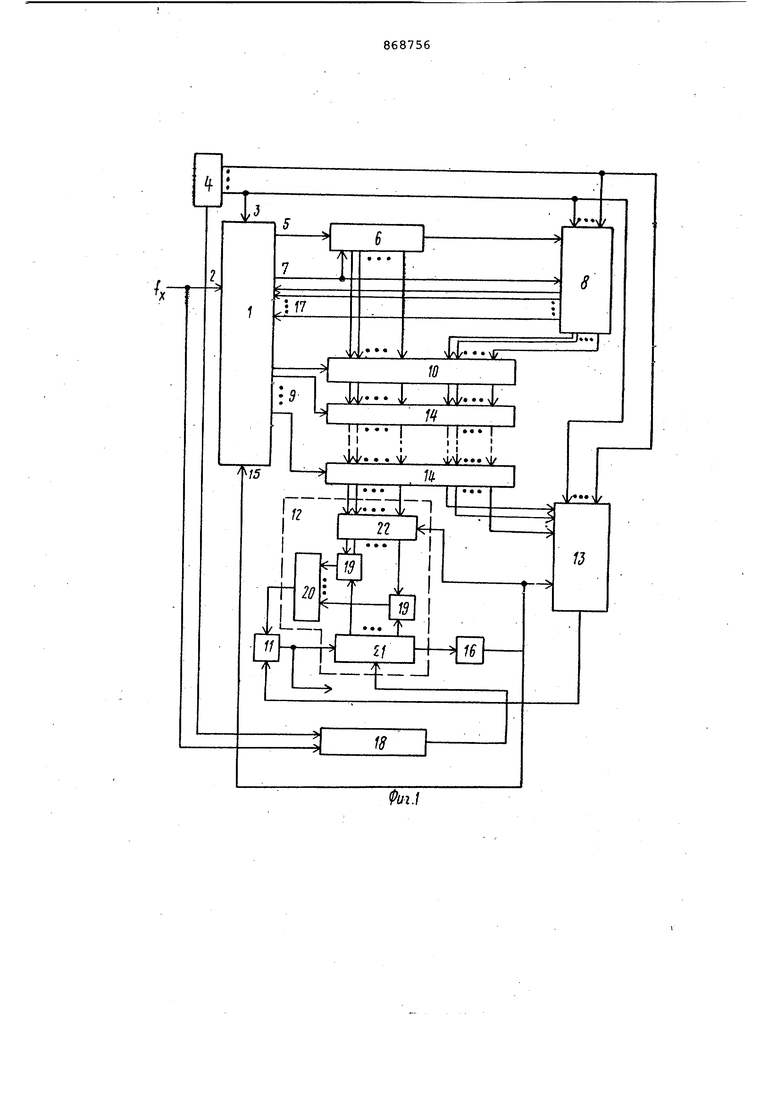

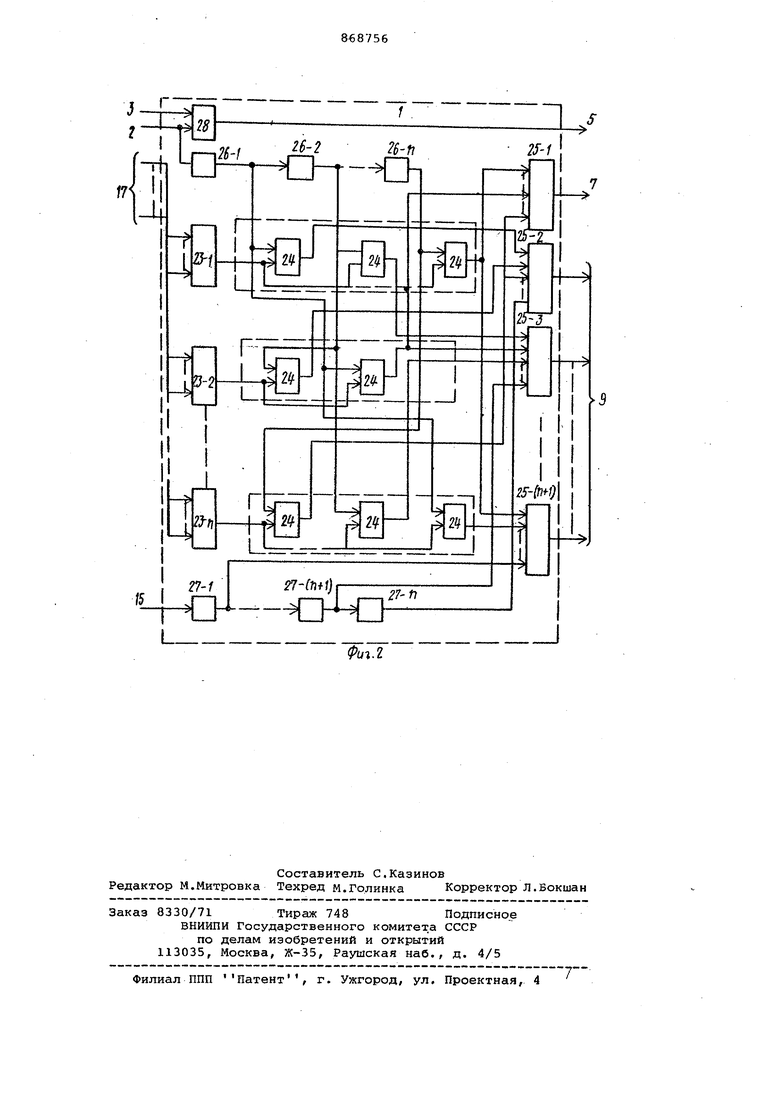

На фиг.1 показана блок-схема предлагаемого умножителя; на фиг.2 .структурная схема блока управления.

Умножитель частоты (фиг.1) содержит блок 1 управления, подключенный первым импульсным входом 2 к шине ввода умножаемой частоты, вторым импульсным входом 3 - к первому выходу генератора 4 сетки частот, счетным выходом 5 - к .счетному входу измерителя 6 периода, выходом 7 обнуления - ко входам обнуления измерителя 6 и основного управляемого генератора 8, а первым управляющим выходом 9 - к управляющему входу основного регистра 10, Регистр 10 соединен входами первой группы разрядов с информационными выходами измерителя 6, управляющий выход которого подключен к управляющему входу генератора 8, соединенного входами опорных, частот с выходами генератора 4.

Вычитатель 11 частот, выход которого является выходом умножителя частоты, подключен первыгл входом к частотному выходу двоичного умножителя 12, а вторьв.1 входом - с выходом дополнительного управляемого генератора 13. Выход вычитателя 11 подключен к частотному входу двоичного умножителя 12. Каждый i-ый () дополнительный регистр 14 (где а-количество частот, формируемых генератором 4) соединен выходами первой и второй групп разрядов соответственно со входами первой и второй групп разрядов (i+l)-ro дополнительного регистра 14, а управляющим входом - с (1+1)-ыгл управляющим выходом 9 блока 1 управления, причем (п-1)-ый дополнительный регистр 14 подключен выходами первой группы разрядов к информационным входам двоичного умножителя 12, выходами второй группы разрядов - к информационным входам генератора 13, а упраляющим входом - к п-ому управляющему выходу 9 блока 1 управления.

Блок 1 соединен третьим импульсным входом 15 с выходом формирователя 16 импульсов, с первым управляющим входом двоичного умножителя 12

и со входом управления установкой кода генератора 13, а группой из 12-ти информационных входов 17 с первой группой выходов генератора 8. Генератор 8 подключен второй группой выходов ко входам второй группы разрядов регистра 10, выходы первой и второй группы разрядов которого соединены соответственно со входами первой и второй групп разрядов первого дополнительного регистра 14.

0 Генератор 13 подключен входами опорных частот к выходам генератора 4. Шина ввода умножаемой частоты соединена с сигнальным входом узла 18 формирования задержки, подключенного

5 тактовым входом к соответствующему выходу генератора 4, а выходом - ко второму управляющему входу двоичного умножителя 12, соединенного управляющим выходом со входом формировате0ля 16 импульсов.

Двоичный умножитель 12 содержит группу элементов И 19, элемент ИЛИ 20, счетчик 21 и регистр 22, входы разрядов которого являются информационными входами умножителя 12, уп5равляющий вход - первым управляющим входом умножителя 12, а выходы разрядов подключены к первым входам элементов И 19. Вторые входы элементов И 19 соединены с выходами разDрядов счетчика 21, счетный вход и выход обнуления которого являются соответственно частотным входом и вторым управляющим входом умножителя 12, а выход переполнения - управ5ляющим выходом умножителя 12. Выходы элементов И 19 подключены ко входам элемента ИЛИ 20, выход которого является частотным выходом умножителя 12, Блок 1 управления (фиг.2)

0 :содержит группу из п дешифраторов 23, п групп по п элементов И 24, группу из (п+1)-ых элементов ИЛИ 25, первую группу из п последовательно соединенных формирователей 26, вторую группу из п последовательно

5 соединенных .формирователей 27 и ключ 28, выход которого является счетным выходом 5 блока 1, первый вход соединен со входом первого формирователя 26-1 первой группы формирователей, а

0 первый и второй входы ключа являются соответственно первым и вторым импульснь1ми входами. 2 и 3 блока 1.

Каждый i-ый i() элемент li 24 4саждой j ой () группы элементов

5 И подключен первым входом к выходу (/i-k/+l)-ro формирователя первой группы формирователей 26 (где/i-k/модуль разности), а вторым входом к выходу j-ro дешифратора 23, сое0диненного входами с информационными входами 17 блока 1. Каждый j-ый вход первого элемента ИЛИ 25-1 подключен к выходу (n-j+l)-ro элемента И j-ой группы элементов И 24, а выходы каждого К.-го (24kin) элемента ИЛИ 25.

ИЛИ 25 на выходы 9 блока 1. Первый импульс переписывает содержимое счетчиков измерителя б периода и счетчик управляемого генератора 8 частоты в регистр 10. Второй импульс содержимое регистра 10 переписывает в первы из дополнительна регистров 14 и так далее. Последним импульсом содержимое из (п-1)-го регистра 14 переписывается в п-ыП регистр 14. Содержимое п-го регистра 14 сигналом с выхо да формирователя 16, появляющегося в момент окончания развертки кода предыдущего периода, переписывается в регистры двоичного умножителя 12 и дополнительного управляемого генерат ра 4.

В общем случае логика работы блока 1 управления такова, что содержимое счетчиков измерителя 6 периода и управляемого генератора 8 частоты сигналами выходов 9 блока 1 (распределение которых определяется номером сработавшег-о дешифратора 23 блока 1 управления) заносится в регистр с номером/ равным номеру поддиапазона. Таким образом, предлагаемый умножитель частоты обеспечивает полную развертку, каждого кода текущего периода в случаях резких изменений частоты на входе умножителя, что и исклчает динамическую погрешность.

Для синхронизации работы умножителя в него, введен узел 18 формировани задержки, состоящий,в общем случае, из пересчетного элемента, формирователя и ключа, i-bin импульс входной частоты f)( открывает ключ, через который на вход пересчетного элемента с выхода генератора 4 сетки частот поступают импульсы тактовой частоты .fg. Коэффициент пересчета k пересчетного элемента и период TQ тактовой частоты выбираются из условия

kTo TX .o

Таким . образом, через время, равное г на выходе пересчетного элемента -формируется сигнал, поступающий на вход формирователя. С выхода последнего импульс поступает на вход обнуления счетчика 21 двоичного умножителя 12 и на сброс ключа узла 18. Ключ закрывается, но первым же после этого импульсом частоты fx он открывается вновь.

При синхронной работе умножителя импульс, формируемый узлом 18 формирования задержки, совпадает с моментом обнуления счетчика 21 двоичного умножителя 12 и подтверждает состояние счетчика. При нарушении синхрони зации работы умножителя, что может

произойти за счет сбоя одного из регистров 10 и 14, импульс с выхода

узла 18 формирования задержки вводит умножитель в синхронизм, что обеспечивает надежную работу умножителя.

Таким образом, предлагаемый умножитель частоты позволяет по сравнению с известным за счет введения новых узлов и связей увеличить динамическую точность умножения и расширить динамический диапазон изменения входного сигнала.

Формула изобретения

каждого к -го (24k«n) ИЛИ соединены с выходами {К-1)-ых элементов И всех групп элементов И и с выходом (n-k+2)-ro формирователя второй группы формирователей, приче вход первого формирователя второй группы формирователей является третим импульсным входом блока управления, выход первого элемента ИЛИ является рыходом обнуления блока управления, а выход каждого к -го (2ik4n) элемента ИЛИ - (к-1)-ым управляющим выходом блока управления.

3, Умножитель по п.1, о т л и чающийс тем, что двоичный умножитель содержит группу элементов И, элемент ИЛИ, счетчик и регис входы разрядов которого являются информационными входами двоичного умножителя, управляющий вход - первым управляющим входом двоичного умножителя, а выходы разрядов подключены к первым входам элементов И соединенных вторыми входами с выходами разрядов счетчика, счетный вхо и вход обнуления которого являются соответственно частотным входом и вторым управляющим входом двоичного умножителя, а выход переполнения управляющим выходом двоичного умножителя, причем выходы элементов И подключены ко входам элемента ИЛИ, выход которого является частотным выходом двоичного умножителя.

Источники информации, принятые во внимание при экспертизе

свидетельство СССР Об F 7/52, 1969. свидетельство СССР 06 F 7/52, 1970. свидетельство СССР 03 К 5/00, 1969

Фи1.2

Авторы

Даты

1981-09-30—Публикация

1980-01-08—Подача