1

ИзОбретбнке относится к вычислительной технике.

Известны мяогофувщионалБные логические МО-дули с кодовой настройкой на реализацию произвольной логичеокой функции входных переменных, выполненные на магнитных токовых переключателях и содержащие узел формирования полного набора минитермю-в входных переменных, узел задания мииитермов реализуемой функции, узел анализа минитермов входных перемендых и формирова/ния значения реализуемой фута-кции.

Однако для этих модулей характерно сложное управление их логи1кой (большое количество ШИ1Н ввода кода логичеокой 01перации) и иизкое быстродействие.

Целью изобретения является создание многофункционального логического имодуля с высоким быстродействибМ и лростым управлением.

Для этого .распределяющие обмотки узла формирования полного набора Минитермов входных переадеиных включены последовательно с соответствующими распределяющими 0|б1мотками прямых и инверсных значений мийитермов реализуемой функции узла анализа 1минитерл1а -входных переменных и формирования значения реализуемой функции, раюположепными на запоминающих сердечниках узла задания мииитермов реализуемой

функции, а диоды, Связанные с распределяющими обмотками арямых и инвер-сных значений .минитермов реализуемой функции объединены соответственно в две схемы «ИЛИ.

Выход первой из «их подключен .к единичной выходной клемме модуля, а выход второй - к нулевой выходной клемчме модуля.

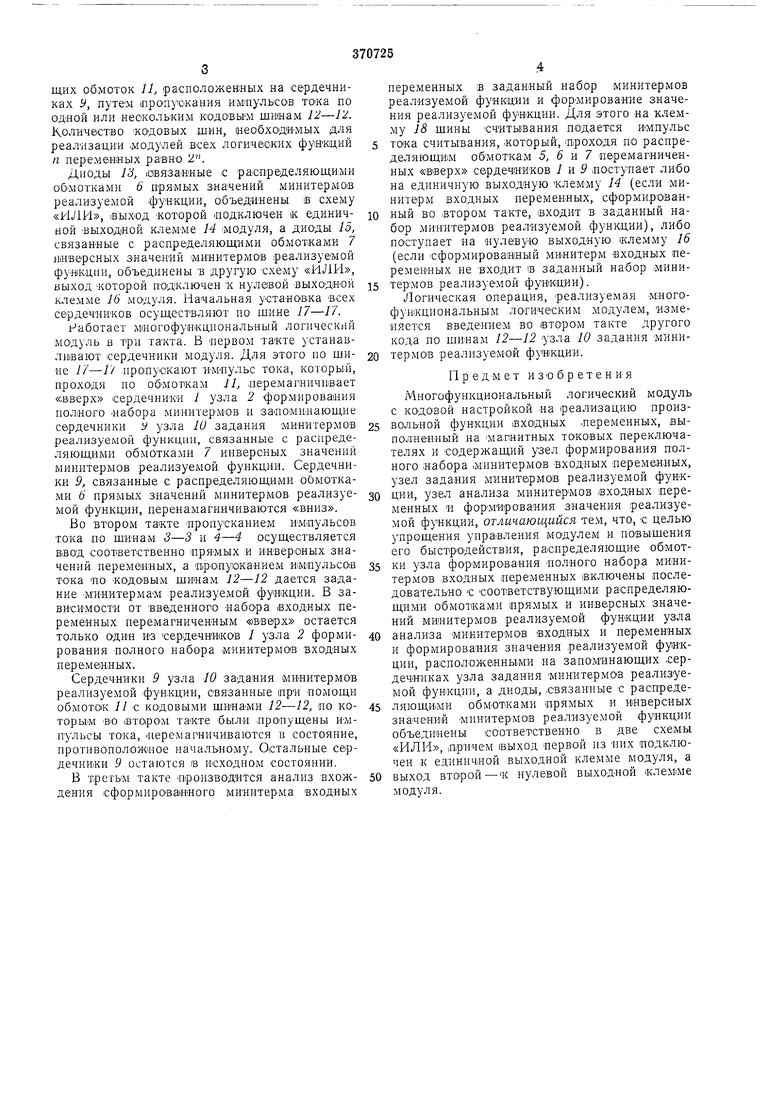

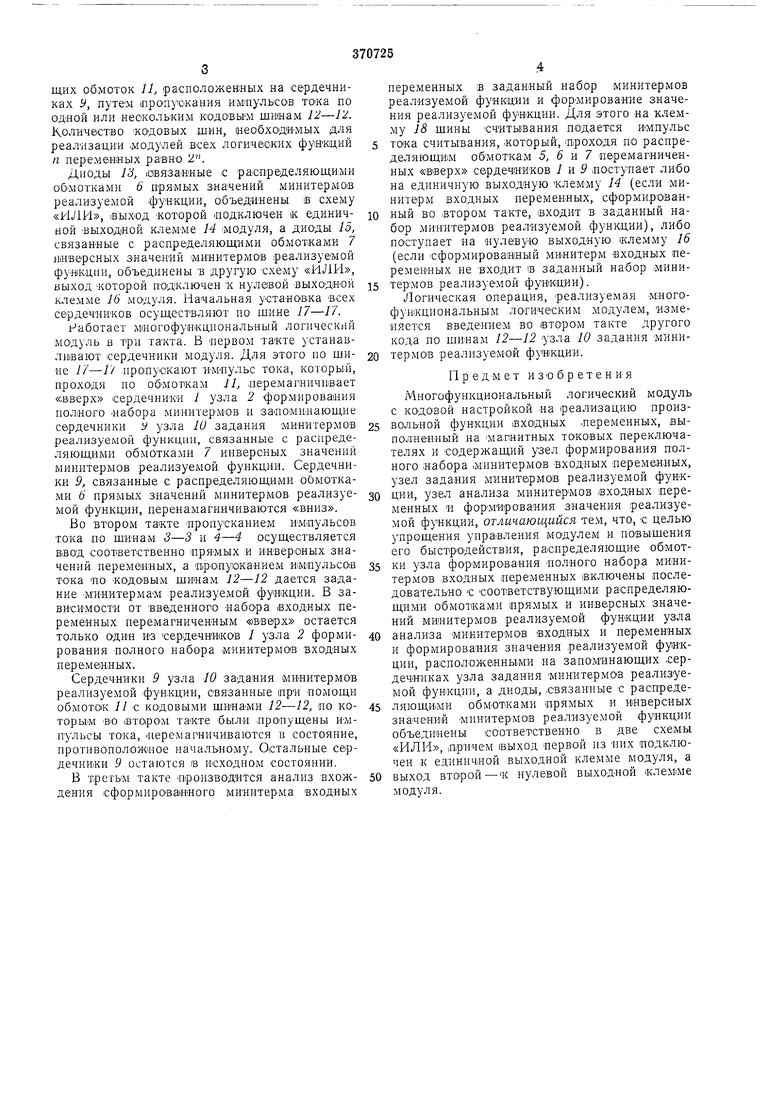

Принципиальная схема многофункцио1вального логическОГО модуля, предназначе пиого,

например, для реализации произвольных логических функций трех переменных, приведена на чертеже.

Структура модуля такова, что прямые и инверсные значения входных переменных

записываются «а сердеч1ники / узла 2 формирования полного набора минитермов входных переменных путем пропускания импульсов тока по соответствующим входным щинам 3 и 4. Распределяющие обмотки 5 узла 2 формирования полного набора минитермов входных переменных включены последовательно с соответствующими распределяющими об:мотками 6 и 7 прямых и инверсных значений минитермов реализуемой функции узла 8 анализа

минитерма входных переменных и формирования з начения реализуемой функции, расположенными на запоминающих сердечниках 9 узла W задания минитермов реализуемой функции. Все мипитермы реализуемой функции получают задание при помощи у правляющих обмоток 11, расположенных на сердечниках У, путем тропуокания ИМпульсОВ по одной или нескольким кодовым шииам 12-Г2. Количество -кодовых шин, необходимых для реализации модулей всех логических функций п переме-ввых равно 2.

Диоды 13, ювязаиные с распределяющими обмотками 6 прямых зиачений минитерхмов реализуемой функции, объединены в схему «ИЛИ, 1выход которой подключен к единичной ВЫХОДНОЙ клемме 14 модуля, а диоды 15, связанные с распределяющими обмотками 7 ииверсных эначений мниитермов реализуемой функции, объединены ъ другую схему «ИЛИ, выход -которой подключен к нулевой выходной клемме 16 модуля. Начальная установка всех сердечников осуществляют по шине 17-П.

i-аботает М(ногофу1нкциональный логический модуль в три такта. В первом такте устанавливают сердечники модуля. Для этого по шине Г/-Ii .пропускают импульс тока, который, проходя по обМоткам 11, перемагничпвает «вверх сердечники 1 узла 2 формирования полного набора минитер-мов н запоминающие сердечники У узла 10 задания минитермов реализуемой функции, связанные с распределяющими обмотками 7 инверсных значений минитермов реализуемой функции. Сердечники 9, связанные с распределяющими обмотками 6 прямых значений минитермов реализуемой функции, перенамагничиваются «вниз.

Во втором такте пропусканием импульсов тока по шинам 3-3 и 4-4 осуществляется ввод соогветственно прямых и инверОных значений переменных, а пр01нуоканием импульсов тока по кодовым шинам 12-12 дается задание МИНитермаМ реализуемой функции. В зависимости от введенного набора входных переменных перемагниченным «вверх остается только адин из сердечников 1 узла 2 формирования полного набора минитермав входных переменных.

Сердечники 9 узла 10 задания минитермов реализуемой функции, связанные при помощи обмоток и С кодовыми шинами 12-12, по которым во (Второ м такте были пропущены ИМпульсы тока, перемагничиваются в состояние, противоположное начальному. Остальные сердечники 9 остаются в исходном состоянии.

В третьм такте производится анализ вхождения |Сформированного миннтерма входных

переменных IB заданный набор миннтермов реализуемой функции и формирование значения реализуемой функции. Для этого на клемму 18 шины считывания подается импульс тока считывания, который, проходя по распределяющем обМОткам 5, б и 7 перемагниченных «вверх сердечников ./ и 5 поступает либо на единичную выходную клемму 14 (если минитерм входных переменных, сформированный во втором такте, входит в заданный набор минитермов реализуемой функции), лНбо поступает на нулевую выходную клемму 16 (если сформированный минитерм входных переменных не входит в заданный набор минитермов реализуемой функции).

Логическая операция, реализуемая многофункциональным логическим модулем, изменяется введением во втором такте другого кода по шинам 12-12 узла 10 задания минитермов реализуемой функции.

Предмет изобретения

Многофункциональный логический модуль с кодовой настройкой на реализацию произвольной функции входных переменных, выполненный на ма.гнитных токовых переключателях и содержащий узел формирования полного набора (Минитермов входных переменных, узел задания минитермов реализуемой функции, узел анализа минитермов входных переменных и формирования значения реализуемой функции, отличающийся тем, что, с целью упрощения управления модулем и повышения его быстродействия, распределяющие обмотки узла формирования нолного набора минитермов входных переменных включены последовательно с соответствующими распределяющими обмотками прямых и инверсных значений минитермов реализуемой функции узла

анализа минитермов входных и переменных и формирования значения реализуемой функции, расположенными на запоминающих сердечниках узла задания минитермов реализуемой функции, а диоды, связанные с распределяющи1ми обмотками прямых и инверсных значений мннитермов реализуемой функции объединены соответственно в две схемы «ИЛР, причем выход первой из них подключен к единичной выходной клемме модуля, а

выхОД второй-чс нулевой выходной клем1ме модуля.

1..„.

.J

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИВЕРСАЛЬНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ С КОДОВОЙ ПЕРЕСТРОЙКОЙ ЛОГИКИ | 1972 |

|

SU436353A1 |

| Многофункциональный модуль со встроенным контролем | 1972 |

|

SU438121A1 |

| УНИВЕРСАЛЬНЫЙ ДВУХВХОДОВЫЙ ПОРОГОВЫЙ МОДУЛЬ | 1972 |

|

SU350174A1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ | 1972 |

|

SU332575A1 |

| Многофункциональный пороговый модуль с кодовой перестройкой логики | 1972 |

|

SU474108A1 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1971 |

|

SU320057A1 |

| Многофункциональный пороговый логический элемент | 1973 |

|

SU608265A1 |

| Многофункциональный пороговый модуль с кодовой перестройкой логики | 1974 |

|

SU493031A1 |

| УНИВЕРСАЛЬНАЯ ЯЧЕЙКА ВЫЧИСЛИТЕЛЬНОЙ СРЕДЬ! СО СКВОЗНЫМ ПЕРЕНОСОМ НА МАГНИТНЫХ ТОКОВЫХ ПЕРЕКЛЮЧАТЕЛЯХ | 1972 |

|

SU436347A1 |

| ДВОИЧНЫЙ РЕГИСТР НА МАГНИТНЫХ ПОРОГОВЫХ | 1973 |

|

SU369632A1 |

Авторы

Даты

1973-01-01—Публикация