1

Изобретение относится к области вычислительной техники.

Известны универсальные вычислительные модули с кодовой перестройкой логики, выполненные на магнитных токовых переключателях и содержащие узлы ввода кода реализуемой функции, ввода кода входных переменных, узел формирования значения реализуемой функции, узел формирования сигнала обратной связи и узел формирования сигнала сквозного переноса, выполненные на сердечниках с ППГ.

Общим недостатком известных модулей является структурная сложность и ограниченные логические возможности.

С целью упрощения модуля и расширения его логических возможностей на сердечниках узла ввода кода входных переменных расположены управляющие обмотки этого узла, узла ввода кода реализуемой функции и распределяющие обмотки узла формирования значения реализуемой функции, причем распределяющие обмотки узла формирования сигнала сквозного переноса соединены последовательно с группой управляющих обмоток узла ввода кода реализуемой функции, а управляющие обмотки узла формирования сигнала сквозного переноса соединены с управляющими обмотками узла ввода кода входных переменных и с распределяющими обмотками узла формирования сигнала обратной связи, управляющие обмотки которого последовательно соединены с распределяющими обмотками узла формирования значения реализуемой функции.

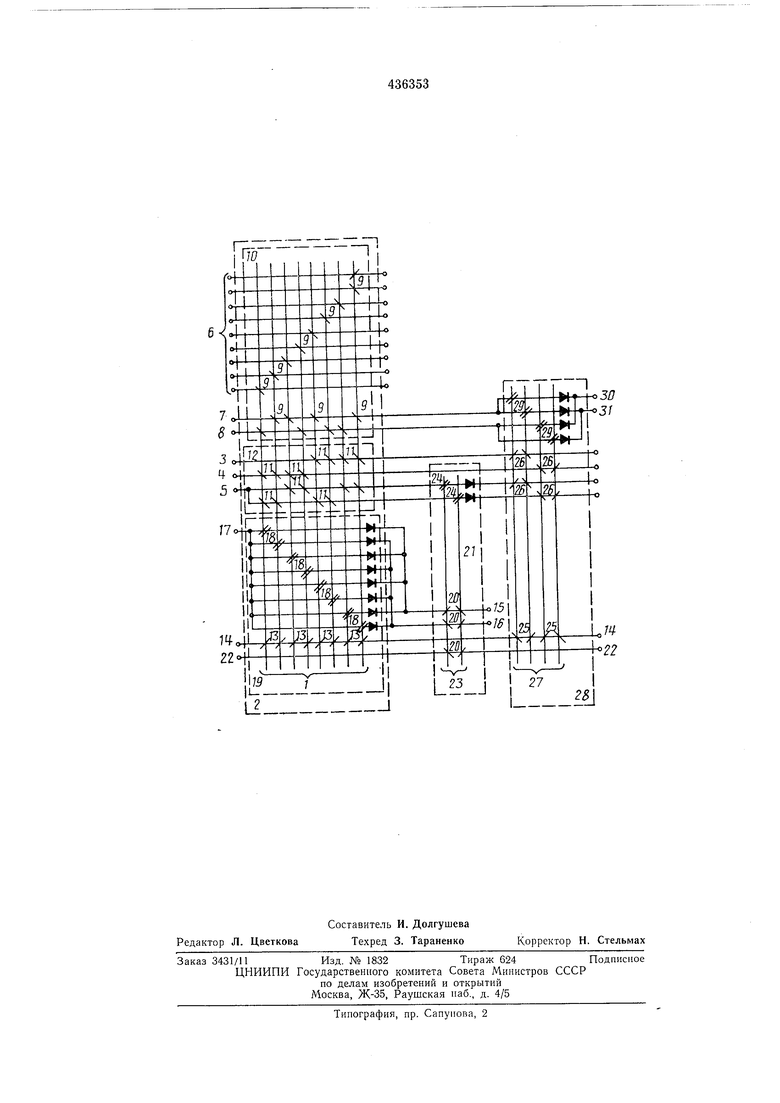

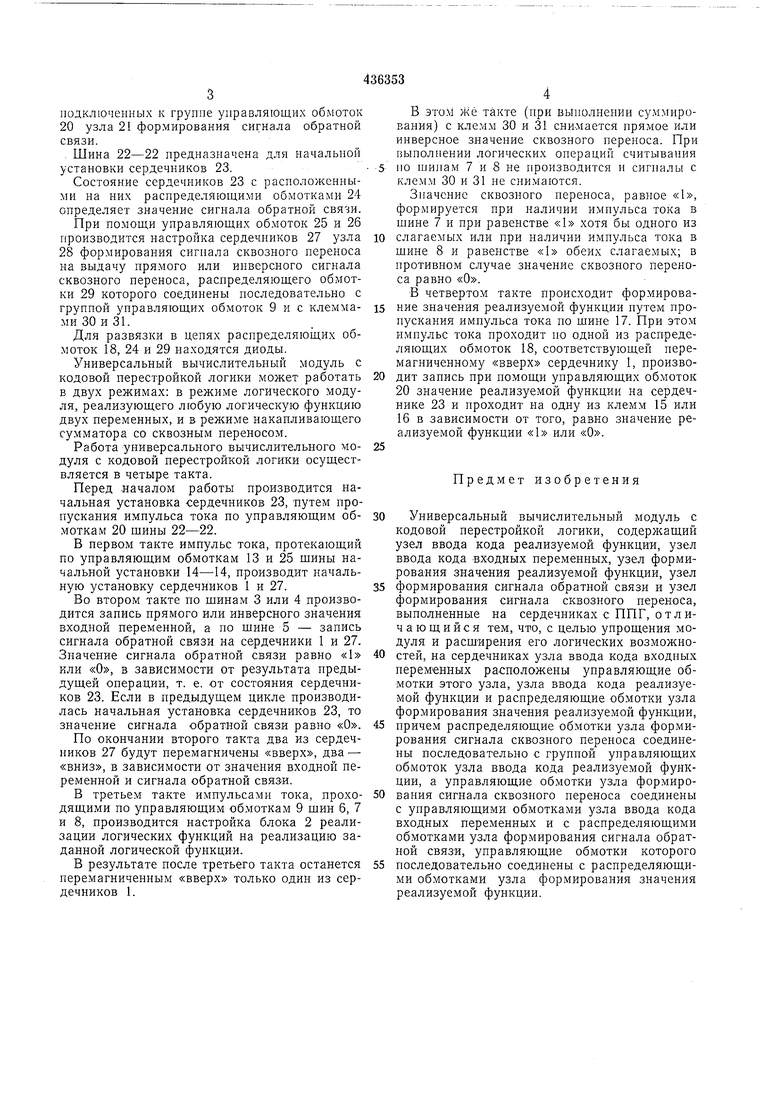

Иринципиальная схема универсального вычислительного модуля с кодовой перестройкой логики приведена на чертеже; вертикальными линиями обозначены сердечники с ППГ, горизонтальными - щины, а наклонными - обмотки.

Структура модуля такова, что прямые и инверсные значения входных переменных записываются на сердечники 1 блока 2 реализа5 ции логических функций при поступлении сигналов на входные щины 3, 4 и 5.

Вид реализуемой функции задается кодом, заносимым по шинам 6, 7 и 8.

Суммарные магнитные потоки управляю0 щих обмоток 9 узла 10 ввода кода реализуемой функции, управляющих обмоток 11 12 ввода кода входных переменных, управляющих обмоток 13 щины 14-14 начальной установки определяют состояние сердечников 1 5 при реализации заданной функции.

Прямое и инверсное значения реализуемой

функции снимаются соответственно с клемм 15

и 16 при пропускании импульсов тока по щине 17, распределяющим обмоткам 18 узла 19

0 формирования значения реализуемой функции.

подключенных к группе управляющих обмоток 20 узла 21 формирования сигнала обратной связи.

, Шина 22-22 предназначена для начальной установки сердечников 23.

Состояние сердечников 23 с расположенными на них распределяющими обмотками 24 определяет значение сигнала обратной связи.

При помош;и управляющих обмоток 25 и 26 производится настройка сердечников 27 узла 28 формирования сигнала сквозного переноса на выдачу прямого или инверсного сигнала сквозного переноса, распределяющего обмотки 29 которого соединены последовательно с группой управляющих обмоток 9 и с клеммами 30 и 31.

Для развязки в цепях распределяющих обмоток 18, 24 и 29 находятся диоды.

Универсальный вычислительный модуль с кодовой перестройкой логики может работать в двух режимах: в режиме логического модуля, реализующего любую логическую функцию двух переменных, и в режиме накапливающего сумматора со сквозным переносом.

Работа универсального вычислительного модуля с кодовой перестройкой логики осуществляется в четыре такта.

Перед началом работы производится начальная установка сердечников 23, -путем пропускания импульса тока по управляющим обмоткам 20 шины 22-22.

В первом такте импульс тока, протекающий по управляющим обмоткам 13 и 25 шины начальной установки , производит начальную установку сердечников 1 и 27.

Во втором такте по шинам 3 или 4 производится запись прямого или инверсного значения входной переменной, а по шине 5 - запись сигнала обратной связи на сердечники 1 и 27. Значение сигнала обратной связи равно «1 Р1ЛИ «О, в зависимости от результата предыдущей операции, т. е. от состояния сердечников 23. Если в предыдущем цикле производилась начальная установка сердечников 23, то значение сигнала обратной связи равно «О.

По окончании второго такта два из сердечников 27 будут перемагничены «вверх, два - «вниз, в зависимости от значения входной переменной и сигнала обратной связи.

В третьем такте импульсами тока, .проходящими по управляющим обмоткам 9 шин 6, 7 и 8, производится настройка блока 2 реализации логических функций на реализацию заданной логической функции.

В результате после третьего такта останется перемагниченным «вверх только один из сердечников 1.

В этом же такте (при выполнении суммирования) с клемм 30 и 31 снимается прямое или инверсное значение сквозного переноса. При выполнении логических операций считывания по шипам 7 и 8 не производится и сигналы с клемм 30 и 31 не снимаются.

Значение сквозного переноса, равное «1, формируется при наличии импульса тока в шине 7 и при равенстве «I хотя бы одного из

слагаемых или при наличии импульса тока в шине 8 и равенстве «1 обеих слагаемых; в противном случае значение сквозного переноса равно «О. В четвертом такте происходит формирование значения реализуемой функции путем пропускания импульса тока по шине 17. При этом импульс тока проходит по одной из распределяющих обмоток 18, соответствующей перемагниченному «вверх сердечнику I, производит запись при помощи управляющих обмоток 20 значение реализуемой функции на сердечнике 23 и проходит на одну из клемм 15 или 16 в зависимости от того, равно значение реализуемой функции «Ь или «О.

Предмет изобретения

Универсальный вычислительный модуль с кодовой перестройкой логики, содержащий узел ввода кода реализуемой функции, узел ввода кода входных переменных, узел формирования значения реализуемой функции, узел

формирования сигнала обратной связи и узел формирования сигнала сквозного переноса, выполненные на сердечниках с ППГ, отличающийся тем, что, с целью упрощения модуля и расширения его логических возможностей, на сердечниках узла ввода кода входных переменных расположены управляющие обмотки этого узла, узла ввода кода реализуемой функции и распределяющие обмотки узла формирования значения реализуемой функции,

причем распределяющие обмотки узла формирования сигнала сквозного переноса соединены последовательно с группой управляющих обмоток узла ввода кода реализуемой функции, а управляющие обмотки узла формирования сигнала сквозного переноса соединены с управляющими обмотками узла ввода кода входных переменных и с распределяющими обмотками узла формирования сигнала обратной связи, управляющие обмотки которого

последовательно соединены с распределяющими обмотками узла формирования значения реализуемой функции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный модуль со встроенным контролем | 1972 |

|

SU438121A1 |

| УНИВЕРСАЛЬНАЯ ЯЧЕЙКА ВЫЧИСЛИТЕЛЬНОЙ СРЕДЬ! СО СКВОЗНЫМ ПЕРЕНОСОМ НА МАГНИТНЫХ ТОКОВЫХ ПЕРЕКЛЮЧАТЕЛЯХ | 1972 |

|

SU436347A1 |

| УНИВЕРСАЛЬНЫЙ ДВУХВХОДОВЫЙ ПОРОГОВЫЙ МОДУЛЬ | 1972 |

|

SU350174A1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 1973 |

|

SU370725A1 |

| Многофункциональный пороговый модуль с кодовой перестройкой логики | 1972 |

|

SU474108A1 |

| Многофункциональный пороговый модуль с кодовой перестройкой логики | 1974 |

|

SU493031A1 |

| Многофункциональный пороговый логический элемент | 1973 |

|

SU608265A1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ | 1972 |

|

SU332575A1 |

| ЯЧЕЙКА ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1973 |

|

SU407425A1 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1971 |

|

SU320057A1 |

Даты

1974-07-15—Публикация

1972-05-24—Подача