1

Изобретение относится к электросвязи, а именно к передаче дискретных сигналов по каналам связи.

Известны корректоры сигналов дискретной информации, содержащие дискретный модулятор, регистр сдвига, соединенный через регуляторы с сумматором, дешифратор управления, распределитель, регенератор, генератор тактовых импульсов и подстроечный генератор.

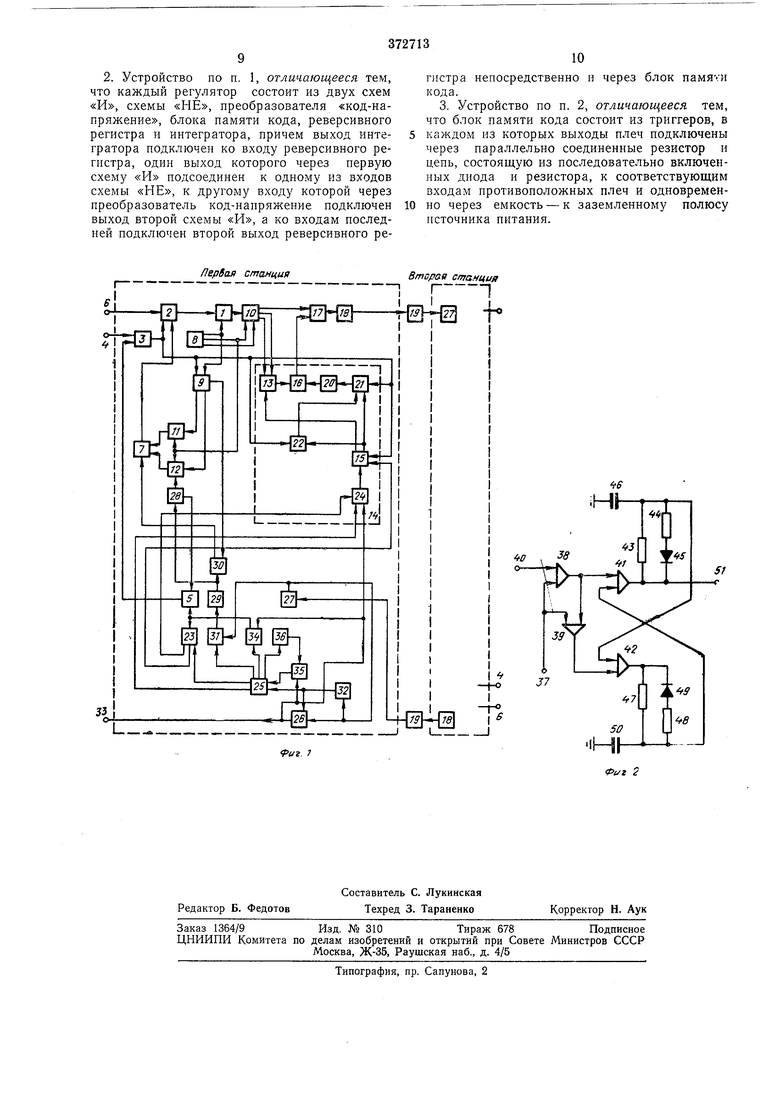

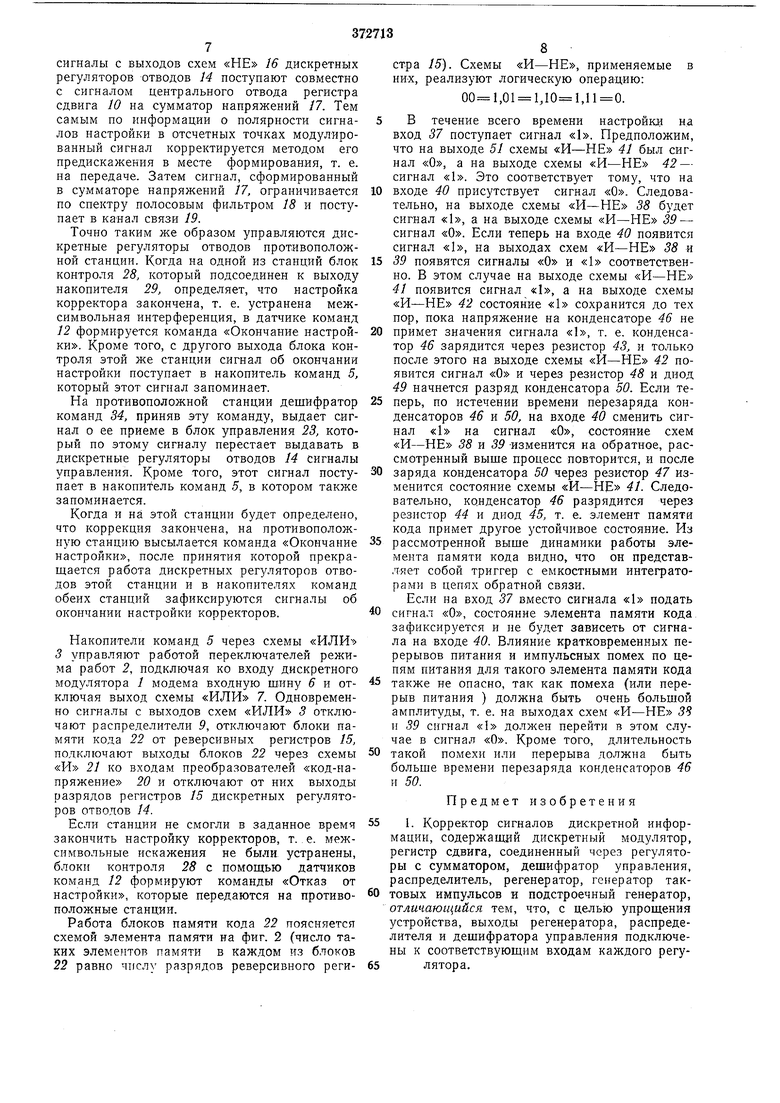

Цель изобретения - упрощение устройства. Достигается она тем, что в предлагаемом корректоре выходы регенератора, распределителя и дешифратора управления подключены к соответствующим входам каждого регулятора. Каждый регулятор состоит из двух схем «И, схемы «НЕ, преобразователя коднапряжение, блока памяти кода, реверсивного регистра и интегратора, причем выход интегратора подключен ко входу реверсивного регистра, один выход которого через первую схему «И подсоединен к одному из входов схемы «НЕ, к другому входу которой через преобразователь код-напряжение подключен выход второй схемы «И, а ко входам последней подключен второй выход реверсивного регистра непосредственно и через блок памяти кода. Блок памяти кода состоит из триггеров, в каждом из которых выходы плеч подключены через параллельно соединенные регистр и цепь, состоящую из последовательно включенных диода и резистора, к соответствующим входам противоположных плеч и одновременно через емкость - к заземленному полюсу источника питания.

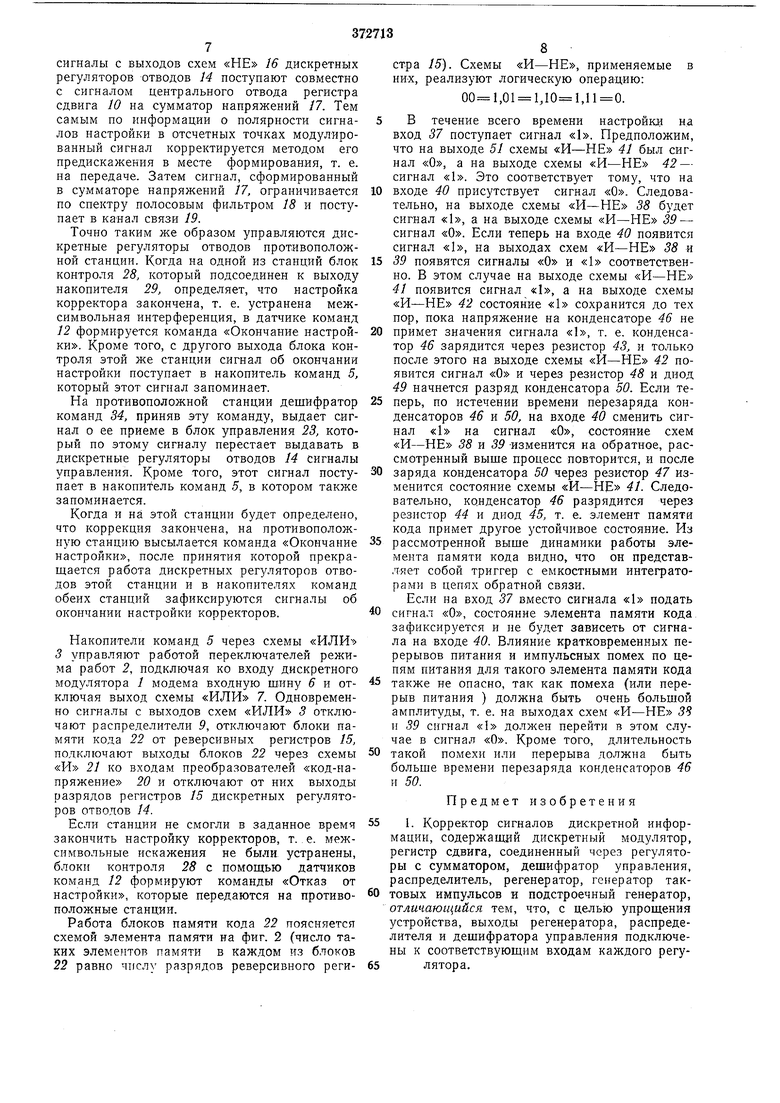

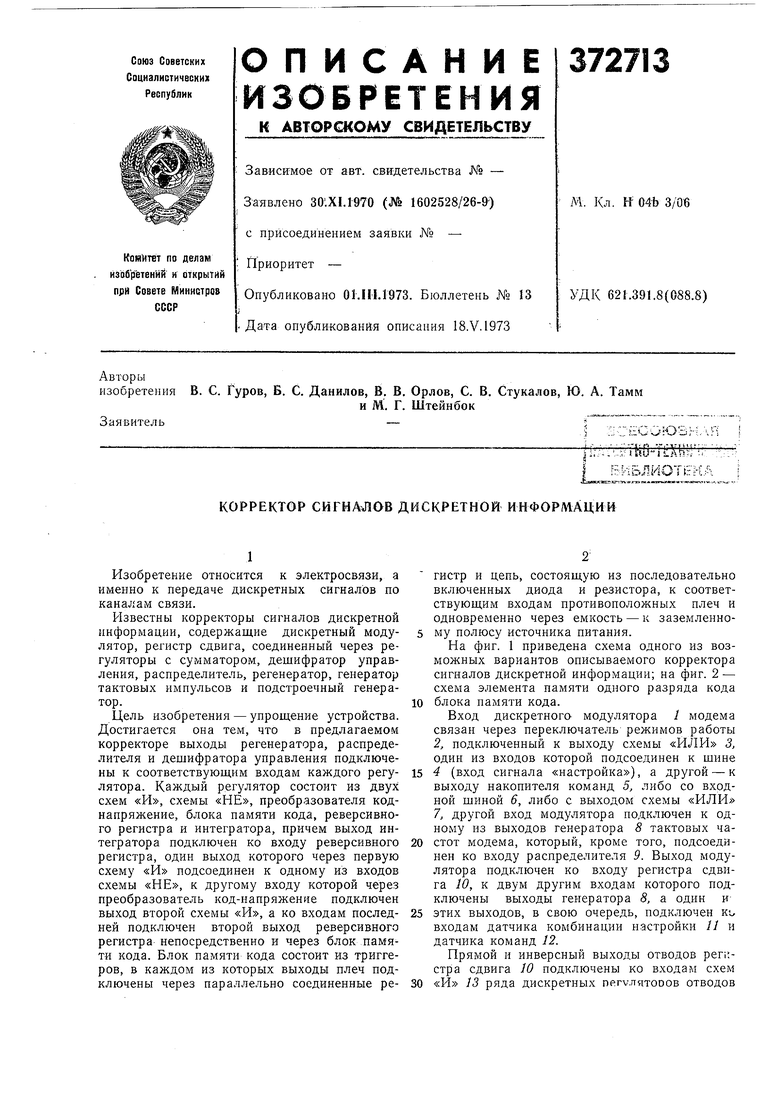

На фиг. 1 приведена схема одного из возможных вариантов описываемого корректора сигналов дискретной информации; на фиг. 2 - схема элемента памяти одного разряда кода

блока памяти кода.

Вход дискретнога модулятора 1 модема связан через переключатель режимов работы 2, подключенный к выходу схемы «ИЛИ 3, один из входов которой подсоединен к шине

4 (вход сигнала «настройка), а другой - к выходу накопителя команд 5, либо со входной шиной 6, либо с выходом схемы «ИЛИ 7, другой вход модулятора подключен к одному из выходов генератора 8 тактовых частот модема, который, кроме того, подсоединен ко входу распределителя 9. Выход модулятора подключен ко входу регистра сдвига 10, к двум другим входам которого подключены выходы генератора 8, а один и

этих выходов, в свою очередь, подключен квходам датчика комбинации настройки 11 и датчика команд J2.

Прямой и инверсный выходы отводов реп:стра сдвига 10 подключены ко входам схем

«И 13 ряда дискретных пегулятооов отводов

14 (для упрощения чертежа на фиг. 1 изображен один регулятор).

Третий вход схемы «И 13 соединен с выходом реверсивного регистра 15, а выход схемы «И 13 подключен к одному из входов схемы «НЕ 16, выход которой соединеи со входом сумматора напряжений 17 (пе изображенные на чертеже остальные дискретные регуляторы отводов 14 также подключены к сумматору напряжений), а дополнительный вход данного сумматора, выход которого через полосовой фильтр модема 18 подключен к каналу связи 19, соединен с дополнительным выходом регистра сдвига 10. Другой вход схемы «НЕ 16 связан с выходом преобразователя «код-напряжение 20, вход которого соединен с выходом ряда схем «И 21 (для простоты на чертеже показана только одна из них), один из входов которых в свою очередь соединен с выходом блока памяти кода 22, другой - с выходом реверсивного регистра 15 и со входом блока памяти кода. Третий вход схемы «И 21 соединен с выходом схемы «ИЛИ 3, и входами распределителя 9, блока памяти кода 22, реверсивного регистра 15. Второй вход реверсивного регистра подключен к выходу блока управления 23, третий - к выходу дополнительного реверсивного регистра 24, один вход которого подсоединен к блоку управления 23, другой - к выходу распределителя 25, третий--к выходу регенератора 26, который, в свою очередь, через дискретный демодулятор 27 подключен к каналу связи 19.

Распределитель 9 двумя выходами подсоединен, соответственно, ко входу датчика комбинации настройки 11 и входу датчика команд 12, другой вход датчика 12 подключен через блок контроля 28 к выходу накопителя 29, а другой выход блока 28 подсоединен ко входу накопителя команд 5.

Выходы датчиков 11 и 12 соединены, соответственно, с двумя входами схемы «ИЛИ 7, третий вход которой через схему «И 30 (на самом деле их несколько, но для простоты чертел а показана только одна) подключен к накопителю 29, Второй вход схемы «И 30 подключен к выходу распределителя 9. В свою очередь, вход накопителя 29 подсоединен через схему «И 81 (их тоже несколько) к выходу распределителя 25, а второй вход схемы «И 31 - к выходу дискретного демодулятора 27 и ко входу подстраиваемого генератора 32.

Выход регенератора 26 подключен одновременно к выходной шине 33, ко входу дешифратора команд 34 и ко входу компараторй 35, выход которого соединен со входом распределителя 25, а второй вход распределителя 25 - с выходом подстраиваемого генератора тактовых частот 32 и входом генератора 26.

Второй вход компаратора 35 соединен через дешифратор комбинации настройки 36 с однпм из выходов распределителя 25.

Второй выход распределителя 25 подключен ко входу блока управления 23 непосредственно, а третий - через дешифратор команд 34 ко второму входу блока управления 23 и одновременно ко входу накопителя команд 5. В приведенной на фиг. 2 схеме возможной реализации элемента памяти блока памяти кода 22 (при исиользовании в качестве схем «И-НЕ интегральных элементов) вход 37,

на который поступает сигнал с выхода схемы «ИЛИ 3, соединен со входами схем «И-НЕ 38 и 39, а вход 40, на который поступает сигнал с выхода одного из разрядов реверсивного регистра 15, соединен со входом схемы

«PI-НЕ 38, выход которой в свою очередь соединен со входом схемы «И-НЕ 41 непосредственно и входом схемы «И-НЕ 42 - через схему «И-НЕ 39.

Выход схемы «И-НЕ 41 через параллельио включенные резистор 43 и резистор 44, последовательно с которым включен диод 45, подсоединен к конденсатору 46 и входу схемы «И-НЕ 42. Выход схемы «И-НЕ 42, в свою очередь, через параллельно включенные резистор 47 и резистор 48, последовательно с которым включен диод 49, подсоединен к конденсатору 50 и входу схемы «И-НЕ 41. Кроме того, выход 51, подключенный к выходу схемы «И-НЕ 41, соединен со входом одной из схем «И 21 дискретного регулятора отвода 14.

Сигнал, поступивший на шину 4, через схему «ИЛИ 3 воздействует на переключатель режима работ 2, который отключает от

входа дискретного модулятора модема / входную шину 6 и подключает к нему выход схемы «ИЛИ 7. Одновременно тот же сигнал, появившийся на выходе схемы «ИЛИ 3, поступает на вход реверсивного регистра 15

и входы схем «И 21 дискретных регуляторов отводов 14, обеспечивая тем самым отключение схем «И 21 от блока памяти кода 22 и подключение их непосредственно к выходам регистра 15. Распределитель 9, на другой

вход которого поступает гребенка тактовых импульсов от генератора 8 тактовых частот модема, управляет работой датчика комбинации настройки 11 и датчика команд 12, на вторые входы которых поступает от генератора 8 тактовых частот модема, сдвинутая по отношению к упомянутой выше гребенке тактовых импульсов. Кроме того, к третьему входу датчика команд 12 подключен блок контроля 28. Эти два узла вырабатывают в

процессе настройки следующие команды:

а)начало настройки;

б)окончание настройки;

в)отказ от настройки.

Сигналы с выходов датчика комбинации настройки //, датчика команд 12 и схем «И 30, работой которых управляет распределитель 9, поступают на соответствующие входы схемы «ИЛИ 7. Таким образом, на выходе

схемы «ИЛИ 7 в течение всего времени настройки формируются блоки информации следующего вида:

Информация о полярности

Команда

сигнала настройки в отсчетных точках

Комбинацию настройки выбирают определенной структуры, чтобы в ней содержалось достаточно информации для работы подстраиваемого генератора 32 тактовых частот модема противоположной станции и можно было оценить межсимвольные искажения, вносимые каналом связи 19. Кроме того, передается команда «Начало настройки. Блоки информации, пройдя через переключатель 2 и дискретный модулятор /, регистр сдвига 10, сумматор напряжений 17, полосовой фильтр 18 модема первой станции, поступают в канал связи 19. На другой станции сигнал, пришедший из канала связи 19, демодулируется в дискретном демодуляторе 27, регенерируется в регенераторе 26 с цомошью гребенки тактовых импульсов, вырабатываемой подстраиваемым генератором 32 (подстройка его ведется по сигналу из демодулятора 27), и выдается одновременно на выходную шину 33, на вход компаратора 35, на вход дешифратора команд 34 и на вход дополнительного реверсивного регистра 24 ряда дискретных регуляторов отводов 14. Распределитель 25, на один вход которого поступает от подстраиваемого генератора 32 гребенка тактовых импульсов совместно с дешифратором комбинации настройки 36 и компаратором 35 выделяет из принятой информации комбинацию настройки, и в случае принятия ее дешифратор команд 34 выявляет переданную команду «Начало настройки и управляет работой накопителя команд 5 и блока управления 23.

Если комбинация настройки и команда «Начало настройки приняты несколько раз подряд, накопитель команд 5 через схему «ИЛИ 3 переключает вторую станцию в режим настройки. На второй станции при этом происходят такие же переключения, как и на первой.

Таким образом, на второй станции формируются такие же, как и на первой, блоки информации, в которых информация о полярности сигнала настройки в отсчетных точках вырабатывается в результате оценки сигнала, имеющегося на выходе дискретного демодулятора 27 в моменты приема сигнала настройки. Этот сигнал с помощью схем «И 31 стробируется распределителем 25 в отсчетных точках, затем полярность этого сигнала в отсчетных точках запоминается в накопителе 29, который через схемы «И 30 подключается ко входу схемы «ИЛИ 7 распределттелем Р в те моменты, когда формируется информация о полярности сигнала настройки з отсчетных точках.

На первой станции принятые от второй станции блоки информации выделяются соответствующими дешифраторами, а принятая )иформация о полярности сигнала настройки в отсчетных точках записывается с помощью распределителя 25 в дополнительные реперсивные регистры 24 дискретных регуляторов отводов 14.

Продвижение этой информации в дополнительных реверсивных регистрах 24 происходит одновременно во всех дискретных регуляторах отводов 14, в конце каждого принятого блока информации с помощью блока управления, управляемого, в свою очередь, распределителем 25. После принятия определенного числа блоков информации блок управлении

23 вырабатывает сигнал продвижения реверсивных регистров 15, код в разрядах которых изменяется по сигналам подключенных к ним дополнительных реверсивных регистров 24 (эти сигналы вырабатываются только

в том случае, если в данной отсчетной точке явно преобладает о.о:ин вид информации - «1 или «О). Изменение кода фиксируется з соответствующих блоках иамяти кода 22 и также через схемы «И 21 непосредственно

поступает на вход преобразователя «код-напряжение 2(9, выхо.дное напряжение которого (по постоянному току) изменяется в зависимости от кода, набранного в разрядах реверсивного регистра 15. Напряжение с выхода преобразователя 20 управляет работой схемы «НЕ 16, на другой вход которой поступает сигнал со схемы «И 13. На два входа схемы «И /5 поступают прямой и инверсный сигналы с соответствующего отвода регистра сдвига 10 (число отводов регистра сдвига равно числу дискретных регуляторов отводов, а сигнал на выходе каждого из этих отводов сдвинут на интервал времени, равный длительности посылки, передаваемой по каналу связи 19. Прямой или инверсный сигнал подключается ко входу схемы «НЕ 16 с помощью схемы «И 13, третий вход которой подсоединен к дополнительному выходу реверсивного регистра 15, в тот момент, ког.ца з этом регистре записано минимальное кодовое число, а дополнительный реверсивный регистр 24 формирует сигнал уменьшения этого числа. В этом случае появляется сигнал на дополнительном выходе реверсивного регистра /5, и

с помощью схемы «И 13 ко входу схемы «НЕ 16 подключается инверсный сигнал. При этом в реверсивному регистре кодовое чть сло возрастает на единицу. По сигналам с выхода схемы «И 13 схема «НЕ 16 преобразует постоянное напряжение, поступающее с выхода преобразователя «код-напряжение 20, в дискретно меняющийся по амплитуде модулированный сигнал данного отвода рргпстра сдвига 10 (пропорционально КОДУ, набпапрому в реверсивном регистре 15. Затем сигналы с выходов схем «НЕ 16 дискретных регуляторов отводов 14 поступают совместно с сигналом центрального отвода регистра сдвига 10 на сумматор напряжений 17. Тем самым но информации о полярности сигналов настройки в отсчетных точках модулированный сигнал корректируется методом его предискажения в месте формирования, т. е. на передаче. Затем сигнал, сформированный в сумматоре напряжений 17, ограничивается по снектру полосовым фильтром 18 и поступает в канал связи 19. Точно таким же образом управляются дискретные регуляторы отводов противоположной станции. Когда на одной из станций блок контроля 28, который подсоединен к выходу накопителя 29, определяет, что настройка корректора закончена, т. е. устранена межсимвольная интерференция, в датчике команд 12 формируется команда «Окончание настройки. Кроме того, с другого выхода блока контроля этой же станции сигнал об окончании настройки поступает в накопитель команд 5, который этот сигнал запоминает. На противоположной станции дешифратор команд 34, приняв эту команду, выдает сигнал о ее приеме в блок управления 23, который по этому сигналу перестает выдавать в дискретные регуляторы отводов 14 сигналы управления. Кроме того, этот сигнал поступает в накопитель команд 5, в котором также запоминается. Когда и на этой станции будет определено, что коррекция закончена, на противоположную станцию высылается команда «Окончание настройки, после принятия которой прекращается работа дискретных регуляторов отводов этой станции и в накопителях команд обеих станций зафиксируются сигналы об окончании настройки корректоров. Накопители команд 5 через схемы «ИЛИ-) 3 управляют работой переключателей режима работ 2, подключая ко входу дискретного модулятора / модема входную шину 6 и отключая выход схемы «ИЛИ 7. Одновременно сигналы с выходов схем «ИЛИ 3 отключают распределители 9, отключают блоки памяти кода 22 от реверсивных регистров 15, подключают выходы блоков 22 через схемы «И 21 ко входам преобразователей «код-напряжение 20 и отключают от них выходы разрядов регистров 15 дискретных регуляторов отводов 14. Если станции не смогли в заданное время закончить настройку корректоров, т. е. межсимвольные искажения не были устранены, блоки контроля 28 с помощью датчиков команд 12 формируют команды «Отказ от настройки, которые передаются на противоположные станции. Работа блоков памяти кода 22 поясняется схемой элемента памяти на фиг. 2 (число таких элементов памяти в каждом из блоков 22 равно чпслу разрядов реверсивного реги510 15 20 25 30 35 40 45 50 55 60 65 стра 15). Схемы «И-НЕ, применяемые в них, реализуют логическую операцию: ,01 1,,. В течение всего времени настройку на вход 57 поступает сигнал «1. Предположим, что на выходе 51 схемы «И-НЕ 41 был сигнал «О, а на выходе схемы «И-НЕ 42 - сигнал «1. Это соответствует тому, что на входе 40 присутствует сигнал «О. Следовательно, на выходе схемы «И-НЕ 55 будет сигнал «1, а на выходе схемы «И-НЕ 39 - сигнал «О. Если теперь на входе 40 появится сигнал «1, на выходах схем «И-НЕ 38 и 39 появятся сигналы «О и «1 соответственно. В этом случае на выходе схемы «И-НЕ 41 появится сигнал «1, а на выходе схемы «И-НЕ 42 состояние «1 сохранится до тех пор, пока напряжение на конденсаторе 46 не примет значения сигнала «1, т. е. конденсатор 46 зарядится через резистор 43, и только после этого на выходе схемы «И-НЕ 42 появится сигнал «О и через резистор 48 и диод 49 начнется разряд конденсатора 50. Если теперь, по истечении времени перезаряда конденсаторов 46 и 50, на входе 40 сменить сигнал «1 на сигнал «О, состояние схем «И-НЕ 38 и 39 -изменится на обратное, рассмотренный выше процесс повторится, и после заряда конденсатора 50 через резистор 47 изменится состояние схемы «И-НЕ 41. Следовательно, конденсатор 46 разрядится через резистор 44 и дпод 45, т. е. элемент памяти кода примет другое устойчивое состояние. Из рассмотренной выше динамики работы элемента памяти кода видно, что он представляет собой триггер с емкостными интеграторами в цепях обратной связи. Если на вход 37 вместо сигнала «1 подать сигнал «О, состояние элемента памяти кода зафиксируется и не будет зависеть от сигнала на входе 40. Влияние кратковременных перерывов питания и импульсных помех по цепям питания для такого элемента памяти кода также не опасно, так как помеха (или перерыв питания ) должна быть очень большой амплитуды, т. е. на выходах схем «И-НЕ 3S и 39 сигнал «1 должен перейти в этом случае в сигнал «О. Кроме того, длительность такой помехи или перерыва должна быть больше времени перезаряда конденсаторов 46 и 50. Предмет изобретения 1. Корректор сигналов дискретной информации, содержащий дискретный модулятор, регистр сдвига, соединенный через регуляторы с сумматором, дешифратор управления, распределитель, регенератор, генератор тактовых импульсов и подстроечный генератор, отличающийся тем, что, с целью упрощения устройства, выходы регенератора, распределителя и дешифратора управления подключены к соответствующим входам каждого регулятора.

2. Устройство по п. 1, отличающееся тем, что каждый регулятор состоит из двух схем «И, схемы «НЕ, преобразователя «код-напряжение, блока памяти кода, реверсивного регистра и интегратора, причем выход интегратора подключен ко входу реверсивного регистра, один выход которого через нервую схему «И подсоединен к одному из входов схемы «НЕ, к другому входу которой через преобразователь код-напряжение подключен выход второй схемы «И, а ко входам последней подключен второй выход реверсивного регистра непосредственно и через блок памяти кода.

3. Устройство по п. 2, отличающееся тем, что блок памяти кода состоит из триггеров, в каждом из которых выходы плеч подключены через параллельно соединенные резистор и цепь, состоящую из последовательно включенных диода и резистора, к соответствующим входам противоположных плеч и одновременно через емкость - к заземленному полюсу источника питания.

Первая станция

. 7

Втсрйя станция

- 4

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ КОРРЕКТОР ДЛЯ ДИСКРЕТНОГС КАНАЛА СВЯЗИФО!1Д mm | 1972 |

|

SU423254A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ МЕЖСИМВОЛЬНЫХИСКАЖЕНИЙ | 1972 |

|

SU439073A1 |

| Корректор с автоматической настройкой групповых трактов системы многоканальной связи | 1977 |

|

SU734885A1 |

| ГАРМОНИЧЕСКИЙ КОРРЕКТОР ДЛЯ КАНАЛА СВЯЗИ | 1971 |

|

SU312390A1 |

| ИОНОСФЕРНАЯ СТАНЦИЯВСЕСОЮЗНАЯПАТЕНТНО-1ЕШШ-;Е?КА^^БИБЛИОТЕКА | 1972 |

|

SU331354A1 |

| ВСЕСОЮЗНАЯ | 1973 |

|

SU372729A1 |

| АВТОМАТИЧЕСКОЕ СПРАВОЧНОЕ УСТРОЙСТВО | 1969 |

|

SU248741A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| Устройство приема и передачи дискретных сигналов | 1979 |

|

SU856031A1 |

| КОРРЕКТОР ДЛЯ КАНАЛА СВЯЗИ | 1970 |

|

SU277875A1 |

Авторы

Даты

1973-01-01—Публикация