1

Изобретение относится к цифровой вычислительной технике и может быть использовано в качестве счетчика числа имнульсов и ячеек памяти в электронно-счетных частотомерах.

Известны фазоимнульсные многоустойчивые элементы по авт. св. № 330256.

Предложенное устройство отличается тем, что вход цепи разряда источника напряжения компарации подключен к выходу схемы задержки. Это повышает надежность работы устройства.

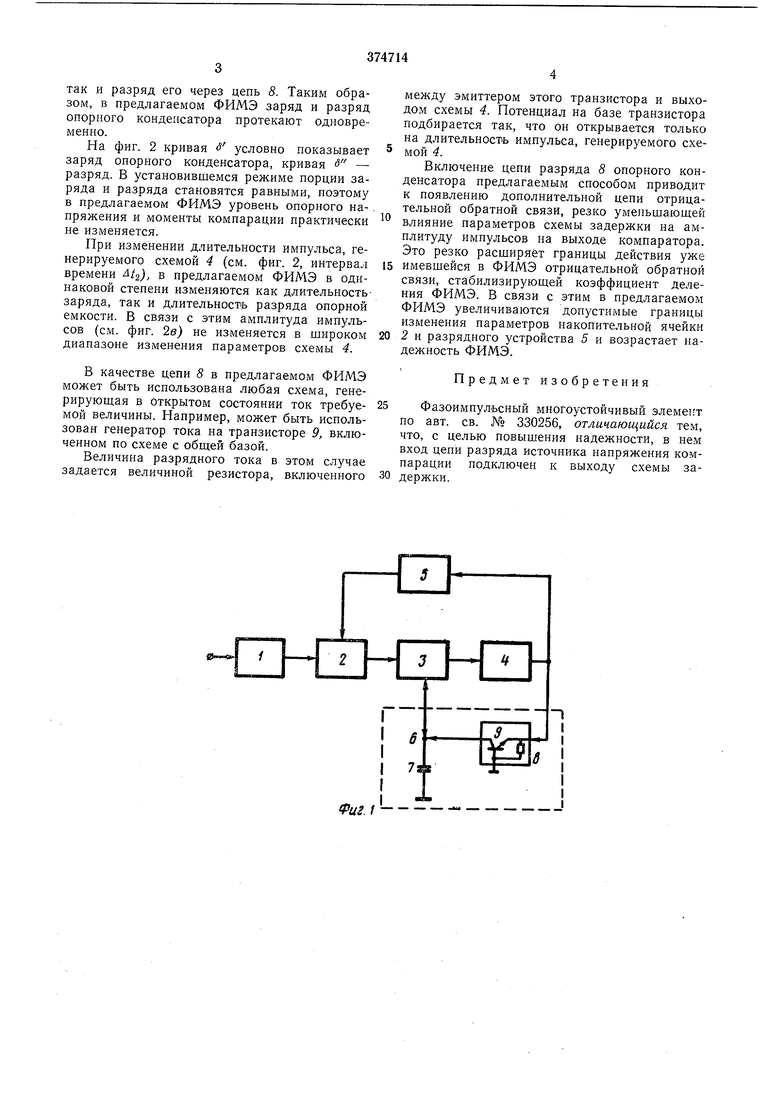

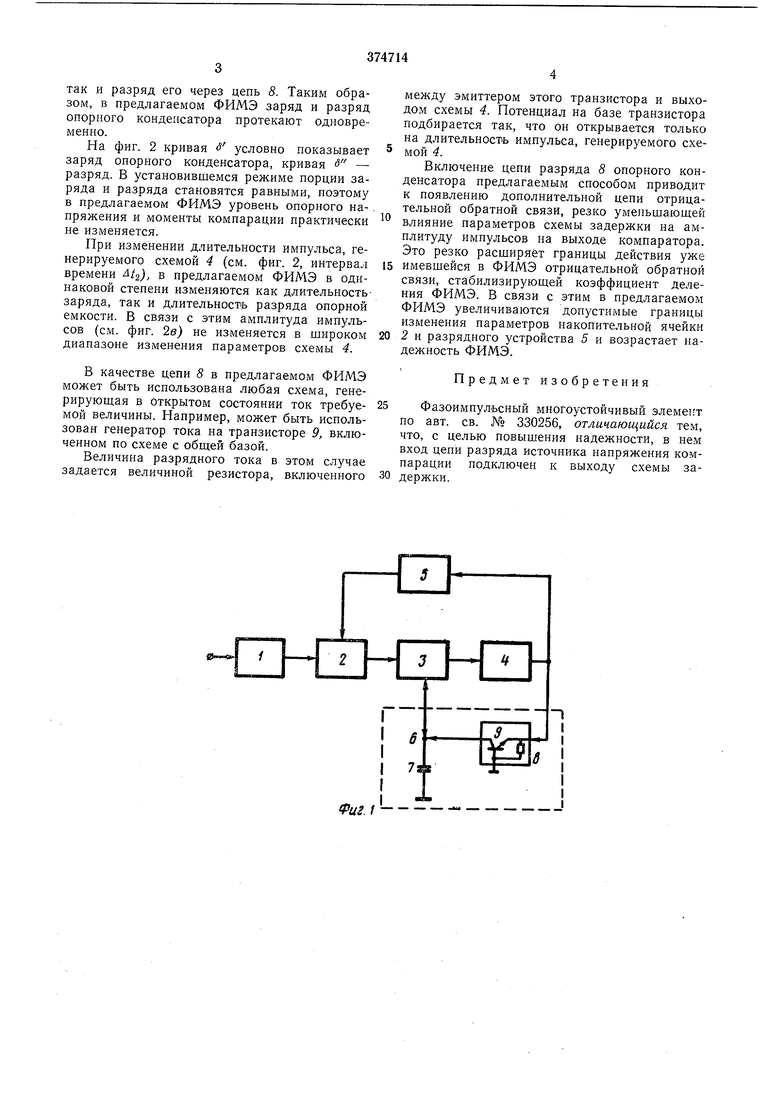

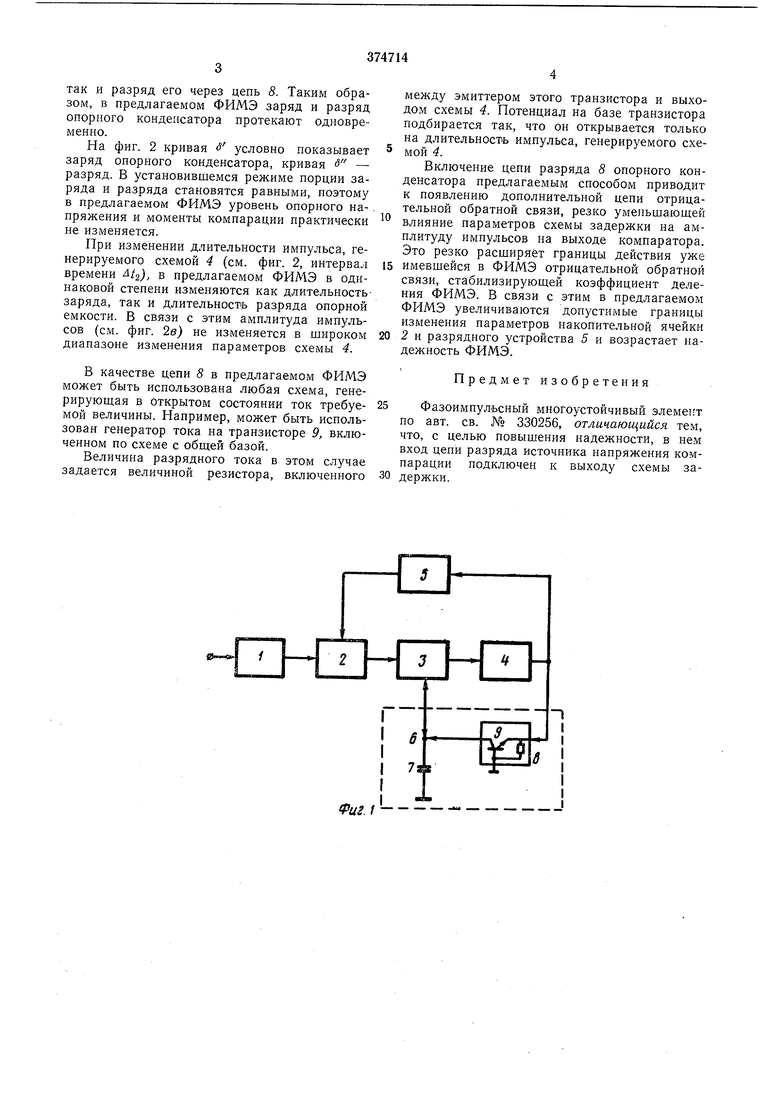

На фиг. 1 изображена блок-схема предлагаемого фазо-импульсного многоустойчивого элемента (ФИМЭ); на фиг. 2 - временные диаграммы, иллюстрирующие работу предлагаемого ФИМЭ, где: а - входные счетные импульсы и условная шкала фазовых состояний; б - ступенчатое напряжение на выходе накопительной ячейки 2 (кривая I) и напряжение на опорном конденсаторе (кривая II); в - импульс на выходе компаратора ; г - импульсы на выходе схемы 4 задержки.

Предлагаемый ФИМЭ состоит из входного усилителя-ограничителя 1, емкостной накопительной ячейки 2, компаратора 3, схемы 4 задержки, разрядного устройства 5, источника 6 напряжения компарации, состоящего из

опорного конденсатора 7, и цепи 8 разряда на определенную величину во времени.

Вход цепи разряда подключен к выходу схемы 4 задержки. Цепь разряда молсет быть

выполнена на транзисторе 9, база-коллекторный переход которого включен между одним из источников напряжения питания и опорным конденсатором, а эмиттер подключен через резистор к выходу схемы 4 задержки.

В ФИМЭ устанавливается коэффициент деления, равный п. Тогда при поступлении п-го импульса на вход ФИМЭ уровень напряжения на выходе ячейки 2 превышает уровень напряжения на опорном конденсаторе 7 (см.

фиг. 2 в, момент времени г).

Компаратор 3 открывается и п-ый перепад ступенчатого напряжения, вырабатываемого ячейкой 2, поступает через компаратор на опорный конденсатор 7 и па вход схемы 4 задержки, включая ее. Отрицательный импульс, длительностью t (см. фиг. 2г), возникающий при этом на выходе схемы 4, поступает на управляющий вход цепи, включая ее на время г,.

Задним фронтом импульса, вырабатываемого схемой 4, запускается устройство 5 и разряжает «накопительный конденсатор ячейки 2. С этого момента времени (см. фиг. 2 момент времени у прекращается как заряд опорного конденсатора п-ой ступенькой,

так и разряд его через цепь 8. Таким образом, в предлагаемом ФИМЭ заряд и разряд опорного конденсатора протекают одновременно.

На фиг. 2 кривая условно показывает заряд опорного конденсатора, кривая - разряд. В установившемся режиме порции заряда н разряда становятся равными, поэтому в предлагаемом ФИМЭ уровень опорного на- , пряжения и моменты компарации практически не изменяется.

При изменении длительности импульса, генерируемого схемой 4 (см. фиг. 2, интервал времени tz), в предлагаемом ФИМЭ в одинаковой степени изменяются как длительностьзаряда, так и длительность разряда опорной емкости. В связи с этим амплитуда пмпульсов (см. фиг. 2в) не изменяется в широком диапазоне изменения параметров схемы 4.

В качестве цепи 8 в предлагаемом ФИМЭ может быть использована любая схема, генерирующая в открытом состоянии ток требуемой величины. Например, может быть использован генератор тока на транзисторе 9, включенном по схеме с общей базой.

Величина разрядного тока в этом случае задается величиной резистора, включенного

между эмиттером этого транзистора и выходом схемы 4. Потенциал на базе транзистора подбирается так, что он открывается только на длительность импульса, генерируемого схемой 4.

Включение цепи разряда 8 опорного конденсатора предлагаемым способом приводит к появлению дополнительной цепи отрицательной обратной связи, резко уменьшающей влияние параметров схемы задержки на амплитуду импульсов на выходе компаратора. Это резко расширяет границы действия уже

имевшейся в ФИМЭ отрицательной обратной связи, стабилизирующей коэффициент деления ФИМЭ. В связи с этим в предлагаемом ФИМЭ увеличиваются допустимые границы изменения параметров накопительной ячейки

и разрядного устройства 5 и возрастает надежность ФИМЭ.

Предмет изобретения

ФазоимпулЬсный многоустойчивый элемент по авт. св. № 330256, отличающийся тем, что, с целью повышения надежности, в нем вход цепи разряда источника напряжения компарации подключен к выходу схемы задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФАЗОИМПУЛЬСНЫЙ МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ | 1972 |

|

SU330556A1 |

| Фазоимпульсный многоустойчивый элемент | 1967 |

|

SU486477A2 |

| ФАЗОИМПУЛЬСНЫЙ МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ | 1970 |

|

SU273272A1 |

| ФАЗОИМПУЛЬСНЫЙ МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ | 1972 |

|

SU344569A1 |

| Счетчик импульсов | 1978 |

|

SU746949A1 |

| Многоустойчивый элемент | 1975 |

|

SU529542A2 |

| ФАЗОИМПУЛЬСНЫЙ МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ | 1971 |

|

SU319050A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1971 |

|

SU298053A1 |

| Цифровой многоустойчивый элемент | 1975 |

|

SU529563A1 |

| ФАЗО-ИМПУЛЬСНАЯ | 1971 |

|

SU314312A1 |

б 7а

Фиг.{

Авторы

Даты

1973-01-01—Публикация