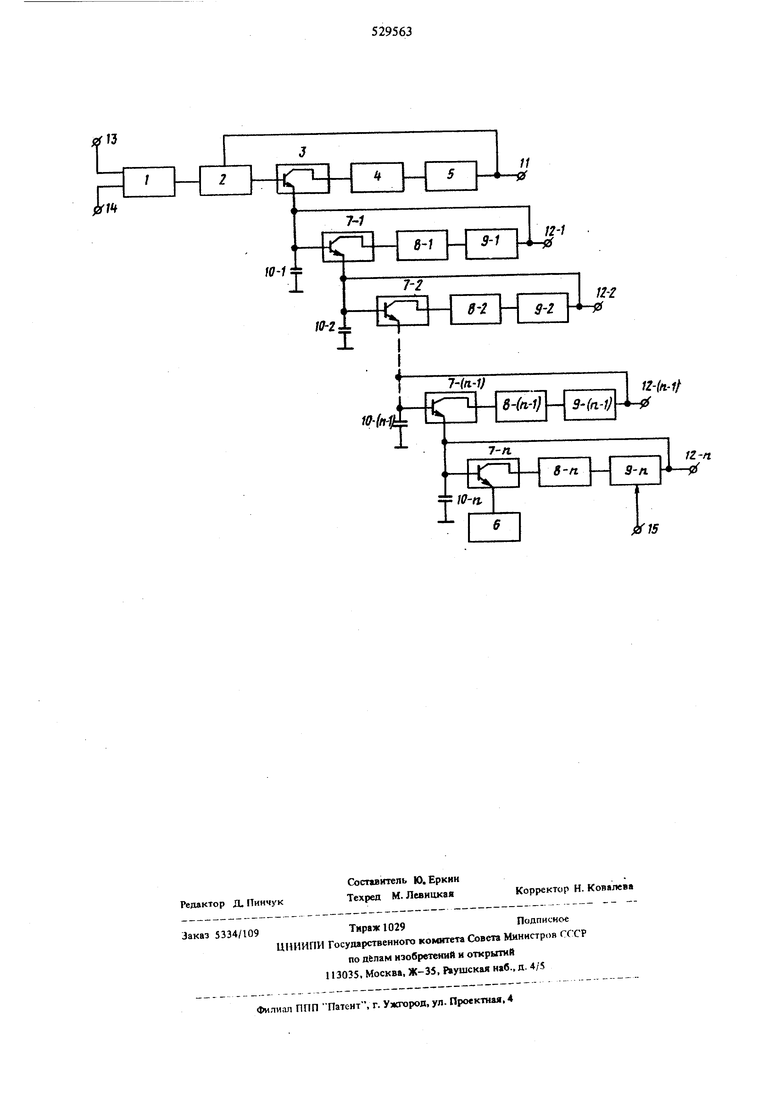

изобретение относится к радаотех1шке и может быть использовано в устройствах вычислительной техники. Известен цифровой многоустойчнвый элемент, содержащий последовательно соединенные делитель- ограничитель, накопитель, зарядный вход которого соединен с выходом усилителя-ограничителя, транзисторный компаратор, соеш{не1шый базой с выходом накопителя, а коллектором - с входом злеме1гга задержки, разрядное устройство, выход которого соединен с разрядным входом накопителя, источник напряжения компарацил 1. Однако этот элемент имеет срав1 ительно невысокую надежность и узкие фукниональные возможности. Цель изобретения - повышение надеха{ости и расширение функциональных возможностей элемента. Для этого в цифровом многоустойчивом эле менте между эммитером транзисторного компаратора и источником напряжения комшрации дополнительно введены последовательно соединенные п-транзисторных компараторов, п-элементов задержки и п-разрядных устройств. Эмиттер каждого П1-юдыдущего транзисторного компаратора соединен с базой каждого последующего, к базе каждого транзисторного компаратора подсоединен дополнительный конденсатор. На чертеже изображена структурная электрическая схема цифрового многоустойчивого элемента Он содержит последовательно соединенные усилитель-ограничитель 1, накопитель 2, зарядный вход которого соединен с выходом усилителя-ог раничителя 1, транзисторный компаратор 3, соединенный базой с выходом накопителя 2, а коллектором - с входом элемента задержки 4, разрядное устройство 5, выход которого соединен с разряд ным входом накопителя 2, источник напряжения компарации 6. Между эмиттером компаратора 3 и источником напряжения компарации 6 включены п последовательных цепей, состоящих из последовательно соединенных компараторов 7-1 - 7-п ,элементов задержки - S-n и разрядных устройств соответственно. Входы разрядных устройств - 9-п соеди нены с входами компараторов - 7-п,к базам которых подключены конденсаторы 10 - , соответственно. Выходы разрядных устройств 5,

- подключены к выходам 11 и соответственно.

Цифровой многоустойчивый элемент работает следующим образом.

Пусть в исходном состоянии все конденсаторы разряжены до нуля. Напряжение на выходе источника напряжения компарании 6 установлено на уровне, расположенном между значениями соответствующих заданных уровней.

В момент постунления первого счетного импульса на вход 13 или 14 напряжение на выходе накопителя 2 дискретно увеличивается до некото рой величины Д и. При этом в схеме протекают следующие процессы. Открьшается компаратор 3 и (Запускает элемент задержки 4. Одновременно начинается заргщ конденсатора через компаратор 3. В результате заряда конденсатора открывается компаратор и запускает элемент задержки . Начинается заряд конденсатора 10-2 через компаратор 7-1. Итак далее.

Комнаратор останется закрытым, так как по принятым начальным условиям к его эмиттеру приложен З1.:1|фающий потенциал источника напряжения компарации 6.

Так как коэффициент передачи транзисторных компараторов от базы к эмиттеру близок к единице, заряд конденсаторов 10-1 - происходит до напряжения, приблизительно равного AU. Задним фронтом импульсов элементов задержки 4, ,S 8(п-1).- запускаются соответственно разрядные устройства 5, - 9-(п-1) и разряжают конденсаторы 10-1 - lO-(n-l) приблизительно до нуля, а напряжете на конденсаторе равно ли.

В момент поступления второго счетного импульса все описанные процессы повторяются, за исключением того, что KONmapaTop 7(п-1) как и компаратор 7-п остается закрытым. Таким образом, к моменту постугшегшя третьего счетного импульса до напряжения, равного д U оказываются заряженными конденсаторы 10(п-1) и . Остальные конденсаторы разряжены до нуля. Последовательным отключением компараторов

конденсаторы - оказьшатотся заряженными до напряжения А U. За время следующего цикла конденсаторы - заряжаются до напряжения, равного 2 U . И так далее,пока они не зарядятся до требуемого напряжения,, заданного источником напряжения компарации 6. Для установки схемы в исходное состояние необходимо подать короткий импульс на вход 15 разрядного устройства .

Перевод многоустойчивого элемента в исходное состояние можно осуществить импульсом,подаваемым на один из входов у жлителя-ограничителя 1 после того, как все конденсаторы 10-1 - будут заряжены до требуемого напряжения,

Формула изобретения

Цифровой многоустойчивый элемент содержащий последовательно соединенные усилитель-ограничитель, накопитель, зарядный вход которого соединен с выходом усилителя-ограничителя, тран зист0рш й компаратор, соеданенный базой с выходом накопителя, а коллектором - с входом элемента задержки, разрядное устройство выход которого соединен с разрядным входом накопителя, источник напряжения компарации. отличающийся тем, что, с целью повыще101я надежности и расщмрения функциональных возможностей, в нем между эмиттером транзисторного компаратора и источником напряжения компарации дополнительно введены последовательно соединенные п транзисторных компараторов п элементов задержки и п разрядных устройств, причем эмиттер каждого предыдущего транзисторного компаратора соединен с базой каждого последующего, к базе каждого транзисторного компаратора подсоединен дополнительный конденсатор.

Источники информации, принятые во внимание при экспертизе;

1. Авт. св. СССР № 330556, М. Кл Н 03 К 29/00, 24.11.72 (прототип).

7- rtIj

V

Чл-r/

5-М|

Э(п.-1}

/2-/t

-У

| название | год | авторы | номер документа |

|---|---|---|---|

| ФАЗОИМПУЛЬСНЫЙ МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ | 1973 |

|

SU374714A1 |

| ФАЗОИМПУЛЬСНЫЙ МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ | 1970 |

|

SU273522A1 |

| Многоустойчивый элемент | 1975 |

|

SU529542A2 |

| ФАЗОИМПУЛЬСНЫЙ МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ | 1970 |

|

SU273272A1 |

| Многоустойчивый элемент | 1973 |

|

SU450331A1 |

| УСТРОЙСТВО ДЛЯ ПИТАНИЯ ИМПУЛЬСНЫХ НАГРУЗОК | 2009 |

|

RU2400013C1 |

| УСТРОЙСТВО ПРОВЕРКИ ИНДУКЦИОННЫХ ЭЛЕКТРОСЧЕТЧИКОВ | 2013 |

|

RU2532861C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1971 |

|

SU298053A1 |

| ФАЗОИМПУЛЬСНЫЙ МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ | 1972 |

|

SU330556A1 |

| Реле времени | 1980 |

|

SU868872A1 |

Авторы

Даты

1976-09-25—Публикация

1975-05-23—Подача