1

Изобретение относится к области вычислительной и Измерительной техники и может быть использова-но для сглаживания и центрирования случайных процессов.

Известные цифровые сглаживающие устройства, содержащие блок сглаживания, состоящий из накацливающего сумматора, соединенного с .регистром, обладают невысокой точностью сглаживания.

Целью изобретения является -повыщение точности сглаживания и расширения функциональных возможностей устройства.

Для достижения поставленной цели оно содержит дополнительный накапливающий сумматор, -входы п младщих разрядов которого соединены с выходами инверсного кода регистра и с соответствующими п входами устройства, а от старших и знаковый разряды - со знаковым входом устройства и с выходом инверсного кода знакового разряда регистра. Выходы прямого кода п старших разрядов сумматора поразрядно подключены к соответствующим входам п младших разрядов .накапливающего сумматора цифрового сглаживающего блока, а выход прямого кода знакового разряда сумматора - ко входам (т-1) старших и знакового разряда сумматора цифрового сглаживающего узла. Выходы прямого кода регистра соединены с выходами устройства.

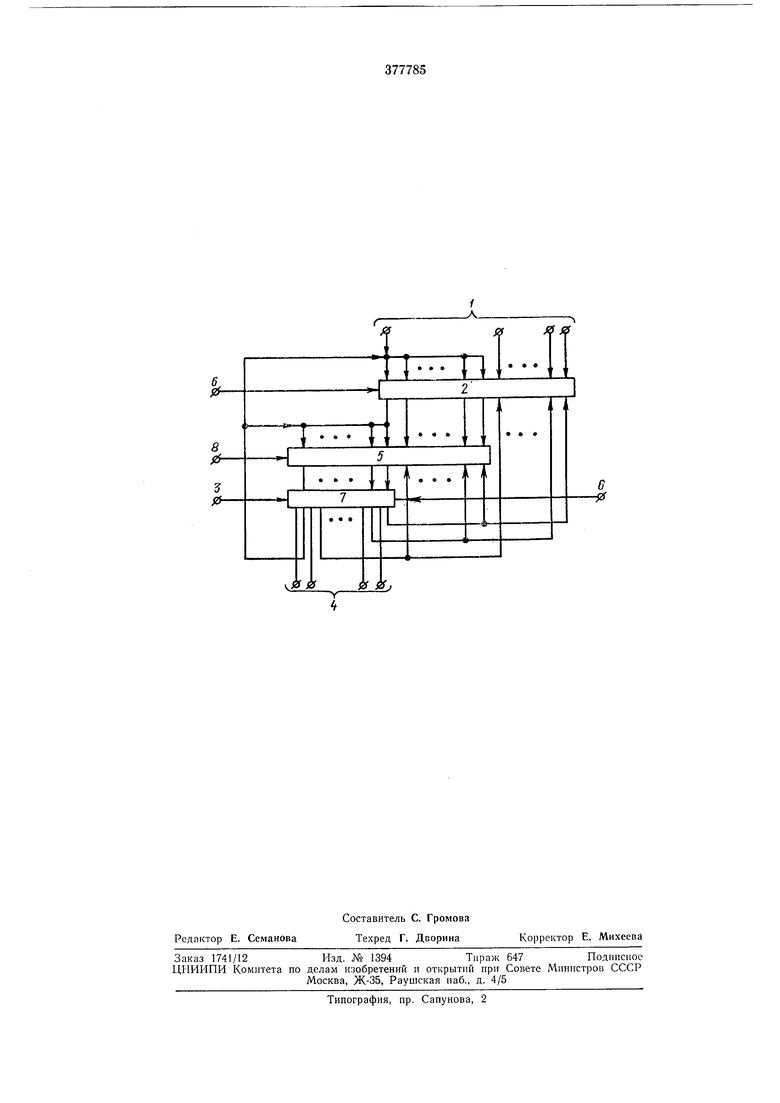

На чертеже 1Представлена блок-схема устройства.

Оно содержит входы /, дополнительный накапливающий сумматор 2, вход 3 устройства, выходы 4 устройства, накапливающий сумматор 5, вход 6 устройства и я-разрядный регистр 7. Емкость накапливающего сумматора 5 - .

В рассматриваемом устройстве реализуется цифровой алгоритм в виде рекуррентного сг отношения

1 ж

- («; ) -«.--I

(1)

, +

К,

где Xi - текущая дискрета входного процесса,

аг - текущая дискрета сглаженного процесса, причем ai ao 0, а Агмакс

2«.

Xi ,fnp, 7(2 Г2/пр fnp - частота ввода входной дискреты,

Т, 272 Т V2, где Г - выбранный интервал сглаживания.

Передаточная функция рассматриваемого устройства имеет вид

К(р) /iC,(p)-/«p)

(3)

l + K,(p)(p)

30 где Ki(p) передаточная функция интегрирующего звена, ЫР) - передаточная функция апериодического звена 1-го порядка. С учетом соотношений (3) и (4) имеем + 1 что Соответствует оператору Баттерворта II порядка с амплитудно-частотиой характеристикой вида () WTTfT / 1 -|- и фазочастотной характеристикой .р(со) arctg 1 - 0,37-2 Определение текущей дискреты сглаженного процесса производится за цикл, состоящий иг четырех тактов. Рассмотрим f-ый цикл работы устройства. Пусть после (г-1)-го цикла в сулМ.маторах 5 и 5 и в регистре 7 зафиксированы соответственно коды чисел (Xi - y-i-i), KZ-OI-I и В такте t, через входы 1 в сумматор 2 подается дискрета J,-. В сумматоре 2 фиксируется код числа 2 (Xi - аг,) -{- XiВ такте /2 на вход 5 подается кома.пдный импульс, производящий выдачу кода числа ai-i на ВЫХОД 4 и перепись кода числа (-osj-i) в сумматоры 2 и 5. При этом в сумматоре 2 Ii-i фиксируется код числа 2(г-;-a;-i) Е(л:(- -a(i)-|-(xi-at-i), а в сумматоре 5 - код числа K2-ai-i-0,1-1. В такте /з на вход 6 подается импульс, производящий сброс регистра 7 и перепись кода числа--2(;к;-a/ i) из сумматора 2 в суммаKi 1 0 тор 5, в котором фиксируется код числа 5 10 15 20 25 30 35 40 45 50 - a, Jf--L (xi - o.). В такте t подачей импульса .на вход 8 осуществляется перепись числа aj ai+i-{-ff-(i - -i-i - ) из сумматора 5 ,в реКгистр 7. /-ЫЙ цикл работы устройства заверщился. Код числа а,, зафиксированный в регистре 7, выдается на выход 4 в такте tz последующего (i+l)-ro цикла, который осуществляется в выщеоиисанной последовательности. Необходимо отметить, что, если , то выдается прямой код числа a, и на выходе прямого кода триггера знака регистра 7 импульс не появляется, если же , то «г выдается 1) иНверсном коде, а на выходе прямого кода триггера знака появляется импульс. В целях повышения точности вычислений .необходимо разрядности узлов рассматриваемого устройства увеличивать в сторону младших разрядов. Предмет изобретения Цифровое сглаживающее устройство, содержащее цифровой блок сглаживания, содержащий накапливающий сумматор, соединенный с регис-рром, отличающееся тем, что, с целью расширения функциональных возможностей устройства, оно содержит дополнительный накапливающий сумматор, входы п младших разрядов которого соединены с выходами инверсного кода регистра и с соответствующими п входа.ми устройства, а т старших и знаковый разряды-со знаковым входом устройства и с выходом инверсного кода знакового разряда регистра, -причем выходы прямого кода л старших разрядов сумматора поразрядно подключены к соответствующим входам л младших разрядов пакапл:ивающего сумматора цифрового сглаживающего блока, а выход прямого кода знакового разряда сумматора - ко входам (т-I) ста.рщих и знакового разряда сумматора цифрового сглаживающего узла, выходы прямого кода регистра соединены с .выходами устройства.

/ S

8 iH3

Д I

G

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU430382A1 |

| ЦИФРОВОЕ ЦЕНТРИРУЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU406196A1 |

| Цифровое сглаживающее устройство | 1974 |

|

SU643884A1 |

| Устройство для измерения частоты | 1982 |

|

SU1247773A1 |

| ОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВ | 1972 |

|

SU356644A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 2010 |

|

RU2444123C1 |

| Многоканальное цифровое сглаживающее устройство | 1976 |

|

SU633028A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Многоканальное цифровое сглаживающее устройство | 1978 |

|

SU748417A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2019 |

|

RU2720219C1 |

Даты

1973-01-01—Публикация