Изобретение относится к вычислительной и измерительной .технике и .может быть использовано для сгл.ажив ния и центрирования случайных процессов.. Известно цифровое сглаживающее устройство, содержащее параллельный накапливающий сумматор, регистр формирователь тактов, обладает мало точностью сглаживания и невысоким быстродействием Ij . Наиболее близким по технической сущности к предлагаемому является устройство, содержащее формировател токов, а в каждом канале параллель ный накапливающий сумматор с узлом сдвига в каждом разряде, п-р рядный вход и (п+г) -разрядный выход, где г - число младших дополнительных разрядов в сумматоре 2 Процедура сглаживания в каждом j -м канале устройства осуществляе ся за два такта, в соответствии с уравнением: V(.,,)/2, (1) где X - входная текущая дискрета сглаживаемой последователь ности. у,; - выходная текущая дискрета; j-(i,m)- номер канала, причем Первый такт -сложение, второй сдвиг полученного результата вправЪ на один разряд (осреднение), При вы.полнении последней операции возни.кает методическая погрешность усечения (отбрасывания), имеющаяот-, рицат.ельный знак, а её максимгшьное значение равно половине цены младшего разряда сумматора (-1/2) при нечетном результате сложения и минимальное значение (0)при четном. Справедливо полагая возникновение четного и нечетного результата сложения в сумматоре событием равновероятным, погрешность усечения можно считать независимой случайной переменной с равномерным распределением в области (О, -1/2) и средним значением ej -1/4. Для m канального устройства результирующая погрешность усечения составит: е -гп2 Для уменьшения этой погрешности увеличивают разрядность сумматора каждого канала на г дополнительных

гл адыих разрядов (длядробной части числа), что ведет к дополнительным аппаратурным затратам, а результирующая ошибка усечения в этом случае составит: - -()

:з)

Недостатки устройства - невысокая точность сглаживания, сравнительно большой объем оборудования и малое быстродействие.,

Цель предлагаемого изобретения повышение быстродействия и уменьшение средней величины методической погрешности вычислений.

Она достигается тем, что в устройстве, содержащем.m, п - разряд-, ых комбинационных сумматоров, (л - 1)-разрядных регистра и форирователь импульсов, выходы котоого соединены соответственно с таковыми входами (п-Г)-разрядных регистров , первая группа информационы входов, первого нз т, п - разрядных комбинационных сумматоров, крое старшего и младшего разрядов, является группой входов устройства, группа выходов т-го из m(n-l)-разядных регистров и BHxoii младше.горазряда т-го п-разрядногр комбинационного сумматора является группой выходов устройства, при этом пер- . . вая группа информацион.ных входов разрядов hro ( ,iii) n-разрядного комбинационного сумматора, кроме старшего и младшего разрядов, соединена соответственнр с группойвыходов ( i-1).-го ( i 2 , m) , (n- 1 ) разрядного регистра, причем вторая группа информационных входов разрядов i-ro { i-1,m), n-разрядного комбинационного сумматора, кроместаршего разряда , подключены соотвественно-к группе выходов i-ro ( i 1 , m) , (n-1) -разрядного регистра, вход формирователя импульсов является тактовым входом устройства, вторая группа информационнь1х входОв Ж адшйх разрядбв т, п -разрядных комбинационных сумматоров подключены к источнику напряжения логической 1, при этом группа 6fc3ходов разрядов -го { i-1,m), п-разрядного комбинационного сумматора, кроме младшего разряда, подключена к группе входов соответственно i( ,m), (п -1 )-разрядного регистра. :

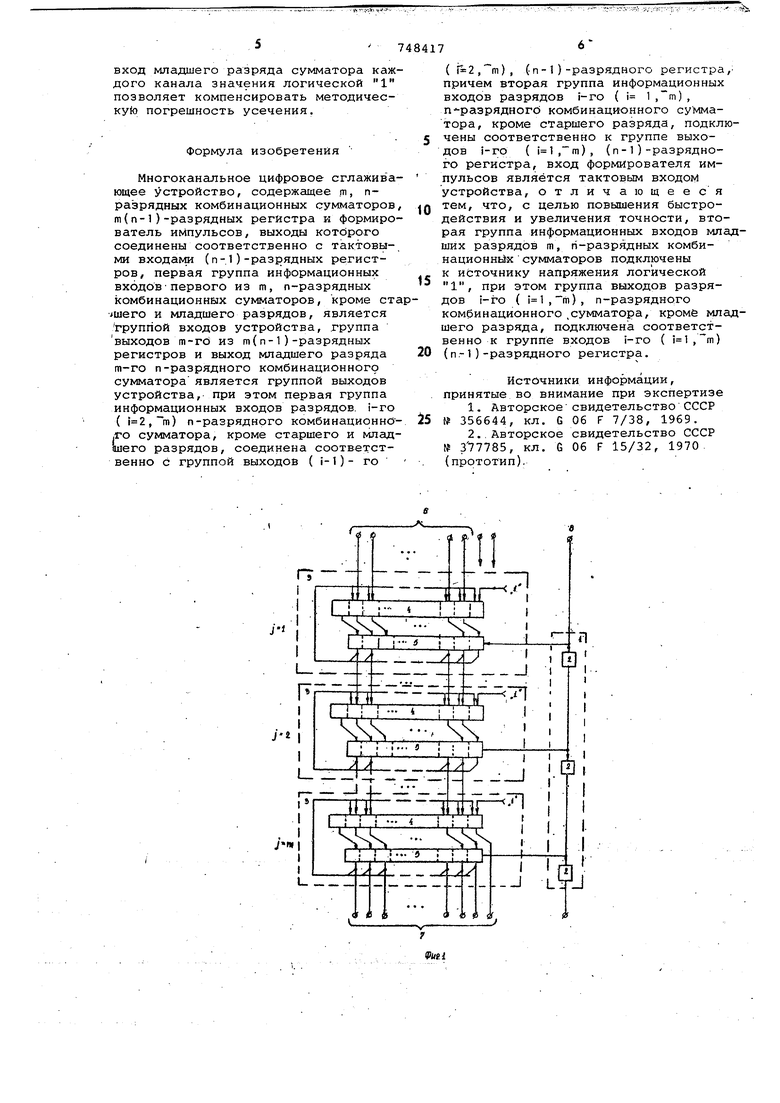

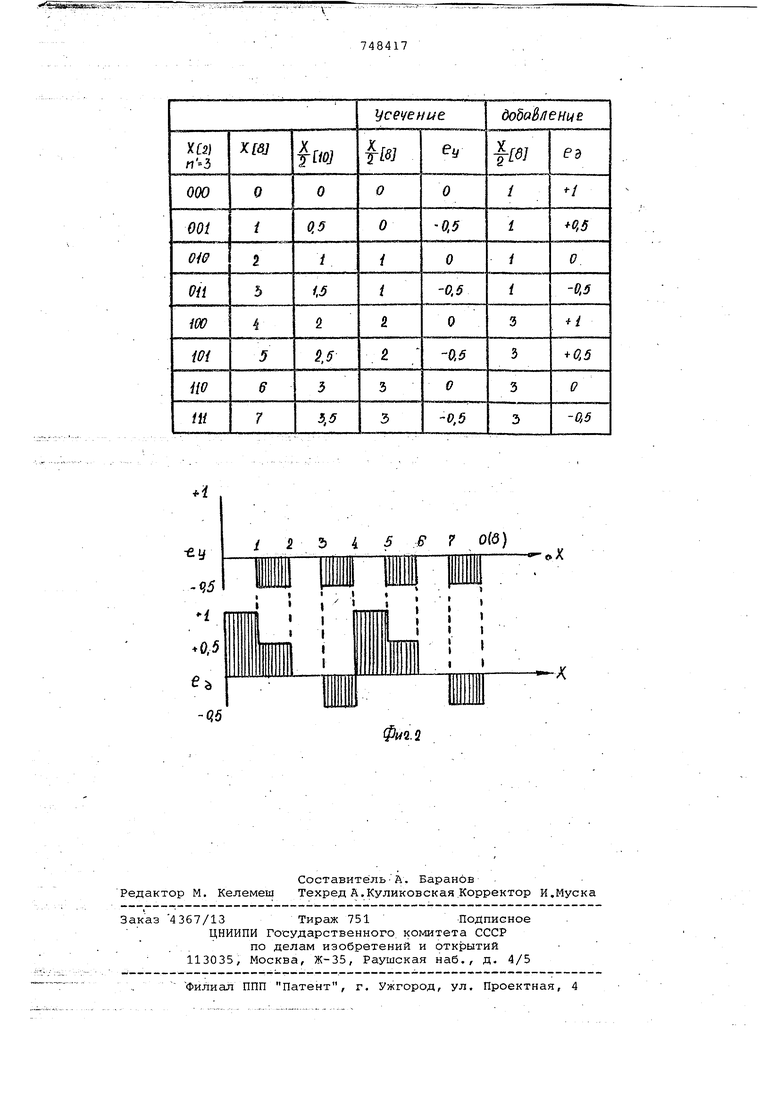

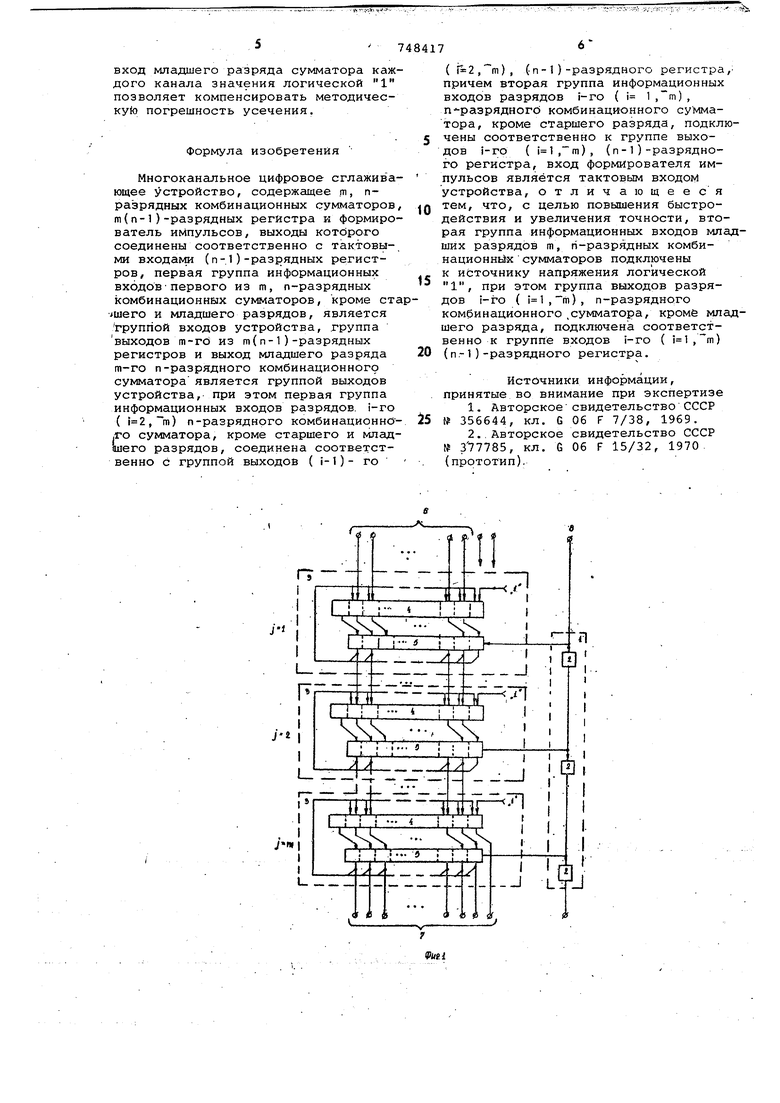

. 1 представлена блок-схема устройства; на фиг 2 - таблица и эпюры абсолютных погрешностей усечения и добавления.

Предлагаемое устройство содержит (фиг. 1) формирователь 1 с элементами 2 задержки, каналы 3, каждый из которых содержит п-разрядный комбинационный сумматор 4 и (п-1)-разрядный регистр 5, обра збванный двухтактным R5- или JK-триггерами; (п-2)-разрядный вход б, на который

поступает п-разрядный параллельный двоичный код текущей дискреты без учета двух младших разрядов; п-раз рядный выход 7, соединенный с (п-1) разрядным выходом регистра 5 и выходом младшего разряда сумматора 4 оконечного канала 3 устройства, управляющий вход 8..

Работа устройства осуществляется за один такт (сложение) в соответствии с уравнением (1):

n-iii

(4) -п-

J

причем текущие значения дискрет из (4).Xf,.j/2 и У. -/2 образуются при

переписи результата сложения с сумматора 4 в регистр 5 без учета младшего разряда сумматора. Кроме того,

Ьри передаче кода г . с регисра 5 предьщущего канала на сумматор 4 последующего канала, на второй информационный вход первого младшег разряда сумматора (вместо выхода млшего разряда регистра) постоянно заведен высокий уровень напряжения (лгическая 1), т.е. вводится погрешность дополнения (по аналогии с усе 1ением) , имеющая, как и рассмотренная выше погрешность усечения, вероятностный характер и равномерную плотность распределения в диапазоне (-1/2, +1) со средним значением ёэ +1/4.

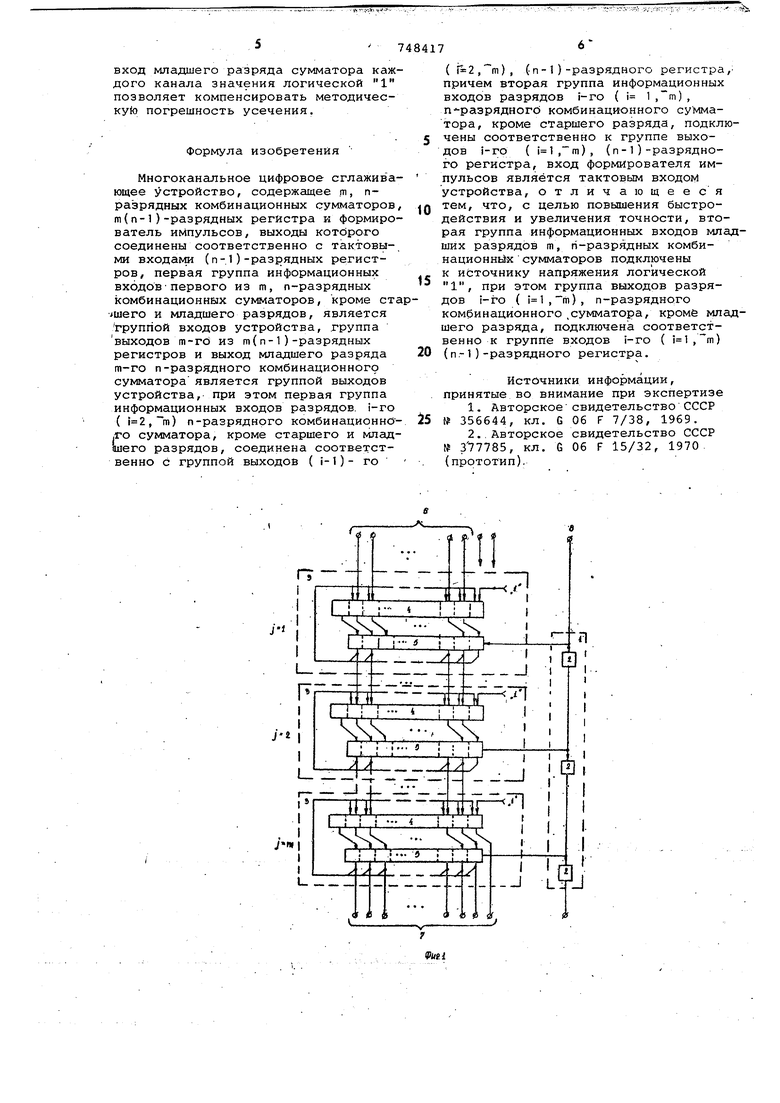

Динамика образования абсолютных погрешностей усечения и добавления для трех младших разрядов (п 3) текущих дискрет приведена в таблице и графиках на фиг. 2.

Следовательно., на информационные входы сумматора каждого j -го ка«нала устройства поступает значение с- погрешностью и значение f,-i,d/ погрешностью При выполнении операции сложения эти погрешности взаимно компенсируются. Операция сложения в каждом последующем канале осуществляется с задержкой (с помощью элемента задержки 2) по отношению к предыдущему каналу на время, равное или больше длительности тактирующего сигнала (строба) , поступающему на вход 8 формирователя тактов 1.

Таким образом, образование позиционных кодов текущих дискрет Хг,у/2 и V..j,j/2 с помощью предложенной выше схемы коммутации сумматора 4 и регистра 5 ведет к упрощению устройства и упразднению операции сдвига вправо на один разряд, т.е. к повышению быстродействия на один такт по сравнению с известным-, а введение на BTOpoifi информационный вход младшего разряда су1иматора каж дого канала значения логической 1 позволяет компенсировать методичесKyto погрешность усечения. Формула изобретения Многоканальное цифровое сглажива ющее устройство, содержащее т, празрядных комбинационных сумматоров m(n-)-разрядных регистра к формиро ватель импульсов, выходы которого соединены соответственно с тактовыми вxoдa Q (п-1)-разрядных регистров, первая группа информационных входовпервого из т, п-разрядных комбинационных сумматоров, кроме ст шего и младшего разрядов, является группой входов устройства, группа выходов т-го из m(n-1)-разрядных регистров и выход младшего разряда т-го п-разрядного комбинационного сумматора является группой выходов устройства, при этом первая группа информационных входов разрядов, i-ro ( ,m) n-разрядного комбинационно го сумматора, кроме старшего и млад шего разрядов, соединена соответственно с группой выходов ( i-1)- го ( .т) , (-п-1 )-разрядного регистра,; причем вторая группа информационных входов разрядов i-ro ( i 1 ,m) , П-разрядногб комбинационного сумматора, кроме старшего разряда, подключены соответственно к группе выходов i-ro ( ,m), (n-1 )-разрядного регистра, вход формирователя импульсов является тактовым входом устройства, отличающееся тем, что, с целью повышения быстродействия и увеличения точности, вторая группа информационных входов младших разрядов т, п-разрядных комбинационньЗх сумматоров подключены к источнику напряжения логической 1, при этом группа выходов разрядов i-ro ( ,m), n-разрядного комбинационного .сумматора, кроме младшего разряда, подключена соответственно к группе входов i-ro ( , m) (п.-1 )-разрядного регистра. Источники информации, принятые во внимание при экспертизе 1.Авторскоесвидетельство СССР № 356644, кл. G 06 F 7/38, 1969. 2.Авторское свидетельство СССР № 377785, кл. G 06 F 15/32, 1970 (прототип).

4 5 ff 0(6)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Цифровое сглаживающее устройство | 2022 |

|

RU2786204C1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Матричное устройство для решения уравнений в частных производных | 1985 |

|

SU1302276A1 |

| Многоканальное цифровое сглаживающее устройство | 1977 |

|

SU686034A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Цифровое сглаживающее устройство | 1983 |

|

SU1092520A1 |

| Устройство для умножения @ - разрядных чисел | 1989 |

|

SU1735843A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

Авторы

Даты

1980-07-15—Публикация

1978-06-12—Подача