1

Изобретение относится к области радиотехники и может быть использовано в системах коротковолновой телеграфной связи с движущимися объектами.

Известны устройства приема двоичных сигналов со случайной многолучевой структурой, содержащие входную цепь, синхронизатор, секционную линию задержки с корреляционными вычислителями в каждом отводе, сумматоры, селектор сравнения и линейные вычислители, каждый из которых состоит из последовательно включенных сумматора и .перемножителя на два входа.

Однако эти устройства конструктивно еложны.

С целью упрощения аппаратуры при приеме однополярных сигналов в предлагаемом устройстве выходы корреляционных и линейных вычислителей подключены к суммирующим входам последующих линейных вычислителей группами все сразу с выбыванием по одному со стороны максимальных номиналов задержки, а умножающие входы линейных вычислителей соединены с выходами ближайших по задержке корреляционных вычислителей, которые не включаются в данную цепь суммирования и умножения, причем входы линейных вычислителей, умножающие входы которых остаются свободными, связаны

через сумматор со входами селектора сравнения.

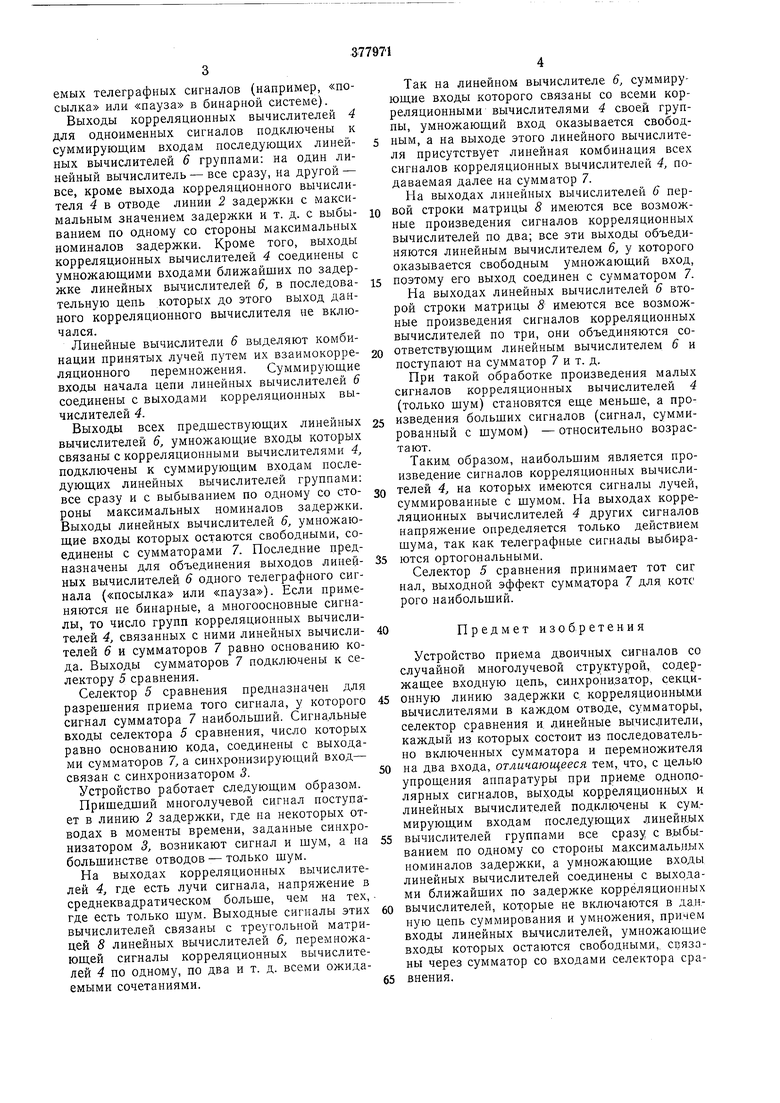

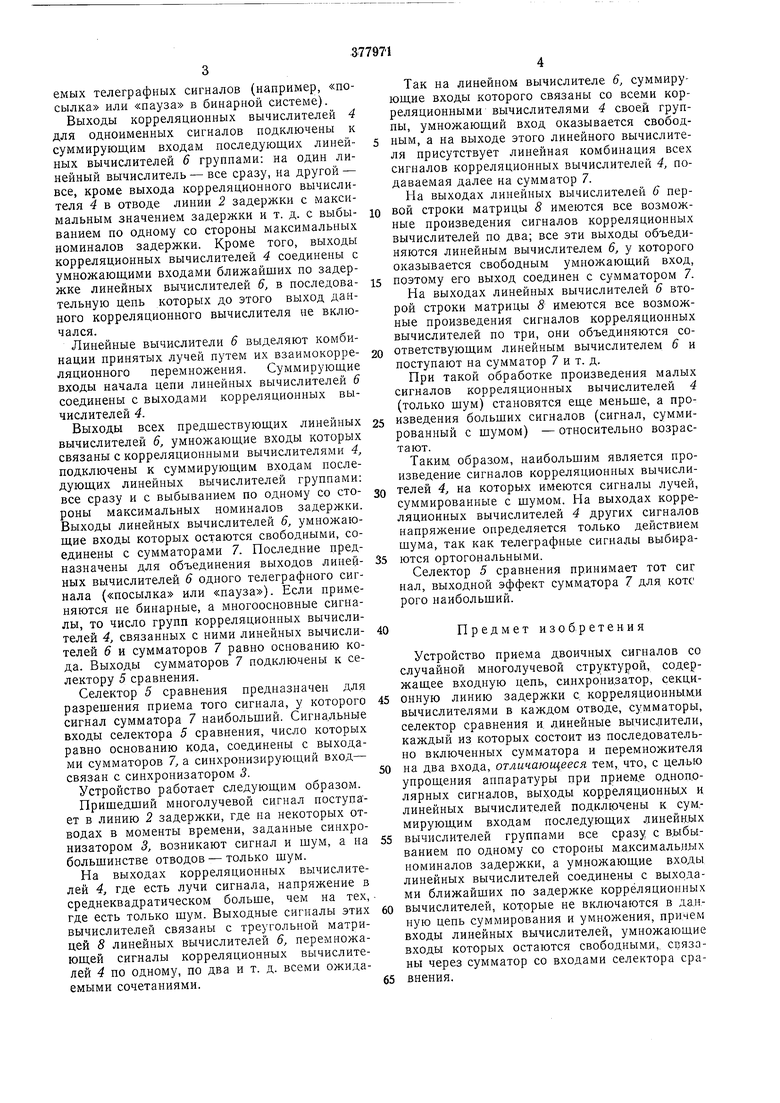

На чертеже приведена блок-схема предложенного устройства.

Входная цепь / устройства предназначена для предварительной селекции и усиления сигналов. Ее выход соединен со входом секционной линии 2 задержки и со входом синхронизатора 3.

Отводы секционной линии 2 задержки, предназначенной для временного разделения лучей сигнала, располагаются на интервале, равном интервалу корреляции используемых телеграфных сигналов. Общая задержка равна максимально возможной величине запаздывания последнего луча относительно первого. Выходы линии 2 задержки соединены с корреляционными вычислителями 4.

Синхронизатор 3 формирует опорные сигналы корреляционных вычислителей 4 и определяет момент разрещения приема селектором 5 сравнения.

Корреляционные вычислители 4 вычисляют взаимокорреляционные функции принимаемых и ожидаемых сигналов. Сигнальные входы корреляционных вычислителей 4 соединены с выходами линии 2 задержки, а опорные входы - с выходами синхронизатора 3, откуда на каждую группу корреляционных вычислителей подаются сигналы одного из ожидаемых телеграфных сигналов (например, «посылка или «пауза в бинарной системе).

Выходы корреляционных вычислителей 4 для одноименных сигналов подключены к суммирующим входам последующих линейных вычислителей 6 группами: на один линейный вычислитель - все сразу, на другой - все, кроме выхода корреляционного вычислителя 4 в отводе линии 2 задержки с максимальным значением задержки и т. д. с выбыванием по одному со стороны максимальных номиналов задержки. Кроме того, выходы корреляционных вычислителей 4 соединены с умножающими входами ближайщих по задержке линейных вычислителей 6, в последовательную цепь которых до этого выход данного корреляционного вычислителя не включался.

Линейные вычислители 6 выделяют комбинации принятых лучей путем их взаимокорреляционного перемножения. Суммирующие входы начала цепи линейных вычислителей 6 соединены с выходами корреляционных вычислителей 4.

Выходы всех предществующих линейных вычислителей 6, умножающие входы которых связаны с корреляционными вычислителями 4, подключены к суммирующим входам последующих линейных вычислителей группами: все сразу и с выбыванием по одному со стороны максимальных номиналов задержки. Выходы линейных вычислителей 6, умножающие входы которых остаются свободными, соединены с сумматорами 7. Последние предназначены для объединения выходов линейных вычислителей 6 одного телеграфного сигнала («посылка или «пауза). Если применяются не бинарные, а многоосновные сигналы, то число групп корреляционных вычислителей 4, связанных с ними линейных вычислителей 6 и сумматоров 7 равцо основанию кода. Выходы сумматоров 7 подключены к селектору 5 сравнения.

Селектор 5 сравнения предназначен для разрещения приема того сигнала, у которого сигнал сумматора 7 наибольщий. Сигнальные входы селектора 5 сравнения, число которых равно основанию кода, соединены с выходами сумматоров 7, а синхронизирующий вход,- связан с синхронизатором 5.

Устройство работает следующим образом.

Прищедщий многолучевой сигнал поступает в линию 2 задержки, где на некоторых отводах в моменты времени, заданные синхронизатором 3, возникают сигнал и щум, а на больщинстве отводов - только щум.

На выходах корреляционных вычислителей 4, где есть лучи сигнала, напряжение в среднеквадратическом больще, чем на тех, где есть только щум. Выходные сигналы этих вычислителей связаны с треугольной матрицей 8 линейных вычислителей 6, перемножающей сигналы корреляционных вычислителей 4 по одному, по два и т. д. всеми ожидаемыми сочетаниями.

Так на линейном вычислителе 6, суммирующие входы которого связаны со всеми корреляционными вычислителями 4 своей группы, умножающий вход оказывается свободным, а на выходе этого линейного вычислителя присутствует линейная комбинация всех сигналов корреляционных вычислителей 4, подаваемая далее на сумматор 7. На выходах линейных вычислителей 6 первой строки матрицы 8 имеются все возможные произведения сигналов корреляционных вычислителей по два; все эти выходы объединяются линейным вычислителем 6, у которого оказывается свободным умножающий вход,

поэтому его выход соединен с сумматором 7. На выходах линейных вычислителей 6 второй строки матрицы 8 имеются все возможные произведения сигналов корреляционных вычислителей по три, они объединяются соответствующим линейным вычислителем 6 и поступают на сумматор 7 и т. д.

При такой обработке произведения малых сигналов корреляционных вычислителей 4 (только щум) становятся еще меньще, а произведения больших сигналов (сигнал, суммированный с щумом) - относительно возрастают.

Таким образом, наибольшим является произведение сигналов корреляционных вычислителей 4, иа которЫХ имеются сигналы лучей, суммированные с щумом. На выходах корреляционных вычислителей 4 других сигналов напряжение определяется только действием щума, так как телеграфные сигналы выби-раются ортогональными.

Селектор 5 сравнения принимает тот сиг нал, выходной эффект сумматора 7 для коте рого наибольщий.

Предмет изобретения

Устройство приема двоичных сигналов со случайной многолучевой структурой, содержащее входную цепь, сипхрони.затор, секционную линию задержки с, корреляционными вычислителями в каждом отводе, сумматоры, селектор сравнения и. линейные вычислители, каждый из которых состоит из последовательно включенных сумматора и перемножителя

на два входа, отличающееся тем, что, с целью упрощения аппаратуры при прием.е однополярных сигналов, выходы корреляционные и линейных вычислителей подключены к суммирующим входам последующих линейных

вычислителей группами все сразу с выбыванием по одному со стороны максимальных номиналов задержки, а умножающие входы линейных вычислителей соединены с выходами ближайших по задержке корреляционных

вычислителей, которые не включаются в данную цепь суммирования и умножения, причем входы линейных вычислителей, умножающие входы которых остаются свободными,, связаны через сумматор со входами селектора сравнения.

Авторы

Даты

1973-01-01—Публикация