предсказания, сумматор 4, блок 5 задержки, вычислитель 6 корреляционных моментов, арифметический блок 7, определяющий прогностические коэффициенты, два регистра 8 и 9 памяти для хранения прогностических коэффициентов, два блока 10 и 11 сравнения этих коэффициентов с единицей, анализатор 12 нуля элемент И-НЕ 13, экстраполятор 14, на основе прогностических коэффи. ,

Изобретение относится к автоматике и технике передачи информации и может быть использовано при создании линий связи с дельта-модуляцией Цель изобретения - повьшгение помехоустойчивости.

На фиг.1 приведена блок-схема устройства на фиг.2 - функциональная схема блока адаптации на фиг .З- схема вычислителя корреляционных моментов; на фиг.4 - схема арифметического блока , на фиг. 5 - схема экст- раполятора.

Низкоскоростной дельта-модулятор содержит компаратор 1, триггер 2 задержки, блок 3 адаптации, сумматор 4, блок 5 задержки, вычислитель 6 корреляционных моментов, арифметический блок 7, первый 8 и второй 9 регистры памяти, первый 10 и второй 11 блоки сравнения, анализатор 12 нуля, элемент И-НЕ 13J экстраполятор 14, цифроаналоговьм преобразователь (ЦА11) 15. Первый вход компаратора 1 и синхронизирующий вход триггера 2 являются соответственно входом и тактовым входом устройства выход триггера 2 - выходом устройства.

Блок 3 адаптации (фиг.2) состоит из регистра 16 сдвига, блока 17 памяти, двух перемножителей 18 и 19, блока 20 задержки и управляемого инвертора 21.

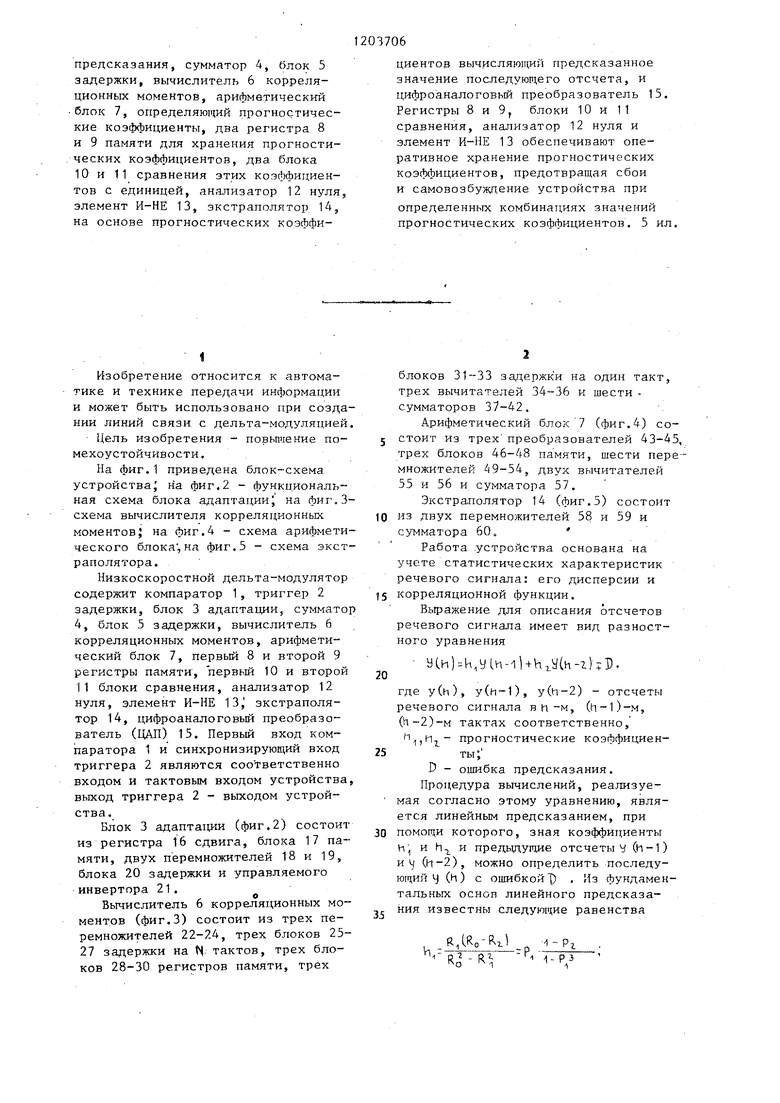

Вычислитель 6 корреляционных моментов (фиг.З) состоит из трех перемножителей 22-7.4, трех блоков 25- 27 задержки на N- тактов, трех блоков 28-30 регистров памяти, трех

циентов вычисляющий предсказанное значение последующего отсчета, и цифроаналоговый преобразователь 15. Регистры 8 и 9, блоки 10 и 11 сравнения, анализатор 12 нуля и элемент И-НЕ 13 обеспечивают оперативное хранение прогностических коэффициентов, предотвращая сбои и самовозбу51щение устройства при

определенных комбинациях значений прогностических коэффициентов. 5 ил

блоков 31-33 за,держк и на один такт, трех вычитателей 34-36 и шести - сумматоров 37-42.

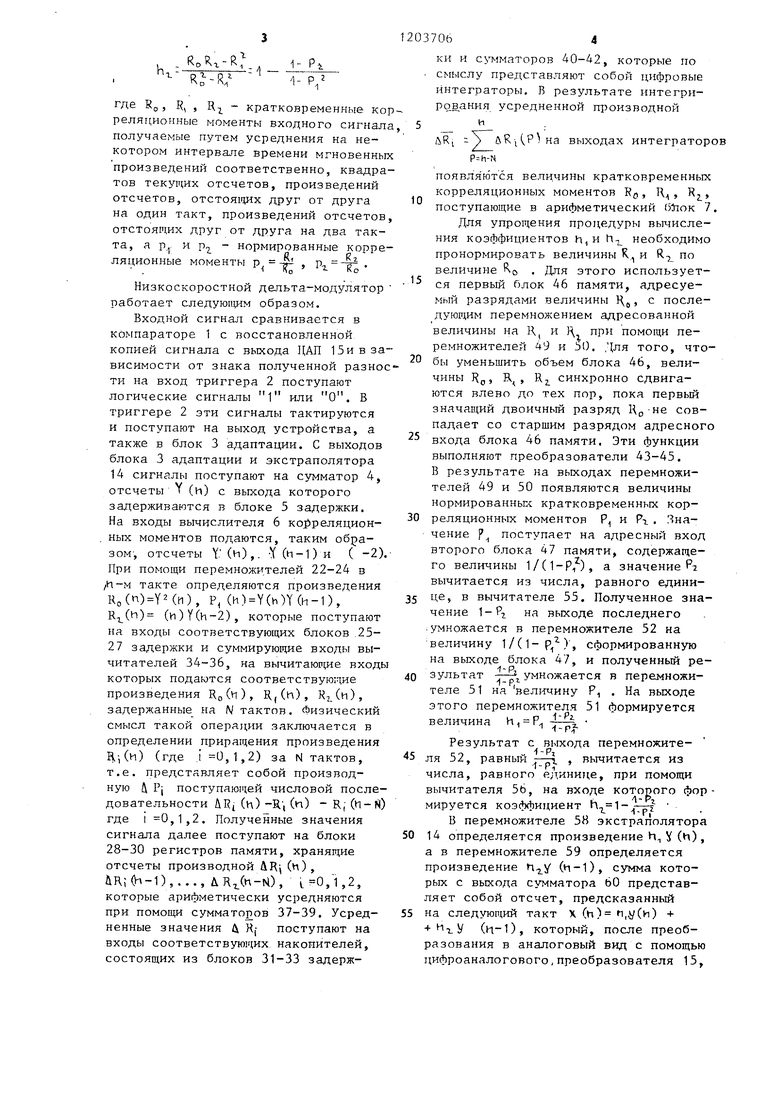

Арифметический блок 7 (фиг.4) со- стоит из трех преобразователей 43-45, трех блоков 46-48 памяти, шести перемножителей 49-54, двух вычитателей 55 и 56 и сумматора 57.

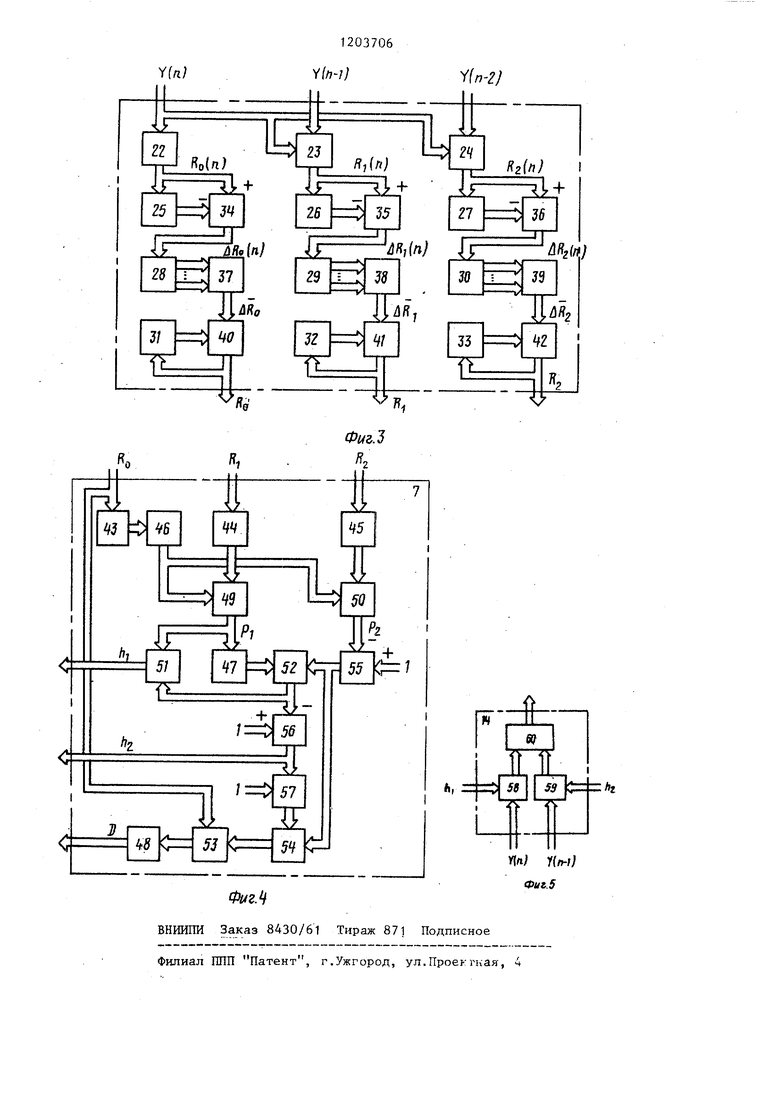

Экстраполятор 14 (фиг.5) состоит из двух перемножителей 58 и 59 и сумматора 60.

Работа .устройства основана на учете статистических характеристик речевого сигнала: его дисперсии и корреляционной функции.

Выражение для описания отсчетов речевого сигнала имеет вид разностного уравнения

20

yCh)b,yln-ll h y(h-zhl3,

где y(h), y(h-1), y(h-2) - отсчеты речевого сигнала в h-м, (И-1)-м, ()-M тактах соответственно, i., прогностические коэффициен- ты f

D - ошибка предсказания. Процедура вычислений, реализуе- мая согласно этому уравнению, является линейным предсказанием, при помощи которого, зная коэффициенты н;, и h и предыдущие отсчеты У (и-1) и ч (h-2), можно определить последующий tj (h) с ошибкой X) . Из фундаментальных основ линейного предсказания известны следующие равенства

R,(Ra-f.

H.V:

}

1- Pi

, n n -J I

RO-R.

1- РИ

где Kg, R, , Д - кратковременные кор реляционные моменты входного сигнала получаемые путем усреднения на некотором интервале времени мгновенных произведений соответственно, квадратов текущих отсчетов, произведений отсчетов, отстоя1 р1х друг от друга на один такт, произведений отсчетов отстоящих друг от друга на два такта, а p,j и р - нормированные корреляционные моменты р - , Рт 1 .

1

Низкоскоростной дельта-модулятор работает cлeдyюIU м образом.

Входной сигнал сравнивается в компараторе 1 с восстановленной копией сигнала с выхода ДАЛ 15ив зависимости от знака полученной разности на вход триггера 2 поступают логические сигналы 1 или О. В триггере 2 эти сигналы тактируются и поступают на выход устройства, а также в блок 3 адаптации. С выходов блока 3 адаптации и экстраполятора 14 сигналы поступают на сумматор 4, отсчеты I (h) с выхода которого задерживаются в блоке 5 задержки. На входы вычислителя 6 ко)реляцион- ных моментов подаются, таким образом, отсчеты Y (h),. -Y (h-1) и ( -2). При помощи перемножителей 22-24 в /И-м такте определяются произведения Ro()Y4M), р (H)Y(h)Y(h-l), R() (и)У(н-2), которые поступают на входы соответствующих блоков .25- 27 задержки и суммирующие входы вы- читателей 34-36, на вычитающие входы которых подаются соответствующие произведения R (1) R., (п), К,, (и), задержанные на N тактов. Физический смысл такой операции заключается в определении приращения произведения , (и) (где i 0,1,2) за N тактов, т.е. представляет собой производную / Pj поступаю1цей числовой последовательности URi (h) -R l (n) - R| (И-Ю где i 0,1,2. Полученные значения сигнала далее поступают на блоки 28-30 регистров памяти, хранящие отсчеты производной AR|(и), UR;(h-1), .,., UHjn-M), ,1,2, которые арифметически усредняются при помощи сумматоров 37-39. Усредненные значения А Hf поступают на входы соответствующих накопителей, состоящих из блоков 31-33 задерж10

2037064

ки и сумматоров 40-42, которые по смыслу представляют собой цифровые интеграторы, В результате интегри- Родания усредненной производной

5 :

ДЯ; -у uR( выходах интеграторов

появляются величины кратковременных корреляционных моментов Rj,, R , R., поступающие в арифметический 6tioK /. Для упрощения процедуры вычисления коэффициентов и, и h необходимо пронормировать величины R и R-j по величине . Для этого использует- ся первый блок 46 памяти, адресуемый разрядами величины Н, с последующим перемножением адресованной величины на R и Д при помощи перемножителей 49 и 50. Лля того, чтобы уменьшить объем блока 46, величины Rg, R , R синхронно сдвигаются влево до тех пор, пока первый значащий двоичный разряд совпадает со старшим разрядом адресного входа блока 46 памяти. Эти функции выполняют преобразователи 43-45. В результате на выходах перемножителей 49 и 50 появляются величины нормированньЕс кратковременных корреляционных моментов Р и Рг . Значение р поступает на адресный вход второго блока 47 памяти, содержащего величины 1/(1-Р/), а значение PTI вычитается из числа, равного едини- 35 це в вычитателе 55. Полученное значение 1-Рг на выходе последнего .умножается в перемножителе 52 на величину 1/(1-р), сформированную на выходе блока 47, и полученный рев пере 1ножи- . На выходе

20

25

30

40

t-P,

зультат --л умножается

I Р

теле 51 на вел1-1чину Р,

этого перемножителя 51 формируется

величина hi P - Л.

45

-r,

Результат с выхода перемножителя 52, равный --т. , вычитается из числа, равного едини ;е, при помощи вычитателя 56, на входе которого формируется коэффициент

В перемножителе 58 экстраполятора

50 14 определяется произведение h V(и), а в перемножителе 59 определяется произведение (п-1), сумма которых с выхода сумматора 60 представляет собой отсчет, предсказанный

55 на следующий такт Х(п)М,уСи) + (ц-1), который, после преобразования в аналоговый вид с помощью цифроаналогового,преобразователя 15,

сравнивается компаратором 1 в следующем такте с сигналом 5(h + 1), Компаратор 1, в Свою очередь, определяет знак разности предсказанного и действительного отсчетов сигнала а для того, чтобы определить величину этой разности, совместно с вычислением предсказанного значения ч(и) проводится вычисление ошибки прогнозирования D ,

Ошибка прогнозирования определяется выражением

/

D VlRo-h.

оК1-Рг)(г-)|Для обеспечения устойчивости дельта-модулятора используется коэф-

фициент D (и) К(п) ™ зволяюрщй учитывать быстрые изменения входного сигнала, так как коэффициент К(и) вычисляется из последних 2-4 битов передаваемой Щ послед(мза- тельности. Коэффициент K(h) вычисляется в каждом такте с использованием предыдущего значения К(И ) lC(h-1). где -- адаптационный множитель, который определяется из да последова , тельности следующим образом,- Если, к примеру, четыре последних бита ДО последовательности составляют комбинацию 0101, что говорит об отсутствии перегрузки дельта-модулятора, то коэффициент ,87. В случае, если появляется комбинация 1111 или ОООС, что говорит о перегрузке, то 1 ,15 что в сущности ведет к увеличению значения ошибки D(n)f (1)()) . В случае комбинации типа 0011 ,. Аппаратно реализовано это следующим образом (фиг.4), Значение складывается с единицей при помоши Сумматора 57. Полученное на выходе значение 2-г в перемножителе 54 умножается на значение l-Pj, с выхода вычитателя 55 С выхода перемножителя 54 значение (. PZ) ( - г -г, умножается в перемножителе 53 на коэффициент Дд с выхода сумматора 40. Полученное значение RO( 1 Р г - :j-р ) адресует своими разрядами третий блок 48 памяти, содержащий значение квадратного корня из адрес- ного слова, т.е. v/До (1 - р) (2-1; .

Биты ДМ последонательности в каждом такте последовательно записываются в регистр 16 сдвига в блоке 3

адаптации (фиг.2) с выхода тактируемого триггера 2 задержки. Сформированный таким образом отрезок ЛМ последовательности адресует блок 17 памяти, который содержит необходимые значения . С выхода блока 17 значения , умножаются в перемно- жителе 18 на значение ((h-l), имеющееся на выходе блока 20 задержки. Полученное на значение K(h) 1 K() поступает на вход блока 20 задеряки для использования его в следующем такте и на первые входы перемножителя 19, которг-ш формирует произведение

p((h)

lRo((VPJ(

,. -l-p,

50

55

0

5

0

в качестве абсолютного значения ошибки предсказания эта величинаJ)fh) поступает на вход управляемого инвертора 21., В следующем такте, после сравнения компаратором 1 зна-. чения X (п) и значения 5 (h+l) с выхода ЦДЛ 1.5 в зависимости от бита. ДМ последо.вательности значение Р( П) бу/гет проинвертировано нли нет, .ггочле чего оно поступает на вход с 7-1матора- 4, с помощью которого из предсказанного значени я (и) вы- ч-итается абсолютное значение Р (h) i -iiii К X (h ) прибавляется абсолютное значение Т) (h), Таким образом в следующем такте формиру-ется отсчет У (h+1), и процесс предсказания в следующем (п + О-м такте повторяется.

Устойчивость работы дельта-модулятора значительно зависит от величины кoэффиlI eнтoв Ь и h., . Для

обеспечения устойчивости работы дельта-модулятора должн.ы выполняться следующие неравенства: (, j причем h., и hj не могут -быть одновременно равны нулю. Для проверки этих условий коэффициенты h.., и hj записываются в регистры 8 и 9 памяти, в блоки 10 и 11 сравнения, реализующие контроль приведенных неравенств, и в анализатор 12 нуля, определяющий равенство нулю обоих коэффициентов h и h одновременно. Элемент И-НЕ 13 запре1цает запись в регистры 8 и 9 вычисленных в текущем такте значений hi и h в случае, если любое из приведенных условий нарушается. В этом случае для предсказания последующего отсчета

7

X(h) используются предыдущие знача ния коэффициентов hj, находящи- еся в регистрах 8 и 9 памяти. Если же условия выполняются, т.е. на выходах блоков 10 и 11 сравнения и анализатора 12 нуля отсутствуют сигналы, то элемент 13 разрешает запись в регистры 8 и 9 памяти вычисленных в текущем такте значений Ц и hj и предсказание пос;|едующег отсчета Jd (h) производится с помощью .коэффициентов h и h2 записанных в регистры 8 и 9 памяти в текущем такте..

Формула изобретения

Низкоскоростной дельта-модулятор содержащий триггер задержки, блок адаптации, цифроаналоговый преобразователь, сумматор, экстраполятор, блок задержки, вычислитель корреляционных моментов, арифметический блок и компаратор, первый вход которого является входом устройства, второй вход соединен с выходом циф- роаналогового преобразователя, выход компаратора подключен к входу триггера задержки, синхронизирующий вход которого соединен с -тактовой шиной, а выход подключен к первому входу блока адаптации и является выходом устройства,- вторые входы блока адаптации соединены с соответствующими первыми входами арифметического блока, первые, вторые и третьи входы которого подключены к

fl;037068

соответствующим выходам вычислителя корреляционных моментов, первые и вторые входы которых объединены с соответствующими входами экстраполято- 5 ра и подключены к соответствующим выходам блока задержки, третьи выходы которого соединены с соответ- ствуюгщми третьими входами вычислителя корреляционных моментов, входы 10 блока задержки подключены к соответствующим выходам сумматора, первые входы которого соединены с соответствующими выходами блока адаптации, а вторые входы объединены с соответ- 5 ствующими входами цифроаналогового преобразователя и подключены к выходам экстраполятора, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены анализатор нуля, первый и второй блоки сравнения, элемент И-НЕ и первый и второй регистры памяти, выходы которых подключены соответственно к третьим и четвертым входам экстраполятора, управляющие входы регистров памяти объединены и подключены к выходу элемента И-НЕ, входы которого соединены с выходами блоков сравнения и анализатора нуля, первые и вторые входы которого объединены с соответствующими входами соответственно первых регистра памяти и блока сравнения и вторых регистра памяти и блока сравнения и подключены соответственно к вторым и третьим выходам арифметического блока.

20

5

0

5

Фиг.2

Фи.З

я.

| название | год | авторы | номер документа |

|---|---|---|---|

| Низкоскоростной дельта-модулятор | 1987 |

|

SU1476612A2 |

| Устройство для оценки параметров многолучевого канала связи | 1991 |

|

SU1781828A1 |

| Адаптивный дельта-кодер | 1988 |

|

SU1658384A1 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

| Дельта-модулятор | 1987 |

|

SU1444953A1 |

| Устройство для оценки параметров многолучевого канала связи | 1987 |

|

SU1494233A2 |

| Устройство для регистрации сейсмических сигналов | 1989 |

|

SU1681288A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| АДАПТИВНАЯ СИСТЕМА РЕГУЛИРОВАНИЯ ПРОЦЕССА КОНТРОЛЯ НА МЕТАЛЛОРЕЖУЩЕМ СТАНКЕ | 1990 |

|

RU2042168C1 |

Изобретение относится к технике передачи информации и предназначено для качественного преобразования речевых сигналов в цифровую форму при низких скоростях передачи. Изобретение позволяет повысить помехоустойчивость дельта-модулятора за счет устранения сбоев и предупреждения самовозбуждения. Низкоскоростной дельта-модулятор содержит компа- ратор 1, триггер 2 задержки, блок 3 адаптации, формирующий ошибку -ЧГКБ П сГ Г 1 сл to о со о Од

| Система связи с дельта-модуляцией, адаптивной к спектру речи | 1974 |

|

SU558411A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| International Conference on Communications, Toronto, 1978, V.3, p | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

Авторы

Даты

1986-01-07—Публикация

1984-05-10—Подача