1

Уст;ройство относится к авто матике и вычислительной технике.

Известен цифровой компаратор, содержащий дв,а регистра, суммирующие входы кото,рых через две схемы запрета связаны со входной шлной устройства; блок сравнения, входы двух входовых схем «Ндравяозвачность которого связаны с дрямьши выходами одноименных разрядов регистров, а выходы через схему «ИЛИ связаны со входом -инвертора; два блока переписи, одни .из входов двухв,ходовььх схем «И которых связаны с прЯМЫми выхода|М,и одного регистра, -причем другие входы схем «И соединены между собой и через лйНИЮ задержки связа ы со входом «оброс другого регистр а, входы установки в единичное состояние которого соединены с выходами этих схем логические схемы; линии задержки; триггеры.

Однако известные комлараторы могут быть использованы только для онределенля пай-большего или наименьщ его числа из групп пойледовательных чисел. При объединемии ко.мпараторов разных типцов увеличивается количество оборудования и устройство усложняется. . . .

Предложенный комнаратор отличается тем. что в него .вве-дены третий, и четвертый регистры, выходы которых связаны со входами

сравнения, причем выходы третьего регистра связаны со входами, блока перениаи, выходы котор ого соединены со .н уста нозки в единичное состояние .второго регистра, и

через схему «ИЛИ - с управляющим входо 1 схемы запрета первого .регистра и одним из входов схемы «И,, другой .вход которой связан со входно й щиной устройства, а выход - с вьгчитающнм входр м, третьего рег|истра. Выходы Т1р етьего рег,истр.а соедил ены с выходами второго блока переписи, кото.рого связаны с выходами первого. .ре.гистра. Выход сравнения связан со .входом установк} в единичное со.стоян.ие триггера, вход устан-овки в нулевое состояние Которого соедииен с упр.авляющи.м входОдМ второго . б.лока переписи. Инверсный выход триггера схему «И, связанную с . , и схе.му «ИЛИ, связанную через..;}инию, за.держки с

упра вляющим входом, .первого блока переписи, соединен со входом .«оброс третьего репистра и с yпpaвля pu.J, входом . с.хемы запрета второго .регистра.. .й..выход триггера через схему увязанную с шиной

, соединен .ср.,.входом «Сброс четвертого регистра; вых.одь. neppqm регистра связа.ны с ВЫХОД.НЫ.МИ .ii.y. наибольше го ч})сла, выходы вто.ррго, рег.и.с.тр.а - с. шина.мп наименьшего числа, .а. ч.етвертого - с щина.ми ..мальной.р.а,зностИ- .-...

Это позволяет .расширить функциолальныс воз.можност и устройства.

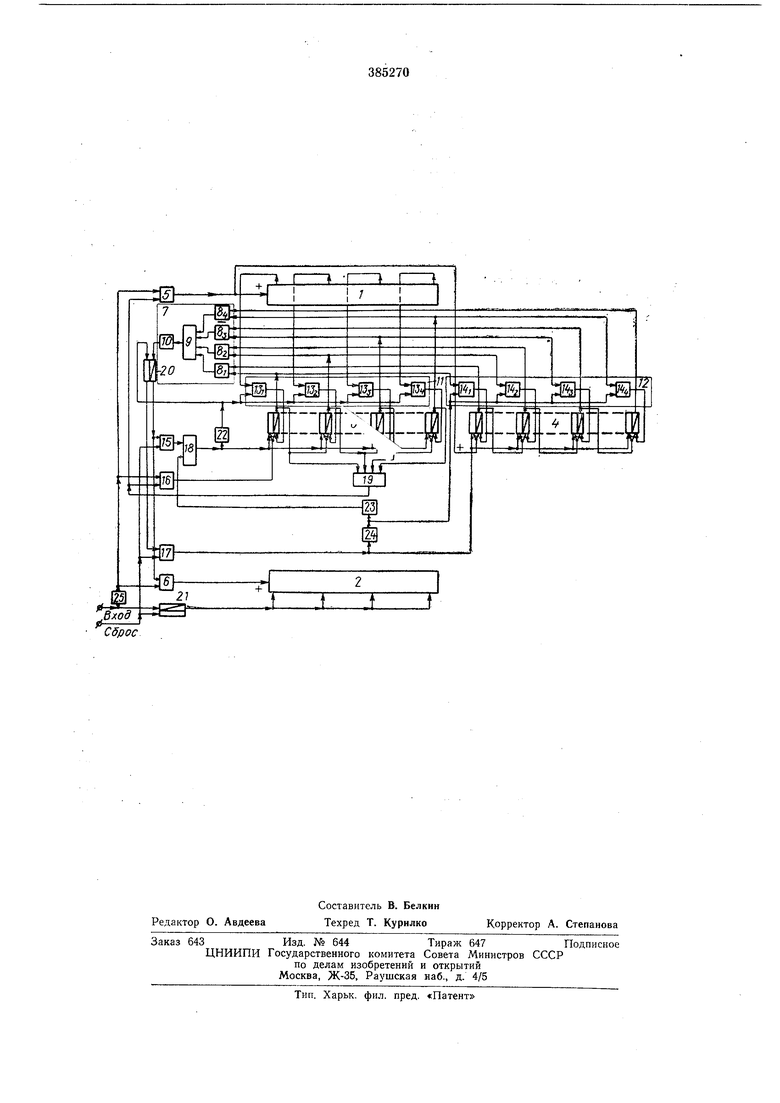

Блок-схема -пред ложе иного цифрового компа.ратора (для чисел не более 15) приведена и а чертеже.

КоМПарато.р содержит регистры /, 2, 3, 4, схемы зап-рета 5-и 6, бЛОЖ сравнения 7, состоящий из двухвходовых схем «неравнозначность 5, §2- 8z, 84, выходы которых через схему «ИЛИ 9 связалы со .входам инвертора 10, блоки переписи 11, 12, состоящие из схем «И /5i, , }3з, 13 л Mt, . }4у, 14 соответственно, схемы «И 15, 16, 17, схемы «ИЛИ

18,19, тр.иггеры 20, 21 -и л.ини.и задержкИ .

Входная шина уст.ройства со входом усталОшш в пулевое состояние триггера 21 (который в-ходом устаиоВКИ в един ичное состояние связан- с ш,и«ой «сброс) « через линию задержки 25 - со входом схем запрета 5 ,и 6, выходы кото-рых сое,дине,ны с суммирующими вхада ми регистров / и 2 соответственно. Ийверсный выход триггера 2/ соединен со входом «сброс регистра 2. Упр.авляющий вхо;д схемы запрета 5 связан с однй.м ,из входов схемы «И J6 и выходом схе.мы «ИЛИ

19,входы которой связаны с выхода-ми регистра 3. Управляющий вход схемы запрета 6 связан с одним .из входов схемы «И 15 и инверсны,м выходом триггера 20, п,ря.мой выход которого связа-н с ОД.Н.И.М из входов схемы «И 17. Другой вход схе.мы «И /7 связа.н с шиной «сброс и другим входо.м схемы «И 15. Выход схемы «И /7 соед.ИИен со входом «сброс регистра 4 п через линии задержки 25 и 24 и схему «ИЛИ IS (другим входом связанную с выходОМ схемы «И 15 - сэ входом «сброс регистра 3, а через линию за.держки 22 - с управЛЯЮЩНм входом блока переп.иси // и входоим установки в нулевое состоян.ие триггера 20. Другие входы блока переписи 11 связаны с выхода.М1И регистра 1, а ВЫХО.ДЫ - со :вхо.да1ми установки в единичное состояние разрядав регистра 3. Выходы регистра 3 связаны с одними из входов схемы блока сравнения 7 (друпие входы которого боединены с выхода1МИ регистра 4) и с одними из входо,в бл.о«а переписи 12. Управляющий вход блока 12 связан с выходом линии задержкл 24, а выходы - со входами установки в единичное состояние разрядов регистра 4. Выход -блока сравн-ей.ия 7 соединен со входом установк:и в единлчн-ое состояние триггера 20.

КоМПа-ратор работает следующи.м образом.

В .исходном состоянии все счетные репистры очищены, т. е. ,их триггеры .находятся в СОСТОЯ.НИ.И, иря .котором отсутствуют сигналы на прямых выходах. Тр.игге.р 20 находится в та-ко.м же состоянии. В результате отсутствуют сигналы ,на одном .из входов схе,.1ы «И 15, на управляющ-ем выходе схемы запрета 6 и есть сигнал .на одном яз входов схемы «И 17.

Поскольку сод€1ржимое -р-егистра 3 равно нулю, отсутстаует сигнал на втором -входе схемы «И 16 .и на упра.вляющем входе схемы

за.1рета 5. Триггер 21 находится в состоянии, при которо.м сигнал на его прямод выходе отсутствует.

Расс.мотр-им случай, когда в регистре / за5 HiHca-HO наибольшее из всех сравненных чисел,

i3 регистре 2 - наи.меньшее, в регистре 4 -

макси.мальная разность, в регистр 3 перезаHifcano наибольшее , т.р.иггерь 20 и 2/

находятся в состая)1иях, соответствующ.нх ис0 ходпо,му.

Расс.мотрИМ работу устройства н.а примере срав.нения пер.вых двух последовательных чисел.

Импульсы очередного сра вниваемого чис5 .ла, поданного на вход компаратора, опрокидывают триггер 21 в единичное состояние, и сигнал с его пря1мого выхода обращает соде)жимое регистра 2 в нуль.

Через линию задержки 25 ,и с,ему за.нрета в им-нульсы очередного числа поступают на вход регистра 2 и подсчитываются в нем. Одновременно ОЛИ проходят через схему «И 16 в регистр 3 и уменьшают его садержи.мое.

Во;зможны три случая.

5 1. Очередное ч-исло .меньше наименьшего из сравнен-ных чи-сел или рав;но ему.

В этом случае после окончания ноступления импульсов данного числа в регистре 2 будет записа.но наи.меньшее ч.исло, а в рег}1стре 3 - максимальная разность.

Имнульс сброса, поданный на шину «сброс после око-нчания поступления .им.нульсов данного числа, перебрасывает триггер 21 в нулевое состояние, пр-оходит через схему э «И 17 я обращает содерж,имое регистра 4 в нуль. Зате.м после прохоледения линии задержки 24 этот же н.мпульс иеренисывает в регистр 4 содерл и.мое регистра 3, т. е. максимальную разность. В этот .момент триггер 0 20 перебрасывается в единичное состояние. Далее и.мпульс сброса через линию задержки 23 Н схему «ИЛИ }8 обр ащает содержи.мое .регистра 3 в нуль, после чего через линию задержки 22 возв-ращает триггер 20 в нулевое состояние и переписывает в регистр 3 содержи.мое регистра /. На этом процесс заканчивается, а схе.ма готова к ириему следующего числа.

2. Очередное число больше на.именьшего из сравненных чисел, но .меньше ил.и р-авно наибольше.му числу.

В этО|М случае .в момент, когда количество И(Мпульсов данного числа, подсчитанное в регистре 2, оказалось равны.м .их количеству в

наи.меньшем числе, содерж.имое оооих регистров . и 4 становится оди.наковы.м. В результате на выходе блока сравнения 7 .появляется сигнал, перебрасывающий триггер 20 в еди Ичнoe состояние. Появляется сигнал на уп0 равляюще.м входе схемы запрета 6, благодаря чему все остальное импульсы .данного числа не поступают в регистр 2. Все .последующие .и.миульсы поступают на вход регистра 3, состоян.ие других элементов с.хемы при это.м не

из.меняете я.

После окончания постунления импульсов данного числа на шииу «сброс нодается импульс, который обращает содержимое регистра 5 в нуль, ,и неребрасывает триггер 20 в .нулевое состояние, а в регистр 3 иеренисывает содержимое регистра /.

3. Очеред)1ое число больше няибольшего .из сравненных чисел.

3 даш-ю.м случае в момент, когда количество поступивших в схему Ямпульсов этого числа станет равным их количеству в наибольшем, занисанлом в регистре 1, содерж.нмое регистра 3 обращается в .нуль. В результате иоступлен.ие сигналов на вход регистра 3 прекращается .и начинается ,их сум мирова,н,ие с содерЖИмым регистро.в / и 4. Переключения в схеме, вызываемые имнульсом сброса, те же, что в предыдущем случае.

Расс.мотр.им теперь начало работы компаратора. Исходные состояния его элементов описаны.

Имнульсы первого из сравнивае;мых чисел, поданного на вход компаратора, опрокидывают триггер 21 в единичиое состояние, и сиглал с его единичного выхода нодтверждает очищенное состояние регистра 2. Через линию задернски 25 .и схему 6 импульсы нервого числа поступают в регистр 2, через схему 5 - в .регистры 1 п 4.

После окончания поступления имнульсов первого числа на шину «сброс подается импульс. Переключение элементов компаратора при этом такое же, как при первом из трех рассмотренных случаев. В результате в регистрах 1 а 2 записано первое число, в регистре 4 - нуль.

При поступлении на вход компарато.ра второго ч.исла могут быть два случая:

1.Второе число меньше первого или равно ему.

Ра,бота схемы в это.м случае аналогична описанной для первого из расс.мотренных трех случаев.

2..Второе число больше .первого.

Работа схемы аналогична описаиной для третьего из рассмотренных ранее случаев.

Предмет 1И з о б р е т е н и я

Цифровой компаратор, содержащий лвя регистра, суммирующие входы которых через две схемы запрета связаны со вход)юй шиной, бло.к сразднения, входы схем « черавнозначиость которого связаны с прямым.н вы.ходаМИ одноименных разрядов регистров, а выходы через схему «ИЛИ связа.н.ы со входом

.инвертора, два блока переписи, одни из входов с.хем «И которых связаны с прямы.ми выходами одного регистра, причем другие входы схем «И через линию задержки связаны со входо.м «сброс другого регистра,

ВХО.ДЫ устаиойки в единичное состояние которого соединены с выхода.ми схе.м «И, логические с.хемы, линии задержки и триггеры, отличающийся тем, что, с целью расширения функциональных возможностей устройства, в

него введены третий и четвертый регистры, выходы которых связаны со .входами блока сравнения, приче.м выходы третьего регистра свя.зань со входа ми блока переписи, выходы iKOTOporo соединены со входами установки в

единичное состояние второго регистра, и через схе.му «ИЛИ - с управляющил входо. схе.мы запрета нервого регистра .и одни.м из входов схемы «И, .другой вход которой связан со входной шиной устройства, а выход-

с вычитающим входо.м третьего регистра, вы.ходы третьего регистра соединены с выходами второго блока переписи, входы которого связаны с выхо.дами первого регистра, вы.ход блока сравнен.ия связан со входом установки в

единичное состояние триггера, вход установки в }1улевое состояние которого соединен с лправля-ющ.им входом второго блока переписи, причем .инверсный выход триггера через схему «И, связанную с шиной «сброс, и схему «ИЛИ, связанную через линию задержк1Г с управляющим входо-м нервого блока нереписи, сое.динен со входоМ «сброс третьего регистра и с управляющи.м входО:М схемы заирета второго регистра, а пря.мой выход трлггера через схему «И, связанную с шиной «сброс, соединен со входо.м «сброс четвертого регистра; выходы нервого регистра св.язаны с вы.ходнЫМи шинами наибольшего числа, ВЫХО.ДЫ второго регистра - с шина.ми наи.меньшего ч.исла, а четвертого - с шинами м а кси м а льн о и раз н ос т.и.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки массивов чисел | 1984 |

|

SU1403059A1 |

| Устройство для упорядочивания чисел | 1984 |

|

SU1241228A1 |

| Измеритель предельных значений временных интервалов | 1975 |

|

SU602911A1 |

| УСТРОЙСТВО для ОКРУГЛЕНИЯ ЧИСЕЛ^0-СОЮгн.:^Я IП''Т'''^'.'«-' - *'>&''•'.1.-...п1;--,:.лл^-;. ц.^/{, &!'1Б/'НО",1кЛ I | 1973 |

|

SU367420A1 |

| Устройство для преобразования серий импульсов во временные интервалы | 1976 |

|

SU653742A1 |

| Генератор псевдослучайных чисел | 1986 |

|

SU1324091A1 |

| Устройство для сортировки чисел | 1986 |

|

SU1315968A1 |

| УСТРОЙСТВО для ПОСТРОЕНИЯ КОРНЕВЫХ ГОДОГРАФОВ СИСТЕМ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 1973 |

|

SU397914A1 |

| Устройство для измерения амплитуды импульсных сигналов | 1984 |

|

SU1223154A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU451078A1 |

Авторы

Даты

1973-01-01—Публикация