1

Изобретение относится к измерительной технике и может быть использовано для определения амплитудного значения последовательности повторяющихся импульсных сигналов в широ- ком диапазоне частот их следования. Цель изобретения - повьппение надежности за счет упрощения устройства.

Поставленная цель достигается вве дением синхронизации каждого такта кодирования текущим сигналом входной последовательности импульсов. При этом каждый такт кодирования синхронизован только с одним из сигналов измеряемой последовательности, а остальные сигналы в интервале времени между соседними тактами кодирования влияния на работу устройства не оказывают. Аппаратурная надеж- ность устройства возрастает благодаря уменьшению числа функциональных элементов. Одновременно возрастает информацис нная надежность.

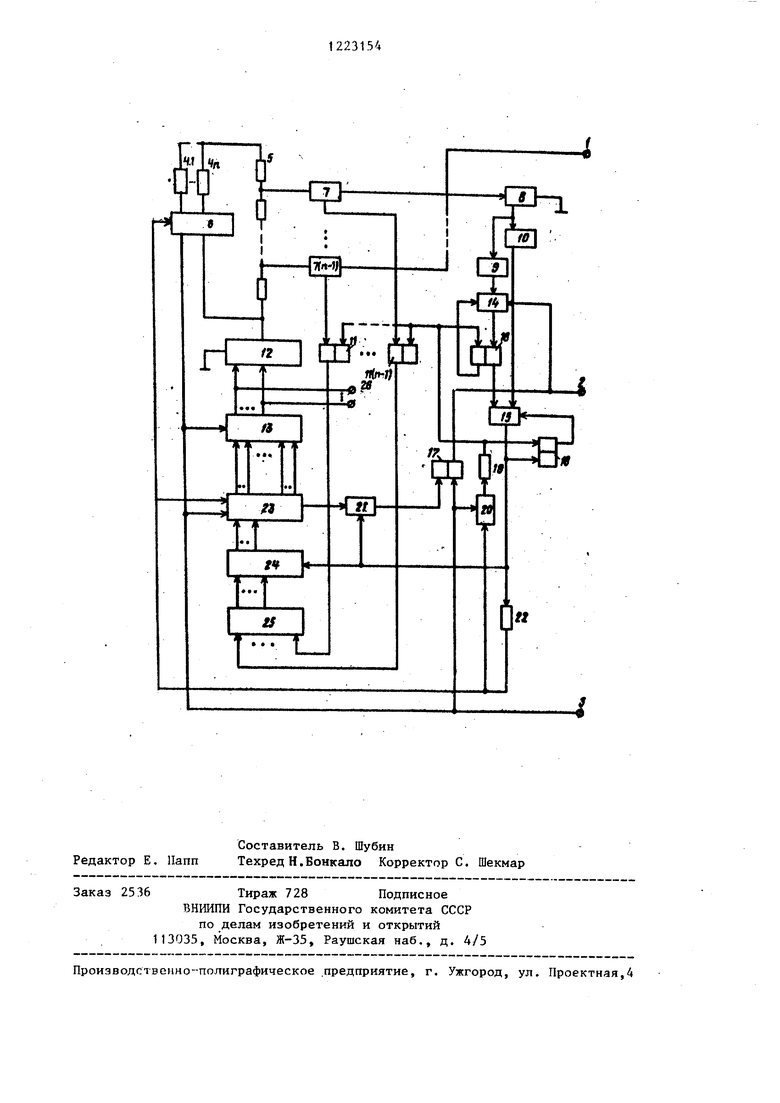

На чертеже представлена структурная схема устройства.

Устройство содержит измерительный вход 1 i выход 2 сигнала конца измерения; вход 3 сигнала запуска; источники 4.1,...,4.п опорного напря- жения от старшего до предпоследнего младшего разрядов соответственно-, резистивный делитель 5; коммутатор 6; измерительные компараторы 7.1- 7(п-1)-, компаратор 8; первый 9 и второй 10 формирователи импульсовi триггеры 11.1-11(п-1) памяти, циф- роаналоговый преобразователь (ЦАП) 12J регистр 13 кода; первый 14 и второй 15 элементы И, первый 16, второй 17 и третий 18 триггеры , первый элемент 19 временной задержки; элемент ИЛИ 20; третий элемент И 21-, .второй элемент 22 временной задержки распределитель 23 кода; блок 24 ключей переписиJ дешифратор 25 кода; первые выходы 26 устройства.

При этом вход 1 устройства соединен с первыми входами измерительных компараторов 7.1-7(п-1) и 8, вторые входы компараторов 7 соединены с выходами делителя 5. Выходы компараторов 7 через триггеры 11.1-11(п-1) памяти соединены с дешифратором 25 кода, выходы которого через блок 24 ключей переписи и распределитель 23 кода соединены с входами регистра 13 кода, выходы которого соединены с

5

5

31

0

30 5 40 45

50 55

54

первыми выходами 26 устройства и входами ЦАП 12. Первый выход ЦАП 12 соединен с выводом резистивного делителя 5 и входом коммутатора 6,второй выход ЦАП 12 соединен с общей шиной питания, так же как и второй вход компаратора 8. Выход компаратора 8 подключен к входам двух формирователей 9 и 10 импульсов. Выход формирователя 9 через последовательно включенные первый элемент И 14, первый триггер 16 подключен к первому входу элемента И 15, второй вход которого соединен с выходом формирователя 10. Выход элемента И 15 соединен с R-входом триггера 18, блоком 24 ключей переписи, входом третьего элемента И 21 и через элемент 22 временной задержки соединен с элементом ИЛИ 20, входами управления распределителя 23 кода и коммутатора 6.

Второй вход элемента ИЛИ 20, управляющие входы распределителя 23 кода, коммутатора 6 и регистра 13 кода соединены с входом 3 устройства. распределителя 23 кода через второй вход элемента И 21 соединен с первым входом триггера 17, второй вход которого соединен с вторым входом элемента ИЛИ 20.Выход элемента ИЛИ 20 через элемент 19 временной задержки соединен с S-вхо- дами триггеров 16-18, при этом выход триггера 18 соединен с третьим входом элемента И 15. Выход триггера 17 соединен с вторым входом элемента И 14 и выходом 2 устройства,а третий вход элемента И 14 соединен с вторым выходом триггера 16. Вход резисторного делителя 5 соединен с первыми выходами источников 4 опорного напряжения, вторые выходы которых соединены соответственно с входами коммутатора 6.

Устройство работает следующим образом.

По сигналу внешнего запуска,поступившему на вход 2, устройство вначале переключается в исходное состояние, после чего автоматически начинается измерение (кодирование) амплитуды ч;игналов импульсной последовательности, поступающей на измерительный вход 1. В исходном состоянии коммутатор 6 подключает параллельно делителю 5 источник 4.1 опорного напряжения старшего разряда, регистр 13 кода сбрасывается в нуле3

вое состояние и напряжение на выходе ЦАП 12 становится нулевым, триггер 17 переключается в единичное состояние, распределитель 23 подключает блок 24 ключей переписи к входам старшего разряда регистра 13, элемент И 21 блокирован нулевым сигналом на выходе регистра 13. Сигнал запуска передается через элемент ИЛИ 20 и с задержкой в элементе 19, необходимой для переключения устройства в исходное состояние, переключает в нулевое состояние триггеры 11 памяти, а триггеры 16 и 18 переключает в положения, при которых деблокируется элемент И 14 и блокируется (триггером 16) элемент И 15.

На. выходах (ступенях) резистив- ного делителя 5 подключенным источником опорного напряжения образуются уровни квантования с постоянным шагом приращения. Делитель 5 с компараторами 7 образует аналого-цифровой преобразователь считывания с поразрядным определением кода. Если используется десятичное кодирование, то делитель 5 является однодекадным, а количество компараторов равно девяти. Опорное напряжение источника 4.1 старшего разряда равно при этом пределу измеряемой величины 10 , где п - число разрядов кода. Остальные опорные напряжения эквивалентны единице соответствующего разряда кода.

В исходном состоянии на ступенях делителя образуются уровни с шагом, эквивалентным единице старшего разряда кода, в рассматриваемом случае С переключением в нулевое состояние триггеров 11 памяти они оказываются подготовленньми к записи единичных сигналов измерительных компараторов 7. С появлением сигнала измеряемой импульсной последователь- ности на входах компараторов 7 он сравнивается с опорными уровнями делителя 5. По мере его нарастания до амплитудного значения на выходах соответствующих компараторов 7 появляются единичные сигналы, которые запоминаются подключенными к ним триггерами 11. Число сработавших компараторов равно значению определяемого разряда кода.

В компараторе 8 измеряемый сигнал сравнивается с нулевым (или np.-i- нятым за нулевой) уровнем. С нарастанием измеряемого сигнала компаратор 8 переключается, например, из

23154

нулевого в единичное состояние. Из переднего фронта выходного сигнала компаратора формирователем 9 формируется импульс, которым переключа- 5 ется триггер 16. При переключении этого триггера блокируется элемент И 14 и деблокируется элемент И 15.

При уменьшении измеряемого сигнала до нулевого уровня компаратора 8

10 сигнал на выходе этого компаратора измеряется с единичного на нулевой. Из фронта спада сигнала этого компаратора в формирователе 10 формируется соответствующий импульс, ко)5 торый передается через элемент И 15 в блок 24 ключей переписи кода и одновременно переключает триггер 18, чем блокируется элемент И 16.

По импульсу, появившемуся на вы20 ходе элемента И 15, через подготовленные цепи распределителя 23 в регистр 13 переписывается код,представленный сигналами измерительных компараторов. Этот единичный код

25 соответствующего разряда преобразуется предварительно дешифратором 25 в разряд соответствующего двоичного кода, в рассматриваемом случае двоично-десятичного кода. Такое пре2Q образование кода необходимо для упрощения суммирования в регистре 13 кодов различных разрядов и суммирования тем самым выходных напряжений. ЦАП. Суммирование двоично-позиционных кодов сводится к суммированию позиций отдельных разрядов, в то время как суммирование двоичных кодов требует применения арифметического устройства с суммированием и переносом сигналов отдельных раз- рядов.

При записи кода в регистр 13 напряжение на выходе ЦАП 12 становится эквивалентным сумме соответствующих разрядов кода.

ЦАП является также двоично-десятичным, преобразует в напряжение только п-1 старших разрядов кода и поэтому содержит п-1 разрядов, а в регистр 13 записываются все разряды

50 кода. Дешифратор 25 является двоичным, имеет четыре выхода. Столько же ключей содержится и в блоке 24.

В первом, после исходного (нулевого) состояния, такте кодирования

55 напряжение ЦАП становится эквивалентным старшему разряду кода.

С задержкой во времени в элементе 22, необходимой для записи теку35

40

45

щего разряда кода в регистр 13, выходной сигнал элемента И 15 переключает распределитель 23, подготавли- вая его для передачи кода второго разряда во втором такте кодирования, и одновременно переключает коммутатор 6, который отключает источник старшего п-го разряда и параллельно делителю 5 подключает источник вто- рого (n-l)-ro старшего разряда.

При указанных переключениях в первом такте на ступенях делителя 5 устанавливаются уровни напряжения с шагом, эквивалентным единице второ- го старшего разряда ко да, смещенные на величину напряжения ЦАП, эквивалентного сформированному в первом такте старшему разряду кода.

С задержкой во времени в элемен- те 19, необходимой для установления новых уровней напряжения на ступенях делителя 5, выходной сигнал элемента 22 переключает триггеры 11,16 и 18 в исходное состояние и начина- ется второй такт кодирования - определения .второго разряда кода.

Сброс триггеров 11.1-11 (п-1) в нулевое состояние относительно появления измеряемого сигнала на входе

Iи на входах компараторов 7.17(п-1) происходит в случайный момент времени. Если сброс ЦАП 12 происходит во время нарастания измеряемого сигнала то в триггеры 11-11(п-1) записываются сигналы компараторов 7, соответствующие амплитуде измеряемого сигнала. Если же сброс триггеров

IIи триггеров 16 и 18 происходит

во время спада измеряемого сигнала, то компараторы 8 фиксируют только часть этого сигнала и в триггеры 11 записывается код, соответствукщий какому-то мгновенному, не амплитудному значению измеряемой величины. Однако в этом случае при уменьшении измеряемого сигнала в деблокированном элементе И 14 формирователь 9 не формирует импульса. Поэтому, хотя из фронта спада измеряемого сигнала формирователь 10 и формирует соответствующий импульс, но этот импульс не проходит через блокированный элемент И 15 в блок 24 ключей переписи кода. В этом случае следующий импуль считывания формируется только с поступлением на вход 1 очередного сигнала измеряемой последовательности, чем достигается определение и запись в триггеры 11 текущего разряда кода амплитудного значения этого сигнала. Записанное перед этим в триггеры 11 число, соответствующее не амплитудному значению сигнала, сбрасывать не нужно, так как оно является частью амплитудного значения сигнала и дополняется при его определении.

Таким образом, если сброс триггеров 11 происходит во время уменьшения измеряемого сигнала, то благодаря описанной синхронизации каждый текущий такт кодирования всегда начинается только с нарастанием одного очередного измеряемого сигнала, чем исключаются ошибки в определении разрядов кода. Вместе с тем во время каждого такта кодирования воздейст-, вие на устройство остальных сигналов последовательности исключается.

В предпоследнем такте кодирования, после записи в регистр (n-l)-ro предпоследнего младшего разряда кода и переключения распределителя 23 в последнее положение Для передачи в регистр 13 младшего разряда кода, на выходе распределителя и соответственно на входе элемента И 21 появляется единичный сигнал.

К началу п-го последнего такта кодирования на ступенях делителя 5 устанавливаются уровни квантования с шагом, эквивалентным единице младшего разряда кода, а напряжение ЦАП эквивалентно при этом сумме п-1 старших разрядов кода. В п-м такте кодирования импульс,поступивший в блок 24 ключей для переписи кода младшего разряда передается также через деблокированный элемент И 21 и переключает триггер 17. С указанным переключением триггера 17 блокируется элемент И 14 и измерение амплитуды последовательности входных сигналов завершается. Конец измерения отображается появлением единичного сигнала на выходе 2 устройства. По этому сигналу с выходов 26 t ожет быть считан из регистра 13 во внешнее устройство памяти или отображения код - цифровой эквивалент измеренной амплитуды.

Новый цикл измерения выполняется с поступлением очередного сигнала запуска на вход 3.

71223154

а изобретения

1вв дв ме ст

Устройство для измерения амплитуды импульсных сигналов, содержаще триггер, два элемента временной задержки, резистивный делитель, один вывод которого соединен с одними из полюсов источников опорного напряжения от старшего до младшего предпоследнего разрядов, другие полюса которых подключены к выходам коммутатора, аналоговым входом параллельно с другим выводом резистивного делителя, соединенного с выходом цифро аналогового преобразователя,входы которого соединены с выходами регистра кода, входами подключенного к распределителю кода, к входам которого подсоединены выходы блока ключей переписи, входами соединенного через дешифратор кода с выходами триггеров памяти, вход каждого из которых подключен к выходу соответствующего измерительного компаратора, опорным входом соединенного с соответствующей ступенью резистивного делителя, а измерительный вход каждого из измерительных компараторов и компаратора, опорным входом соединенного с общей шиной, подключен к измерительному входу устройства, с входом сигнала запуска которого со.е- динены входы сброса коммутатора, распределителя кода, регистра кода, выходы которого подсоединены также к кодовому выходу устройства, о т- личающееся тем, что, с целью повышения его надежности за счет упрощения устройства, в него

8

1введены два формирователя импульсов, два триггера, элемент ИЛИ и три эле-, мента И, первый из которых соответствующими входами соединен с выходом

Первого формирователя импульсов,одним из выходов первого триггера и выходом второго триггера, подключенным к выходу сигнала конца измерения устройства, выход первого элемента И соединен с одним из входов первого триггера, другой вход которого подсоединен к первому входу третьего триггера, и входом сброса триггеров памяти, а через первый элемент временной задержки подсоединен к выходу элемента ИЛИ, один из входов которого соединен с первым входом второго триггера и входом сигнала запуска устройства, а другой вход параллель

но с входами запуска коммутатора и

распределителя кода через второй элемент временной задержки подключен к параллельно соединенным выходу второго элемента И, второму входу

третьего триггера, входу сигнала переписи блока ключей переписи и одному из входов третьего элемента И, вторым входом подключенного к соответствующему выходу распределителя

кода, а выходом - к второму входу второго триггера, соответствующие входы второго элемента И соединены с вторым выходом первого триггера, выходом третьего триггера и выходом второго формирователя импульсов, вход которого параллельно с входом первого формирователя импульсов подсоединен к выходу компа- ipaTOpa,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для измерения амплитуды одиночных импульсных сигналов | 1982 |

|

SU1112301A1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU993468A1 |

| Устройство для определения максимальной гармоники спектра Уолша | 1984 |

|

SU1211751A1 |

| Устройство для измерения максимального значения сигналов | 1977 |

|

SU739424A1 |

| Преобразователь напряжения в код | 1977 |

|

SU728222A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО СРАВНЕНИЯ | 1991 |

|

RU2020749C1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Аналого-цифровой преобразователь последовательного уравновешивания | 1981 |

|

SU1030965A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1480127A1 |

Изобретение относится к измерительной технике. Может быть использовано для определения амплитудного значения последовательности повто ряющихся импульсных сигналов в широком диапазоне частот их следования. Целью изобретения является повышение надежности и упрощение устройства. Поставленная цель достигается путем синхронизации каждого такта кодирования текущим сигналом входной последовательности импульсов. При этом кая;цый такт кодирования синхронизирован только с одним из сигналов измеряемой последовательности. Остальные сигналы в интервале времени между соседними тактами кодирования влияния на работу устройства не оказывают. Информационная и аппаратурная надежность устройства увеличена в результате уменьшения числа схемных элементов и сокращения между ними функциональных связей. 1 ил. г

| Грязное М.И., Гуревич М.Л | |||

| и Маграчев З.В | |||

| Измерение импульсных напряжений | |||

| - М.: Советское радио, 1969 | |||

| Устройство для измерения амплитуды одиночных импульсных сигналов | 1982 |

|

SU1112301A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-04-07—Публикация

1984-07-09—Подача