1

Изобретение относится к области вьйнслйтельной техники и может быть использовано в аналоговых счетно-решающих устройствах, моделирующих математические уравнения,

Известны емкостные аналоговые запоминающие устройства, содержащие узел сравнения, формирователь управляющих импульсов и узел запоминания и воспроизведения.

Однако такие устройства не обеспечивают высокой точности воспроизведения запомненных величин.

В предлагаемое устройство введены инверториый каскад на транзисторе с коллекторным, базовым и. эмиттерным резисторами и дв:а диода, один из кото.рых катодом подключен к базе транзистора, другой анодом к его эмиттеру, причем свободные электроды диодов объединены между собой и подключены к выходу узла сравнения, а через дополнительный резистор к шине нулевого потенциала, а коллектор транзистора инверторного каскада соединен с входом формирователя управляющих импульсов.

Это позволяет повысить точно,сть воспроизведения.

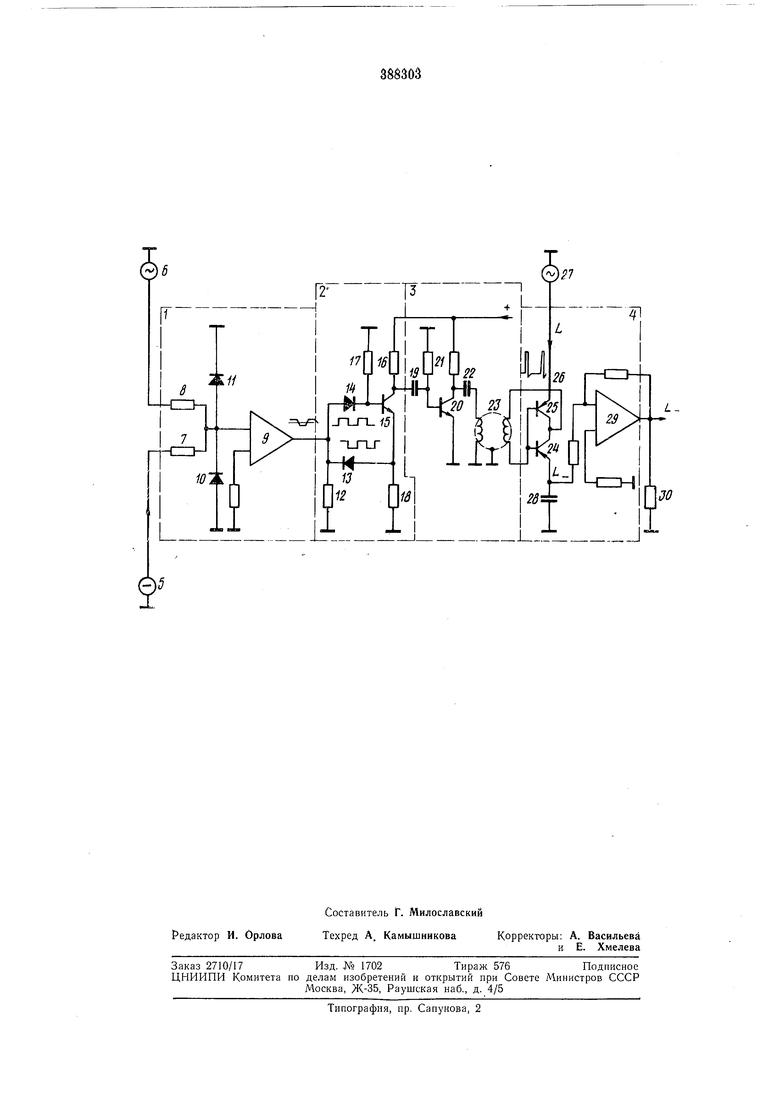

Принципиальная электрическая схема предлагаемого емкостного аналогового запоминающего устройства приведена на чертеже.

Устройство состоит из узла / сравнения, инверторного каскада 2 с двумя диодами.

формирователя 3 управляющих импульсов и узла 4 запоминания и воспроизведения.

Один из входов узла сравнения подключен к датчику 5 напряжения , второй вход соединен с источником 6 информации, генерирующим изменяющееся во времени напряжение и. Резисторы 7 и 5 узла сравнения подключены к входу трала-исторного дифференциаль ного усилителя Р, Для защиты от перегрузки

вход усилителя 9 шунтирован ограничитель ными диодами 10 и //.

Выход узла сравнения соединен с 1зх6доМ инверторного каскада 2. Инверторный каскад об,рйзобан резистором

12, днодами 13 и 14 на входе, транзистором 15, коллекторным, эмиттерным и базойЫм резисторами 16, 17 и. 18,

Выход усилителя 9 через диоды 13 и 14, обеспечивающие прохождение напряжения в

положительном и отрицательном полупериодах, соединен соответственно с базой и эмиттером транзистора 15 инверторного каскада. Коллектор транзистора 15 через раздели.тельный конденсатор 19 соединен с базой

транзистора 20 формирователя управляющих сигналов. Разделительный конденсатор 19 и резистор 21 образуют дифференцирующую цепо,чку. Коллектор транзистора 20 через разделительный конденсатор 22 соединен с первичной обмоткой имтульсного трансформатоpa 23. Вторичная обмотка трансформатора 23 подключена к входу узла 4 запоминания и воспроизведения и соединена с базами и коллекторами транзисторов 24 и 25 транзисторного ключа 26. Вход ключа 26 соединен с источником 27 информации, генерирующим напряжение V, текущее значение L которого подлежит запоминанию и воспроизведению. К выходу ключа 26 подключен запоминающий конденсатор 28, на который подается напряжение L. Конденсатор 28 подключен к входу развязывающего усилителя 29, включенного по схеме повторителя, воспроизводящего на подключенной к его выходу нагрузке 30 запомненную величину напряжения L. Вел.ичины и и V являются взаимосвязанными, изменяющимися во времени напряжениями. Величина Е представлена напряжением, которое также может изменяться во времени, однако при этом скорость изменения величин и и V должна превышать скорость изменения величины Е настолько, чтобы за цикл изменения величин f/ и У изменением Е можно было пренебречь. Пусть Е - неизменная во времени величина напряжения, а величины U и V функционально связанные между собой, (U), переменные напряжения. Лр.и этом величина L есть мгновенное значение иа-пряжения V, запомненное при совпадении мпновенного значения напряжения U с напряжением Е. Напряжение L запоминается и воспроизводится в виде постоянного напрЯ|Жения в течение всего, цикла изменения величины U. Сравнение мгновенного значения напрял ения и с напряжением Е происходит на резисторах 7 и S, разностное напряжение поступает на вход усилителя 9. При равенстве мгновенного значения напряжения и и напряжения Е напряжение на входе усилителя 9 равно нулю. Напряжение на входе усилителя 9 ограничивается диодами 10 и //, и поэтому напряжение на выходе усилителя 9 представляет переменное наиряжение траиециедалыной (почти прямоугольной) формы, изменяющееся синфазно и с той же цикличностью, что и напряжение V. При разности между напряжением Е и мгновенным значением напряжения U, равной нулю, происходит изменение полярности трапециедального напряжения на выходе усилителя 9. С выхода усилителя 9 траиецнедалыное напряжение поступает на вход инверторного каскада с двумя диодами. Через диод 14 в -положительный полупериод напряжение прикладывается к базе, а через диод 13 в отрицательный полупериод к эмиттеру транзистора 15. Положительное напряжение, поступающее к базе транзистора 15, инвертируется, а отрицательное напряжение, приложенное к эмиттеру того же транзистора, проходит, не претерпевая инверсии, и на коллекторе о,бразуется однополярное напряжение, которое представляет со:бой сумму постоянного напряжения и импульсного напряжения переходного процесса, возникающего при переходе от одного полупериода к другому при совпадении мгновенного значения напряжения с компенсирующим его напряжением . Из этого импульсного напряжения путем дифференцирования и ограничения отрицательной полярности формируются импульсы, управляющие ключюм 26. Формирование управляющих импульсов происходит следующим образом. С коллектора траизистора 15 через разделительный конденсатор 19 напряжение, продифференцированное цепочкой 19, 21, в виде двуполярных импульсов подается на базу транзистора 20 формирователя управляющих импульсов. Транзистор 20 отсекает отрицательные импульсы и усиливает положительные, которые с коллектора через разделительный конденсатор 22 поступают на первичную обмотку И1Мпульсного трансформатора 23. Импульсное напряжение вторичной об.мотки трансформатора 23 используется как управляющее и прикладывается между базами и коллекторами транзисторного ключа 26. При наличии управляющего импульса ключ 26 находится в открытом СОСТОЯНИЕ и подключает запоминающий конденсатор 28 к .источнику информации (напряжение V, мгновенное значение которого подлежит запо.минанию). Конденсатор 28 за один или несколько импульсов заряжается до величины L; так как при. прекращении воздействия управляющего импульса ключ 26 запирается, величина L сохраняется на конденсаторе 28 в виде постоянного напряжения. Напряжение L с конденсатора 28 снимают через развязывающий усилитель 29. Предмет изобретения Емкостное аналоговое запоминающее уст ройство, содержащее узел сравнения и формирователь управляющих импульсов, соединенный с узлом запоминания и воспроизведения, отличающееся тем, что с целью повыщения точности, в него введен инверторный каскад на транзисторе с коллекторным, базо вым и эмиттерньш резисторами и два диода, один из которых катодом подключен к базе транзистора, другой анодом к его эмиттеру, причем свободные электроды диодов объединены .между собой и подключены к выходу узла сравнения, а через дополнительный резистор к шине нулевого потенциала, а коллектор транзистора инверторного каскада соединен с выходом .формирователя управляющих и.мпульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регулирования температуры | 1982 |

|

SU1024891A1 |

| Устройство для импульсно-фазового управления трехфазным тиристорным преобразователем | 1987 |

|

SU1631682A1 |

| Устройство время-импульсной модуляции | 1974 |

|

SU507925A2 |

| Устройство для регулирования температуры | 1988 |

|

SU1594503A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU822295A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU780048A1 |

| Преобразователь напряжения | 1981 |

|

SU997209A1 |

| Полупроводниковый выключатель | 1979 |

|

SU873413A1 |

| Двухтактный усилитель | 1985 |

|

SU1337998A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

Авторы

Даты

1973-01-01—Публикация