1

Изобретение относится к области вычислительной техники и в частности, может быть применено в аналоговых вычислительных машинах, работающих в системе остаточных классов.

Известно аналоговое устройство для решения дифференциального уравнения первого порядка в позиционной системе счисления. Оно представляет собой интегратор, выход которого через инвертор соединен со входом. Однако точность и диапазон решения с помощью такого устройства малы.

Одним из способов повышения точности и расширения диапазона решения является решение дифференциального уравнения в системе остаточных классов.

Таким образом целью изобретения является создание устройства для решения дифференциального уравнения первого порядка в системе остаточных классов.

Это достигается путем включения в схему интегрирования ключевых элементов для преобразования решаемой переменной из позиционной системы счисления в систему остаточных классов.

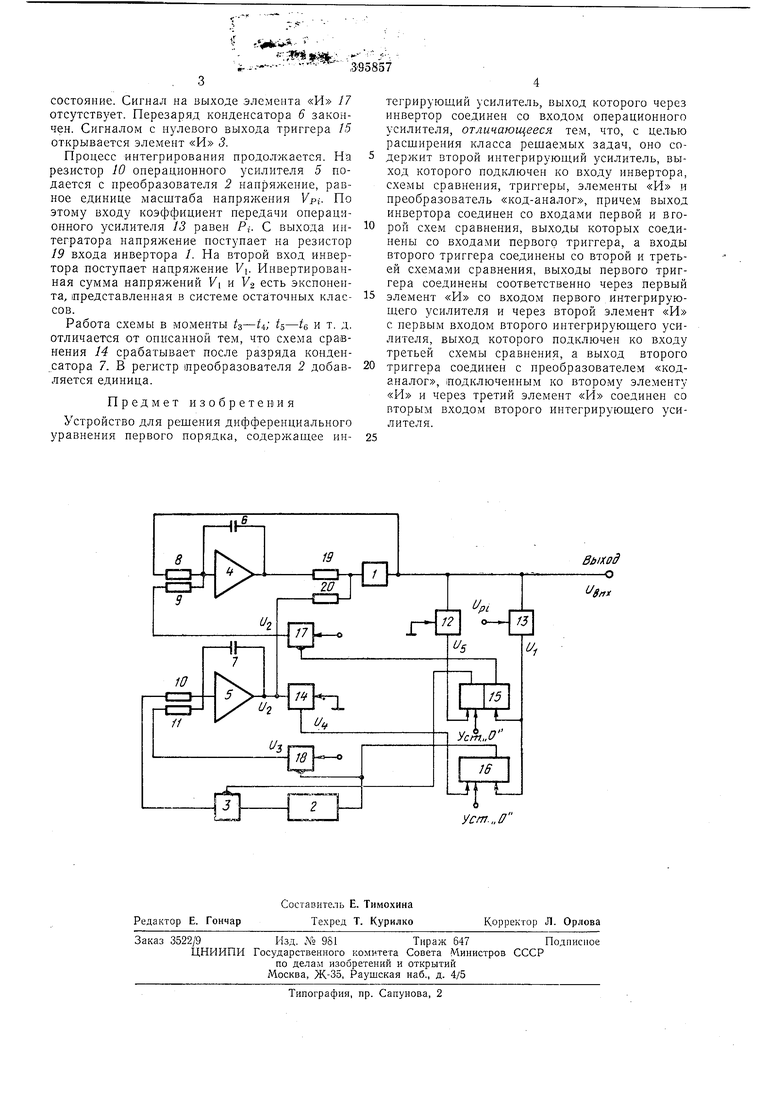

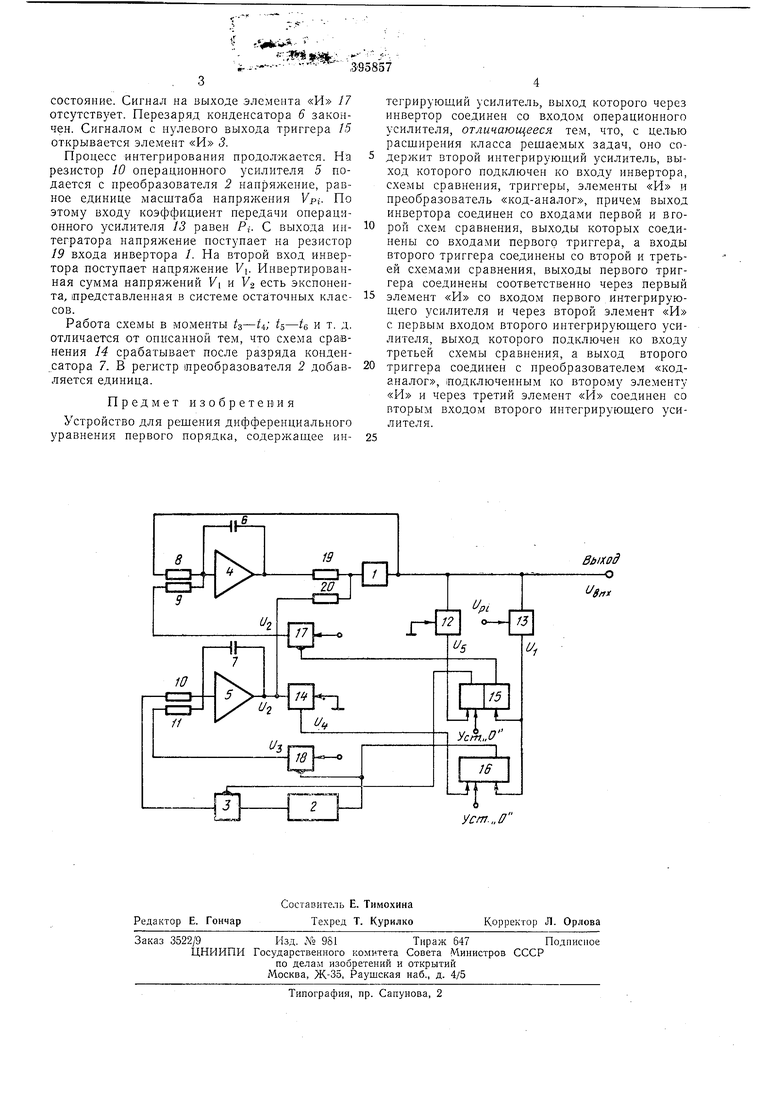

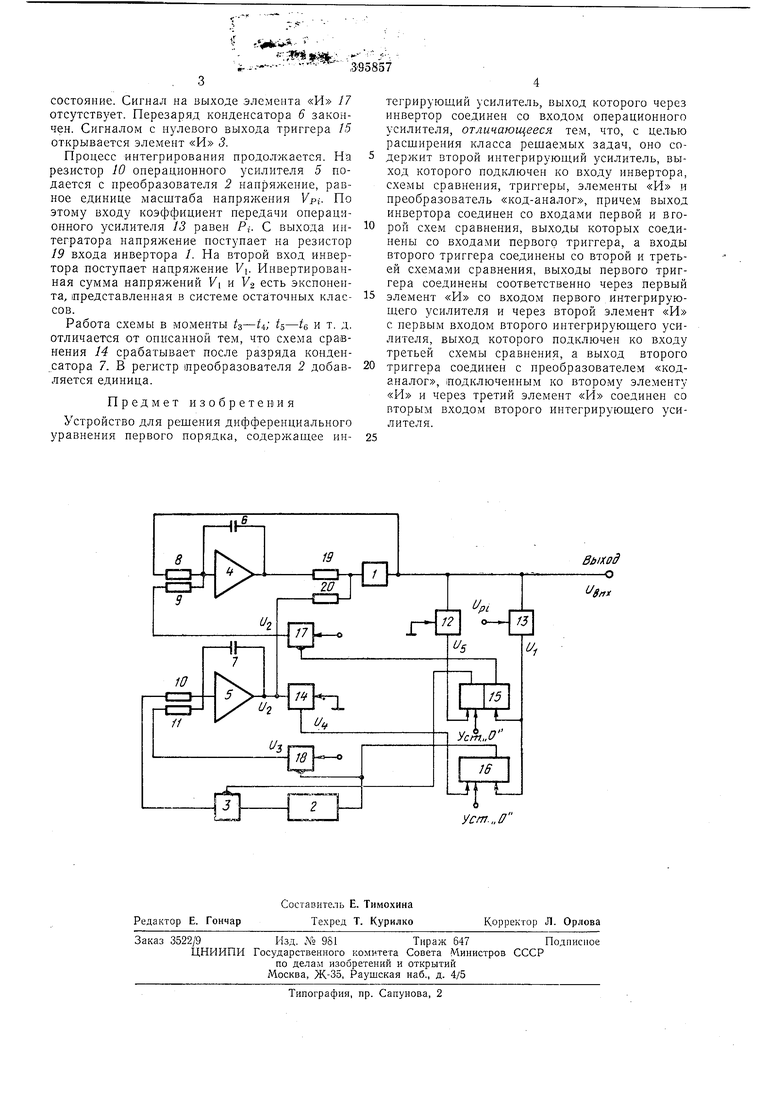

На чертеже изображена функциональная схема устройства.

Устройство состоит из инвертора 1, преобразователя код-аналог последовательного типа 2 и элемента «И 3, операционных усилителей 4 и 5 с кондеисаторами обратной связи соответственно 6 и 7, резисторов входа 8, 9 и 10, 11, схем сравнения 12, 13 и 14, триггеров 15 и 16, элементов «И 17 и 18.

Инвертор / представляет собой инвертирующий операционный усилитель со входными резисторами 19 и 20, имеющий коэффициент передачи, равный единице.

В момент времени /i величина выходного напряжения достигает значения Vpi. Срабатывает схема сравнения 13, с выхода которой импульс У подается на единичные входы триггеров 15 и 16.

Потенциальные единичные выходы триггеров открывают элементы «И 17 и 18, в результате чего на входные резисторы 9 и 11, имеющие малый коэффициент передачи, подаются напряжения сброса Уо и УЗ. Так как конденсатор обратной связи 7 операционного усилителя 5 разряжен до нуля, схема сравнения 14 вырабатывает напряжение , возвращающее триггер 16 в исходное состояние. На выходе элемента «И /5 сигнал отсутствует. Перезарядка конденсатора 7 не происходит. Напряжением Va происходит разряд кондеисатора 6. В регистр преобразователя 2 «код-аналог последовательного типа заносит ся единица.

В времени /2 напряжение на выходе устройства становится равным нулю. Срабатывает схема сравнения 12, импульс Vs с выхода которой возвращает триггер 15 в исходное

....ii.состояние. Сигнал на выходе элемента «И /7 отсутствует. Перезаряд конденсатора 6 закончен. Сигналом с нулевого выхода триггера /5 открывается элемент «И 3. Процесс интегрирования продолжается. На резистор 10 онерационного усилителя 5 подается с преобразователя 2 напряжение, равное единице масштаба напряжения KPJ. По этому входу коэффициент передачи операционного усилителя 13 равен Р,- С выхода интегратора напряжение поступает на резистор 19 входа инвертора /. На второй вход инвертора поступает напряжение V. Инвертированная сумма напряжений V и V-2 есть экспонента представленная в системе остаточных классов. Работа схемы в моменты з-U; U-U и т. д. отличается от описанной тем, что схема сравнения 14 срабатывает после разряда кондеп.сатора 7. В регистр (Преобразователя 2 добавляется единица. Предмет изобретевия Устройство для решения дифференциального уравнения первого порядка, содержащее ин.3 95857 тегрирующий усилитель, выход которого через инвертор соединен со входом операционного усилителя, отличающееся тем, что, с целъю расширения класса решаемых задач, оно содержит второй интегрируюш,ий усилитель, выход которого подключен ко входу инвертора, схемы сравнения, триггеры, элементы «И и преобразователь «код-аналог, причем выход инвертора соединен со входами первой и в горой схем сравнения, выходы которых соединены со входами первого триггера, а входы второго триггера соединены со второй и третьей схемами сравнения, выходы первого триггера соединены соответственно через первый элемент «И со входом первого интегрируюшего усилителя и через второй элемент «И с первым входом второто интегрирующего усилителя, выход которого подключен ко входу третьей схемы сравнения, а выход второго триггера соединен с преобразователем «коданалог, подключенным ко второму элементу «И и через третий элемент «И соединен со вторым входом второго интегрирующего усилителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТОКА В ФАЗЕ АСИНХРОННОГО ЭЛЕКТРОПРИВОДА | 1991 |

|

RU2022442C1 |

| БАКТЕРИЦИДНАЯ СИСТЕМА ДЛЯ ОБРАБОТКИ ВОДЫ | 1994 |

|

RU2072967C1 |

| Функциональный преобразователь | 1978 |

|

SU781838A1 |

| Преобразователь сигнала тензомоста в интервал времени | 1987 |

|

SU1580260A1 |

| Устройство для моделирования электрических машин | 1988 |

|

SU1597886A1 |

| Устройство для управления компенсирующей установкой | 1982 |

|

SU1025001A1 |

| УСТРОЙСТВО ВЫБОРКИ И ХРАНЕНИЯ | 2015 |

|

RU2595487C1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1988 |

|

SU1547063A1 |

| Устройство для моделирования конструкционного трения | 1979 |

|

SU860091A1 |

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1314458A1 |

У С т. „О

Авторы

Даты

1973-01-01—Публикация