1

Изобретение относится к области автоматики, телемеханики и вычислительной техники и может быть использовано, иапри мер, в автоматических регуляторах и измерителях дискретного действия с программным управлеиием, в цифровых вычислительных устройствах, в качестве бесконтактных номеронабирателей для телефонных аппаратов и т. д.

Известно устройство для изменения частоты следования импульсов путем деления стабильной частоты, содержащее несколько счетчиков с цепями связи.

Цель изобретения - осуществление автоматически управляемого нарастающего отсчета серий импульсов и числа импульсов в каждой серии, а также упрощение устройства и повышение его наделиюсти, что особенно заметно должно проявляться при увеличении числа отсчитываемых серий импульсов и числа импульсов в каждой серии.

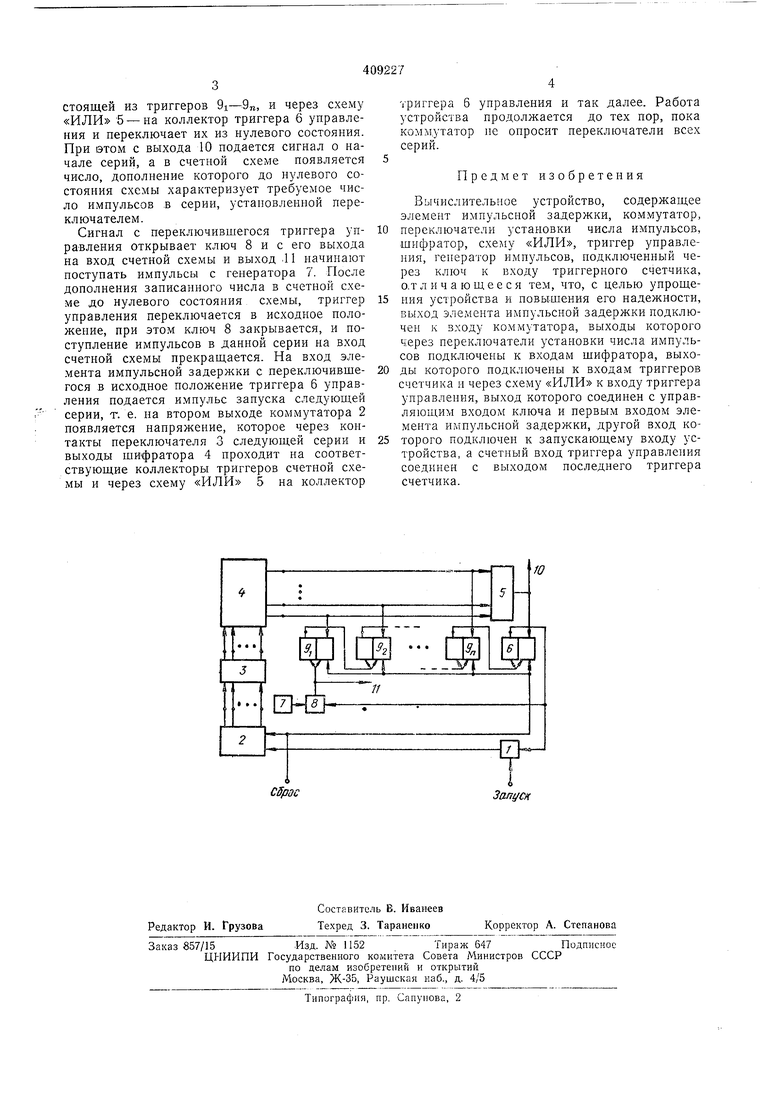

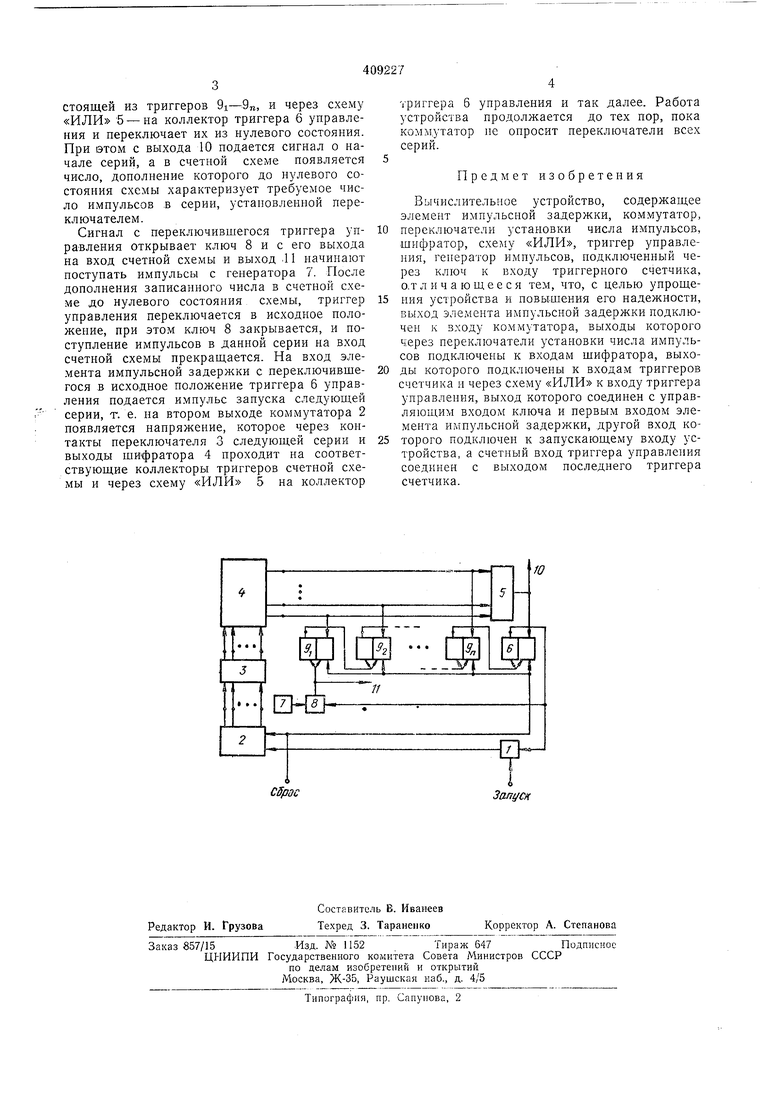

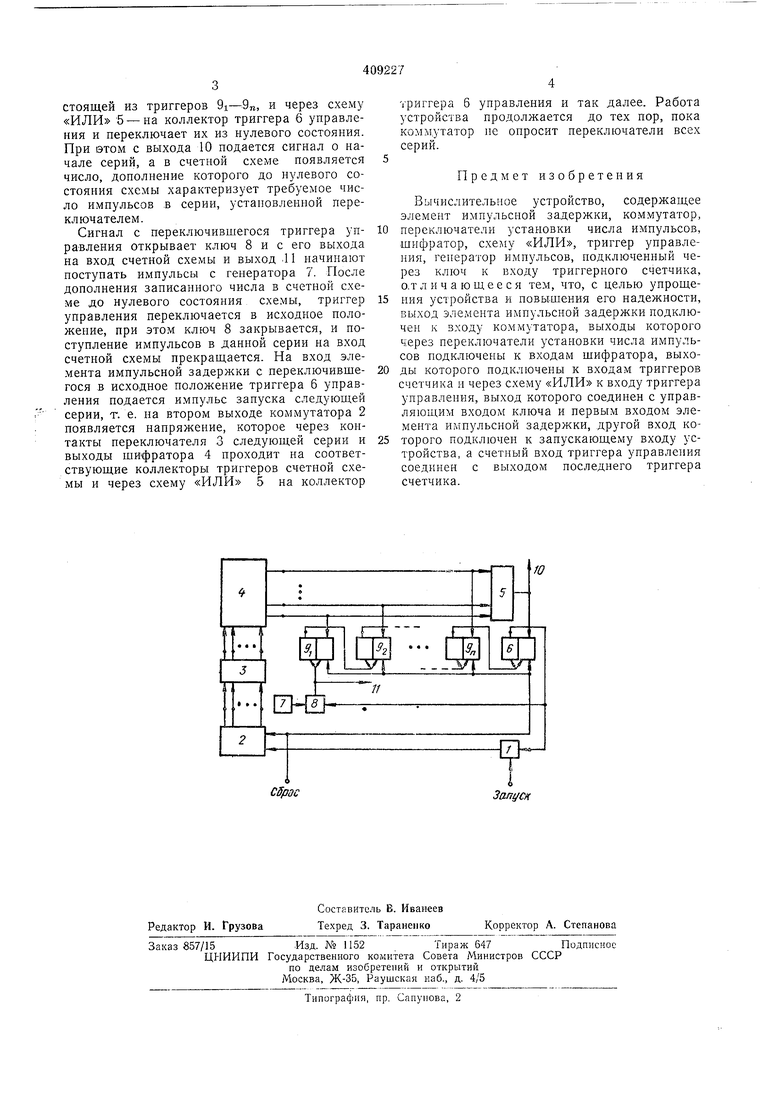

Это достигается применением в устройстве элемента импульсной задержки, выход которого подключен к входу коммутатора. Выходы коммутатора через переключатели установки числа импульсов подсоединены к выходам щифратора, а выходы шифратора - к входам триггеров счетчика и через схему «ИЛИ к входу триггера у1правления. Выход последнего соединен с управляющим входом ключа и первым входом элемента имнульснои задержки, другой вход которого нодключеи к запускающему входу устройства. Счетный вход триггера управления соединен с выходом последнего триггера счетчика. На чертеже показана функциональная схема вычислительного устройства.

Устройство содержит элемент 1 импульсной задержки, коммутатор 2, переключатели 3 установки числа импульсов, щифратор 4, схему

«ИЛИ 5, триггер 6 управления, генератор 7 импульсов, подключенный через ключ 8 к счетной схеме на триггерах 9i-9„.

Выходы коммутатора 2 подсоединены одноименно к входам переключателей установки

числа импульсов. Следовательпо, количество выходов К01ммутатора равно количеству переключателей, количество переключателей - количеству серий импульсов, количество положений каждого переключателя - 1максимальному количеству импульсов в серии, которое, в свою очередь, равно количеству входов шифратора.

При подаче импульса запуска на один из входов Элемента 1 импульсной задержки, первый импульс с его .выхода с задержкой попадает на вход коммутатора 2 и на его первом выходе появляется выходное напряжение. Это напряжение через контакты переключателя 3 и выходы шифратора 4 поступает на соответствующие коллекторы счетной схемы, со

стоящей из триггеров 9i-9„, и через схему «ИЛИ 5 - на коллектор триггера б управления и переключает их из нулевого состояния. При ВТОМ с выхода 10 подается сигнал о начале серий, а в счетной схеме появляется число, дополнение которого до нулевого состояния схемы характеризует требуемое число импульсов .в серии, установленной переключателем.

Сигнал с переключившегося триггера управления открывает ключ 8 и с его выхода на вход счетной схемы и выход .11 начинают поступать импульсы с генератора 7. После дополнения записанного числа в счетной схеме до нулевого состояния схемы, триггер управления переключается в исходное ноложение, при этом ключ 8 закрывается, и поступление импульсов в данной серии на вход счетной схемы прекращается. Па вход элемента импульсной задержки с переключившегося в исходное положение триггера 6 управления подается импульс запуска следующей серии, т. е. на втором выходе коммутатора 2 появляется напряжение, которое через контакты переключателя 3 следующей серии и выходы шифратора 4 проходит на соответствующие коллекторы триггеров счетной схемы и через схему «ИЛИ 5 на коллектор

триггера 6 управления и так далее. Работа устройства продолжается до тех пор, пока коммутатор не опросит переключатели всех серий.

Предмет изобретения

Вычислительное устройство, содержащее элемент импульсной задержки, коммутатор, переключатели установки числа импульсов, шифратор, схему «ИЛИ, триггер управления, генератор импульсов, подключенный через ключ к входу триггерного счетчика, о.т л и ч а ю щее ся тем, что, с целью упрощения устройства и повышения его надежности, выход элемента импульсной задержки подключен к входу коммутатора, выходы которого через переключатели установки числа импульсов подключены к входам шифратора, выходы которого подключены к входам триггеров счетчика и через схему «ИЛИ к входу триггера управления, выход которого соединен с управляющим входом ключа и первым входом элемента импульсной задержки, другой вход которого подключен к запускающему входу устройства, а счетный вход триггера управления соединен с выходом последнего триггера счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА—ВЫВОДА ИНФОРМАЦИИ | 1972 |

|

SU432548A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1615760A1 |

| Устройство для приема и передачи сигналов контроля от датчиков | 1987 |

|

SU1418793A1 |

| Устройство для ввода информации | 1983 |

|

SU1160386A1 |

| Преобразователь импульсной после-дОВАТЕльНОСТи B ОдиНОчНый пРяМО-угОльНый иМпульС | 1979 |

|

SU809533A1 |

| Устройство для счета метража и определения теоретического веса проката | 1975 |

|

SU595741A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1383370A1 |

| Формирователь импульсов | 1985 |

|

SU1283952A1 |

| Автоматический измеритель импульсной мощности СВЧ - радиосигналов | 1989 |

|

SU1704102A1 |

Ю

3ani/Cf(

Авторы

Даты

1973-01-01—Публикация