1

Инвертор относится к области вычислительной техники и предназначен для формирования мощных тактовых импульсов в цифровых вычислительных устройствах, а также для использования в качестве мощного выходного каскада в других импульсных устройствах.

Известен сложный инвертор, содержащий управляющий транзистор, база которого через диодно-резистивную переключающую цепь соединена с входной шиной, последовательно включенные инвертирующий и повторительный транзисторы, шину питания.

Целью изобретения является увеличение нагрузочной способности, быстродействия и снижения рассеиваемой мощности в мощном формирователе импульсов. Это достигается тем, что в ипвертор введены две дополнительные диодно-резистивпые переключающие цепи и последовательно включенные дополнительные инвертирующий и повторительный транзисторы, точка соединения которых подключена к базе основного повторительного транзистора. Дополнительный повторительный транзистор соединен коллектором через резистор с дополнительной шиной питания, а базой с коллектором управляющего транзистора и через резистор с дополнительной шиной питания. Базы основного и дополнительного.-и.ьшерл:и-. рующих транзисторов соединены через Дополнительные днодно-резистивные переключаю1дие цепи с входной шиной.

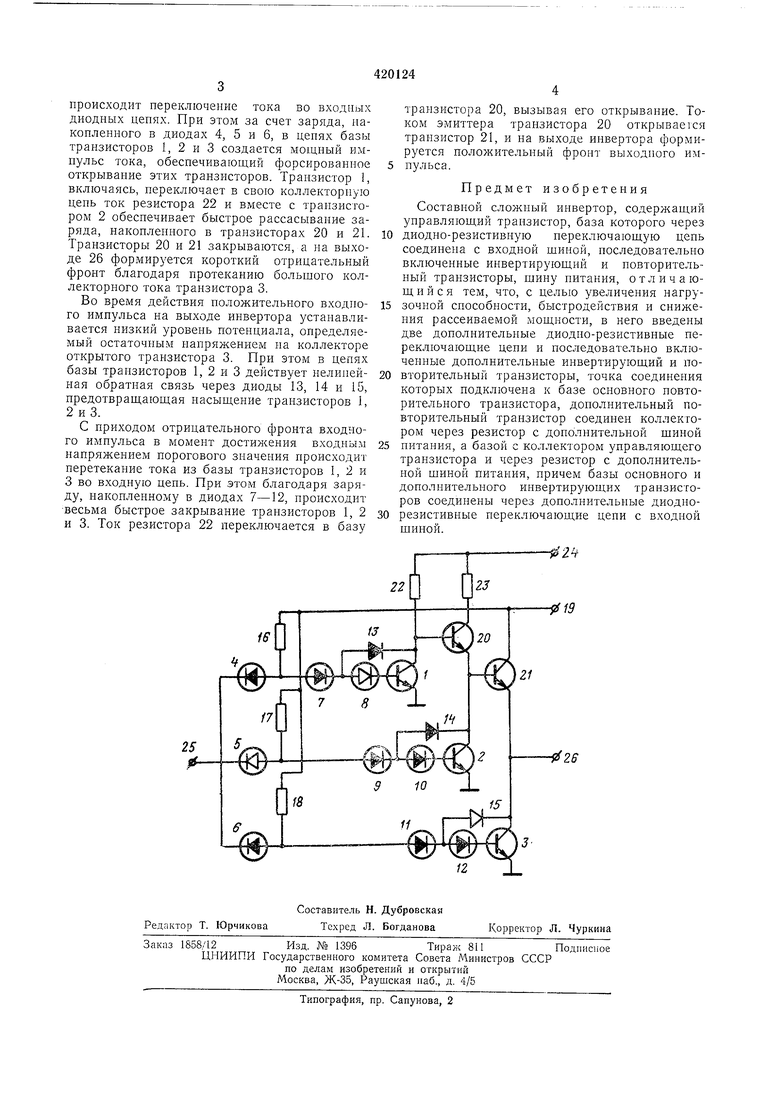

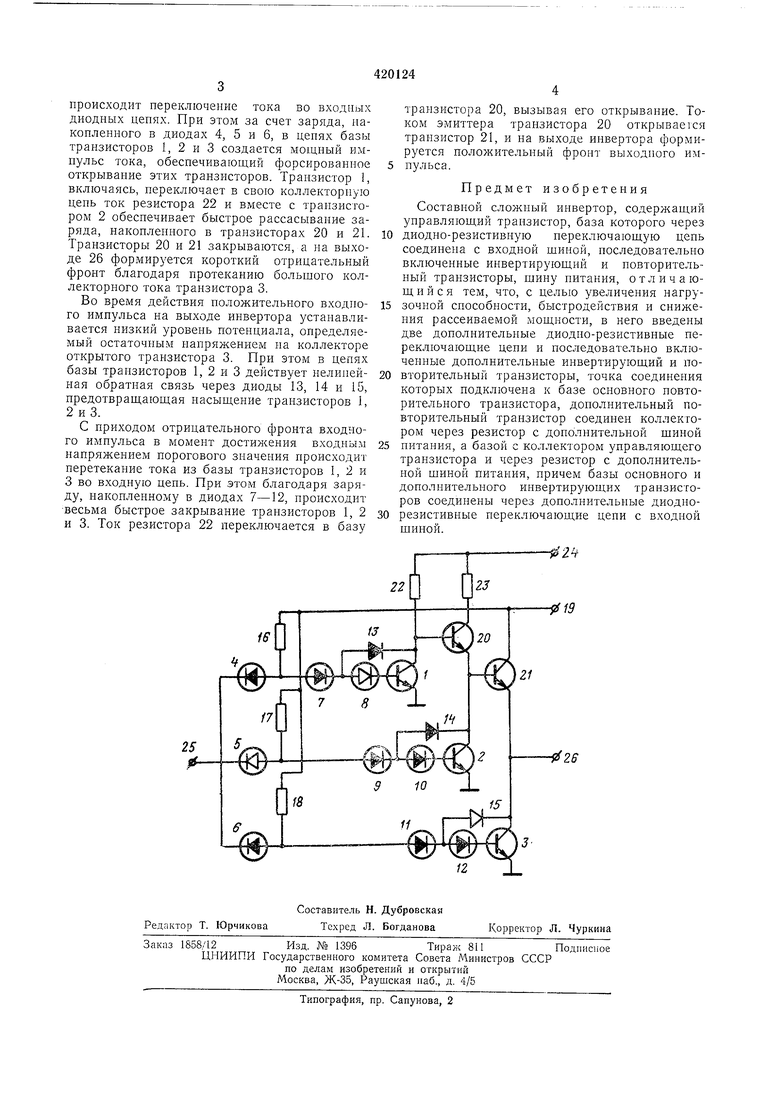

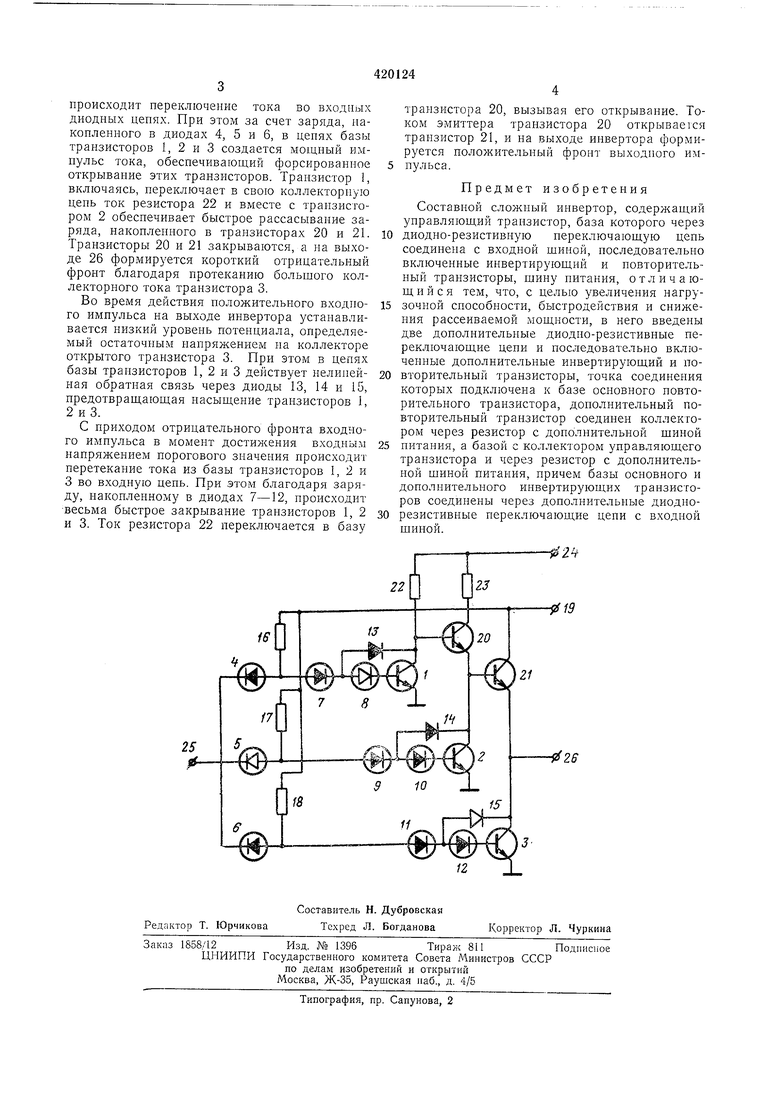

На чертеже изображена принципиальная схема предлагаемого инвертора. Инвертор содержит управляющий 1 и инвертирующие 2 и 3 транзисторы с диодно-резистивными переключаюи ими цепями на входных диодах 4, 5 и 6, диодах 7-12 смещения, диодах 13, 14 и 15 нелинейной обратной связи

и резисторах 16, 17 и 18, подключенных к входу основного источника 19 питания, а также повторительные транзисторы 20 и 21 и резисторы 22 и 23, соединенные с входом вспомогательного источника 24 питания. Коллектор

транзистора 21 нодключен квходу основного источника питания.

При налнчни на входе 25 инвертора низкого уровня напряжения ток от источника 19 через резисторы 16, 17 и 18 течет в диоды 4, 5

и 6, вызывая накопление заряда в них. При этом транзисторы 1, 2 и 3 закрыты, а транзисторы 20 н 21 открыты и насыщены благодаря протеканию тока от источника 24 через резисторы 22 и 23. На выходе 26 инвертора устанавливается высокий уровень .потенциала, близкий по величине к напряжению источника 19 питания.

При поступлении на вход инвертора положн-тельного импульса в момент достижения

входным напряжением порогового зг.ачени;

| название | год | авторы | номер документа |

|---|---|---|---|

| Д-ТРИГГЕР | 1973 |

|

SU389628A1 |

| Двухтактный преобразователь постоянного напряжения | 1982 |

|

SU1056408A1 |

| Динамический Д-триггер | 1982 |

|

SU1019593A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1972 |

|

SU339003A1 |

| ДИНАМИЧЕСКИЙ ИНВЕРТОР | 1969 |

|

SU235817A1 |

| ОДНОВИБРАТОР | 1972 |

|

SU341143A1 |

| Стабилизированный выпрямитель | 1990 |

|

SU1781797A1 |

| РАЗРЯД ДИНАМИЧЕСКОГО РЕГИСТРА СДВИГА | 1972 |

|

SU324711A1 |

| ИМПУЛЬСНЫЙ ДВУХФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И—ИЛИ/И—ИЛИ—НЕ» | 1971 |

|

SU304698A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1972 |

|

SU429517A1 |

Авторы

Даты

1974-03-15—Публикация

1972-04-21—Подача